- 全部

- 默认排序

在PCB设计中,很多工程师会遇见各种问题,其中之一是差分对可以不同层走线吗?答案是可以的,这种设计策略旨在减少电磁干扰和信号损耗,特别是在高速数据传输和射频(RF)应用中。在PCB中,差分信号是一种通过两条相互耦合的传输线(即差分对)来传输

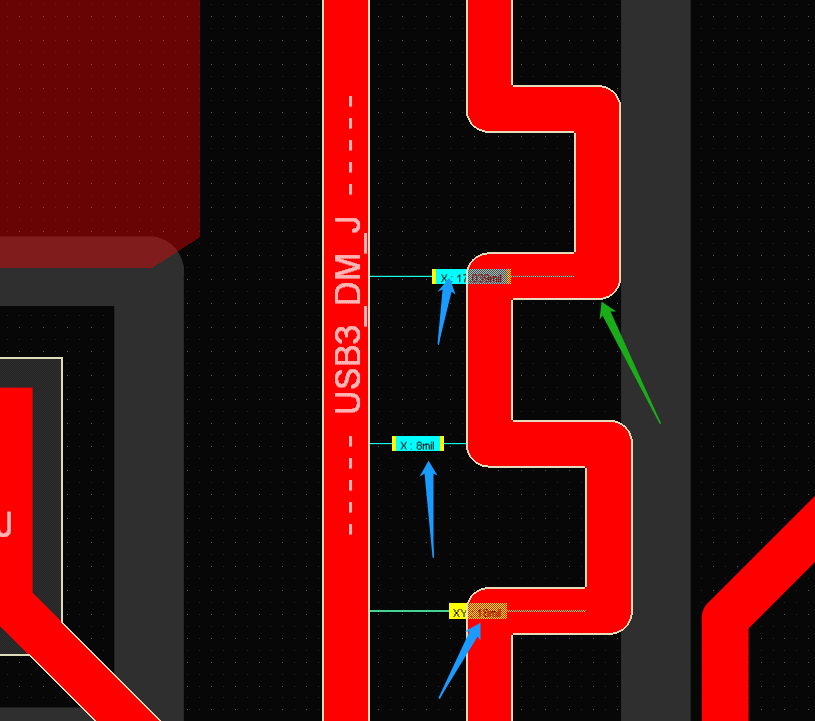

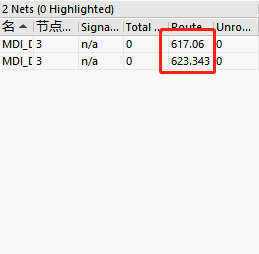

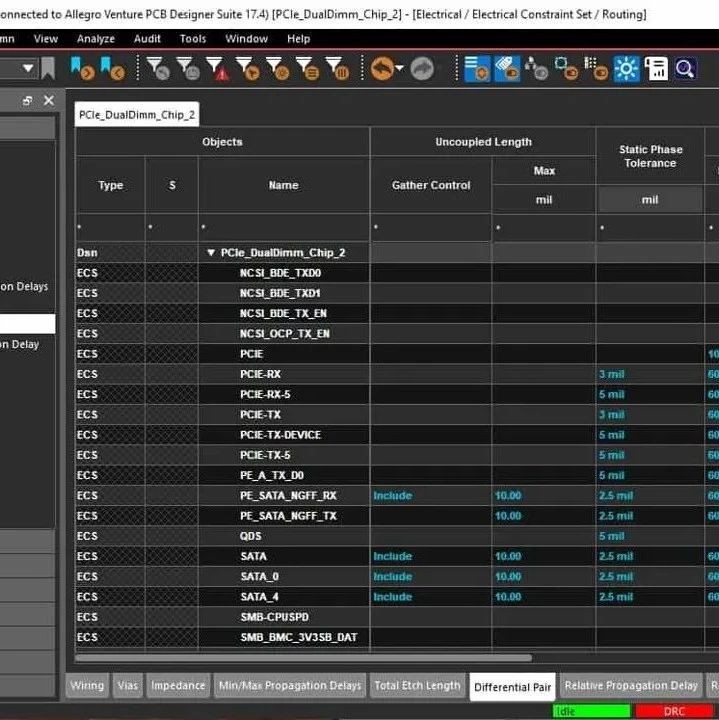

1.1.差分对内等长凸起高度不能超过线距的两倍蛇形尽量不要直角,建议钝角,后期自己优化一下2.存在开路3.ESD器件要靠近管脚摆放,线宽不满足载流,后期自己加粗一下高速信号尽量有完整的参考平面,尽量少打孔,建议增加层处理USB需要进行对内等

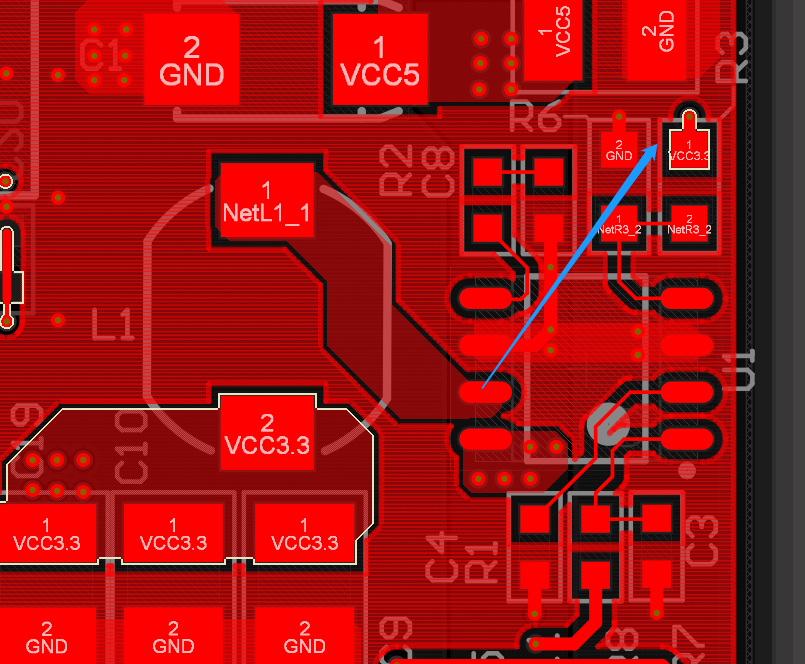

cc1 cc2要加粗这组差分对内不等长这里这么走2.0也是一样的以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?s

反馈信号需要走线连接,并加粗处理2.模拟信号需要包地,走线加粗到12mil3.跨接器件旁边要多打过孔,间距最少2mm,有器件的地方可以不满足4.网口需要添加差分对按照差分间距走线,对内等长误差5mil5.存在间距报错,太近,后期容易造成短路

差分对内等长误差大于5mil两个地间距除跨接器件处外要大于1.5mm时钟需要包地过孔盘粘一起了调整一下以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.ta

随着无线通信技术高速发展,越来越多电子工程师开始接到关于以太网接口的项目设计。想设计以太网接口,确保高效、稳定的数据传输是首要任务,那么如何做?1、差分对布局以太网信号(如RJ45接口中的TX+、TX-、RX+、RX-等)需以差分对形式紧密

在通信系统中,相比单端电路,许多工程师会更加乐意差分电路,因为差分电路有更高的线性度、抗共模干扰信号性能等,当然差分电路并非没有缺点,所以可以通过改善差分滤波器来降低其缺点影响。1、成对差分走线的长度须相同2、差分对内的走线布线须彼此靠近3

本文要点PCB 差分对的基础知识。差分对布线指南,实现更好的布线设计。高效利用 PCB 设计工具。“众人拾柴火焰高” ——资源整合通常会带来更好的结果。毕竟 “三个臭皮匠,顶个诸葛亮”,在电子领域也是如此:较之单一的走线,差分对布线更受青睐。不过,差分对布线可能没那么容易,因为它们必须遵循特定的规则

扫码关注

扫码关注