- 全部

- 默认排序

功率模块Ⅰ—— 绝缘衬底

昨天我们开篇了功率模块,从功率模块的基本分层结构了解了除了半导体芯片之外的几大配置,今天我们来聊聊其中的绝缘衬底,一般会被叫作陶瓷基板,因为这种材料使用的最多,当然还有其他一些适合作为绝缘衬底的材料......绝缘衬底主要是作为半导体芯片的底座,同时会在绝缘衬底上沉积导电材料、绝缘材料和阻性材料,还

功率模块Ⅲ ——底板

前面我们聊了功率模块的绝缘衬底以及其表面金属化的那些事,希望对你们来说有些作用。今天我们继续来聊聊最底层的那块——功率模块的底板......底板作为绝缘沉底的机械支撑,一是吸收功率器件内部产生的热量,二来要将热量传递出去,必须具有较高的热导率才能有效地传递热量。并且需要具有较低的表面粗糙度,能与绝缘

随着科技时代高速发展,5G、物联网、人工智能等新兴技术发展层出不穷,逐渐成为主流,极大地推动了电子设计事业蓬勃发展,导致现在的电子工程师是“就业广、薪资高、需求多,前景好”,因此很多人想要走上电子之旅,那么第一步是先挑选适合的大学,今天我们

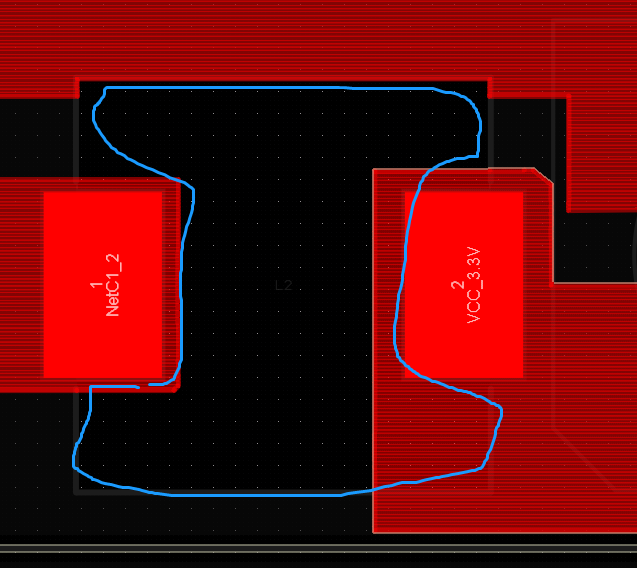

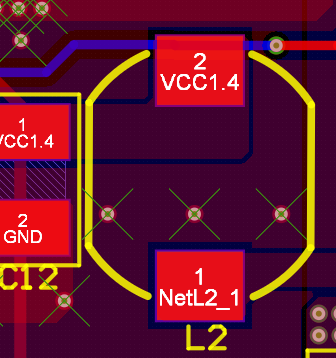

电感所在层的内部需要挖空处理2.走线注意要连接好,不要有stub线头,后期自己优化一下注意焊盘里面不要存在多余的线头3.散热过孔需要开窗处理,其他过孔建议盖油4.铜皮尽量不要用直角,尽量钝角,后期自己优化一下以上评审报告来源于凡亿教育90天

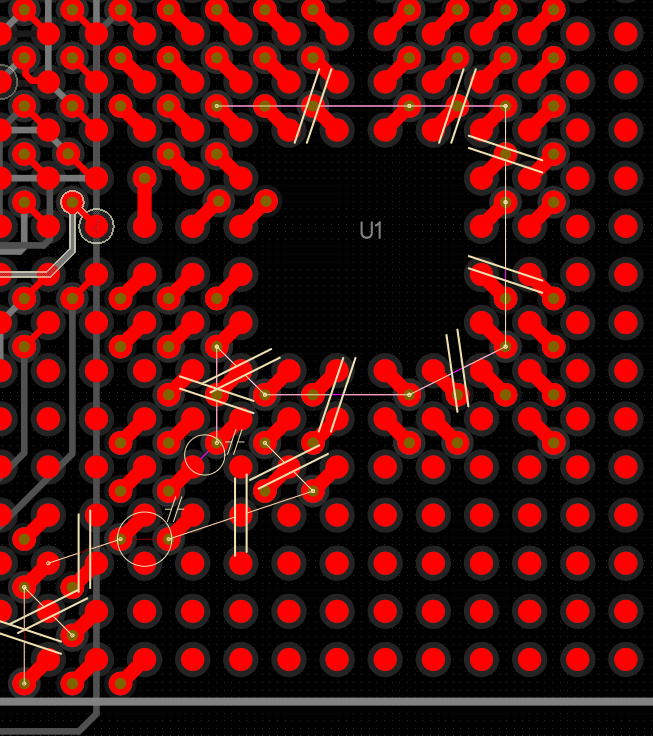

BGA内的电源并未处理,注意要么铺铜要么在电源层进行分割:注意看下U1-U16的地址控制时钟需要组内满足误差 ,还存在报错 ,重新组内等长:U16-U17的地址控制时钟注意对内的等长误差,还存在报错:数据线内也存在等长误差报错:数据线之间满

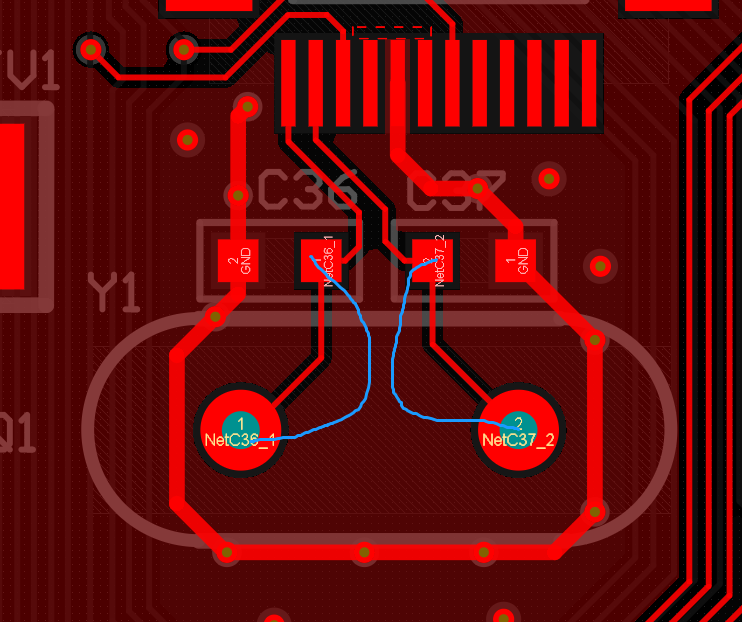

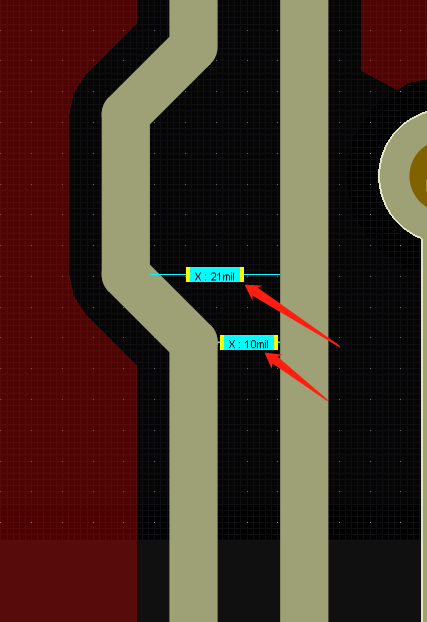

晶振走内差分需要再优化一下2.跨接器件旁边尽量多打地过孔,分割间距最少11.5mm,有器件的地方可以不满足3.网口差分信号需要进行对内等长,误差5mil4.变压器所有层需要挖空处理5.反馈信号要从最后一个输出滤波电容后面取样6.注意数据线之

差分锯齿状等长不鞥超过线距的两倍2.差分换层打孔尽量在旁边打上一对回流地过孔3.232的升压电容尽量走线加粗到15mil4.注意晶振需要包地处理,并在地线上打上地过孔5.注意满足载流大小6.USB差分对内等长误差5mil以上评审报告来源于凡

电感所在层下面要挖空跨接器件旁边尽量多打地过孔,分割间距最少1.5mm,有器件的地方可以不满足差分要对内等长误差不超过5mil485这里应该在电阻这里打孔换层回来。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班

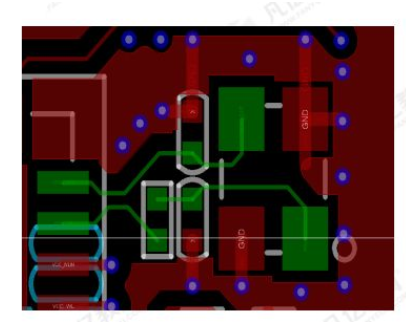

1、模块整体布局时,WIFI模组要尽量远离DDR、HDMI、USB、LCD电路以及喇叭等易干扰模块或连接座;2、晶体电路布局需要优先考虑,布局时应与芯片在同一层并尽量靠近放置以避免打过孔,晶体走线尽可能的短,远离干扰源,尽量天线区域;晶体以

在PCB设计和制造过程中。工程师可能会遇见甩铜现象,也叫做“铜剥离”或“铜剥落”,这些是指在PCB的铜箔层与基板之间出现剥离或分离的情况。而PCB甩铜会导致PCB可靠性大降,甚至损坏,所以必须要了解PCB甩铜的原因及解决方法。1、PCB为什

扫码关注

扫码关注