- 全部

- 默认排序

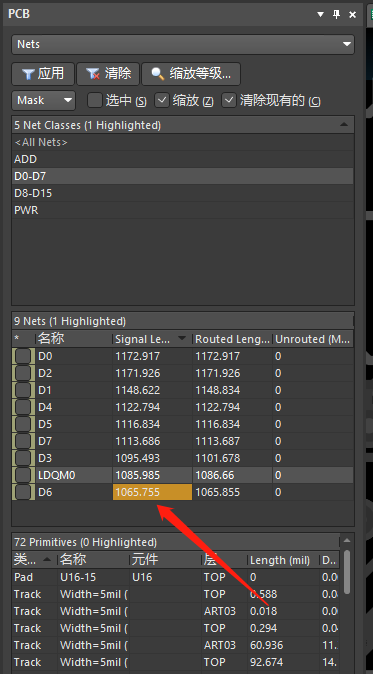

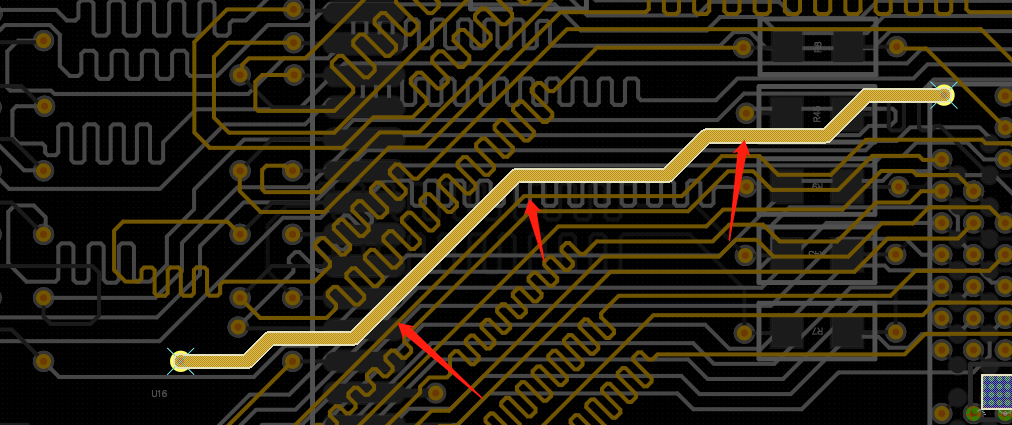

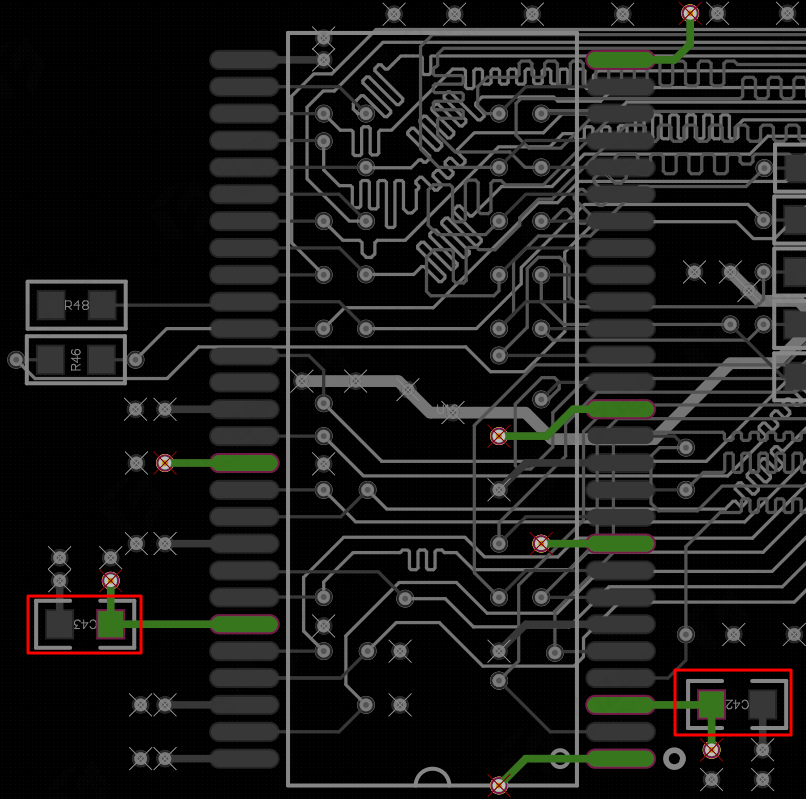

数据线等长存在误差报错2.数据线与地址线之间的分割线上要打地过孔,建议150mil一个3.这几个信号也要加入地址线的类里面进行等长(就是片选,读写,行选,列选)4.注意器件摆放不要干涉5.地网络应该就近打孔,与第二层的地平面相连电源网络也同

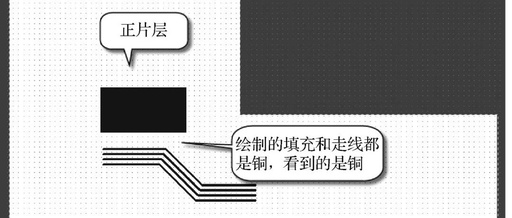

1、层叠的定义及添加对高速多层板来说,默认的两层设计无法满足布线信号质量及走线密度要求,这个时候需要对PCB层叠进行添加,以满足设计的要求。2、正片层与负片层正片层就是平常用于走线的信号层(直观上看到的地方就是铜线),可以用“线”“铜皮”等进行大块铺铜与填充操作,如图8-32所示。图8-32 正片

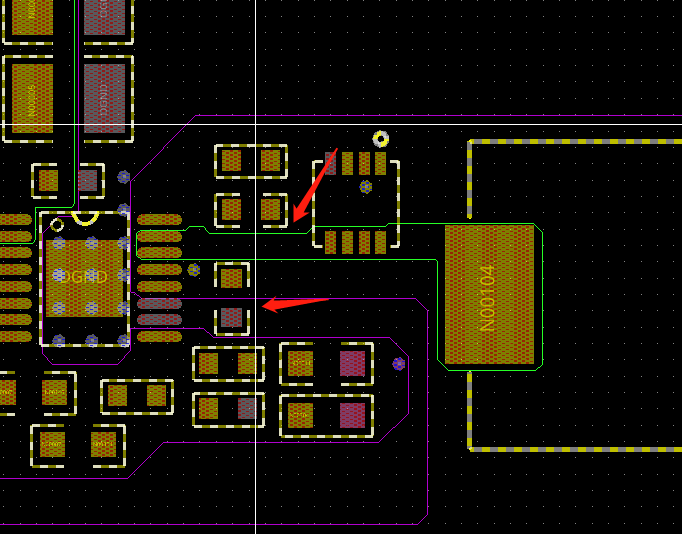

数据线与地址线之间的分割线上需要打地过孔,建议150mil一个第4层数据线和地址线之间也需要添加一根地线分开2.等长存在误差报错3.有器件连接的网络要创建Xsignals进行等长4.注意电源需要再电源层处理一下,铺铜进行连接5.注意器件不要

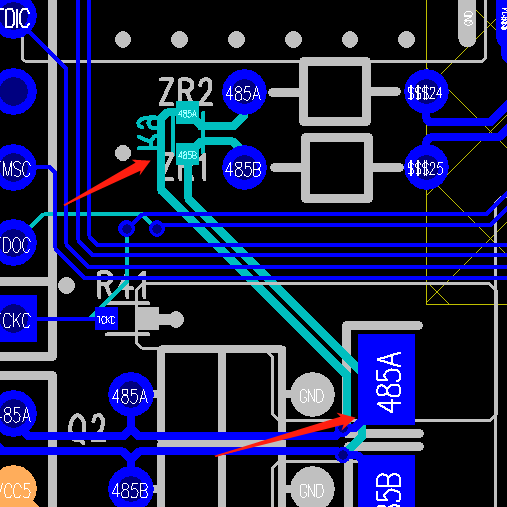

1.485的内差分需要再优化一下2. 模拟信号下面尽量不要穿别的信号线,后期自己换一下走线路径3. 电容尽量靠近管脚放置,一个管脚一个4. 跨接器件旁边尽量多打地过孔,分割间距最少1mm5. 网口除差分信号外其他的信号都需要加粗到20mil

1.电源滤波电容尽量靠近管脚摆放均匀放置,尽量一个电源焊盘放一个电容2.器件摆放干涉3.地址线分组错误,缺少部分信号4.信号线布线造成闭合回路。5.顶层低层没有铺铜,导致地焊盘没有连接过孔。6.时钟没有和地址线等长以上评审报告来源于凡亿教育

1.存在飞线没有连接2.过孔没有添加网络3.包地不完整,外侧也要包地4.差分换层旁边需要打两个地孔,包地尽量保全以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://it

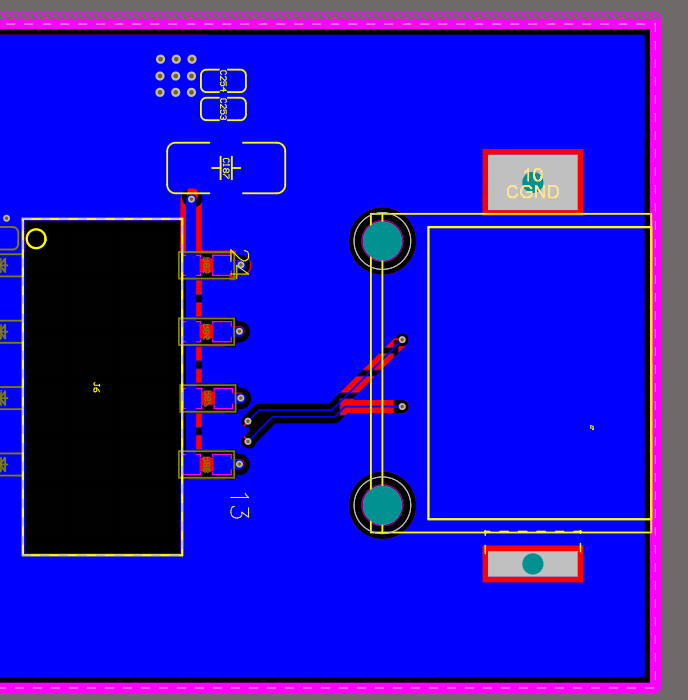

1、外壳地和GND底层铺铜没有分割2、外壳地与GND之间距离需要2mm以上3、跨接区域需要多打孔,外壳地这边也需要多打孔4、多处孤岛铜皮和尖岬铜皮5、差分布线不耦合6、差分换层需要旁边打过孔7、多余过孔没有删除8、电源走线需要加粗走线9、焊

扇孔:PCB设计中的一个术语,这个是一个动作,通俗的理解就是拉线打孔1、过孔的主要作用是用于信号的换层连接,设计中使用过孔必须要在不同层连接信号,不能只连接一层,导致其产生STUB。散热过孔除外。2、同一设计中选用的过孔数量不宜过多,一般不

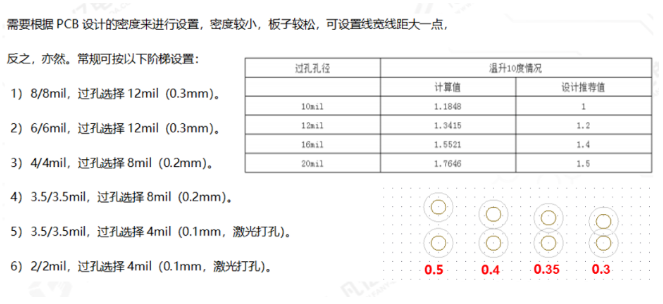

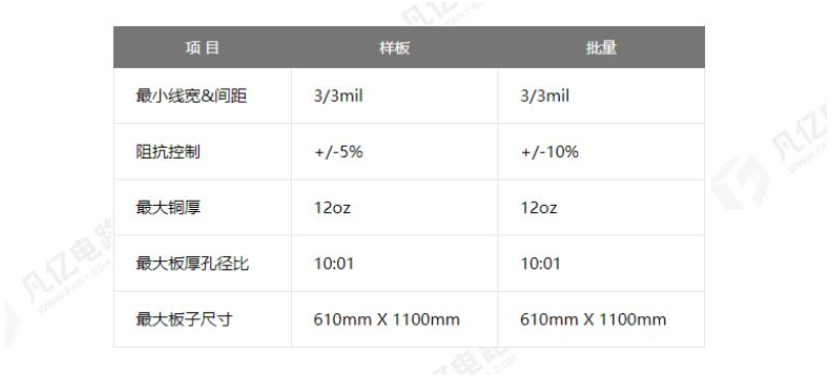

一、关于PCB布线线宽1、布线首先应满足工厂加工能力,首先向客户确认生产厂家,确认其生产能力,如图1所示。如客户无要求,线宽参考阻抗设计模板。图1 PCB板厂线宽要求2、阻抗模板,根据客户提供的板厚及层数要求,选择合适阻抗模型,布线线宽按阻

配置电阻电容可以稍微移动下,留出空间给主干道铺铜:注意电感当前层内部挖空处理:反馈信号没有连接:第二路DCDC的电源跟地都没有处理,都是需要处理的 :以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链

扫码关注

扫码关注