- 全部

- 默认排序

很多人都说咱理科生,咱学电子的人拘谨,枯燥乏味,一点不浪漫。我想说的是,NO!错了,咱们的逻辑思维,对某些事的条理、规划,一旦认真起来做事让你刮目相看!

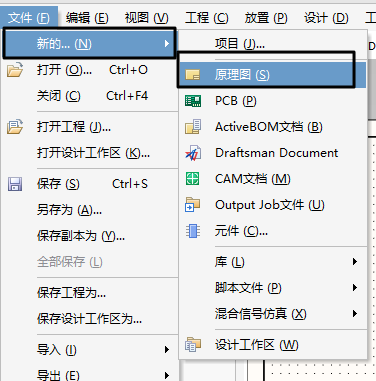

平坦式原理图是一种基础的电路图设计方法,它结构简单,所用的元器件能够在一张电路图上全部表示出来。功能模块是不能进行重复调用的,基本上每一页就是一个功能模块,不同页之间的网络用Offsheet连接,不同的页面都属于同一层次,相当于在一个电路图文件夹中,绘制平坦式原理图的方法和新建原理图方法一致

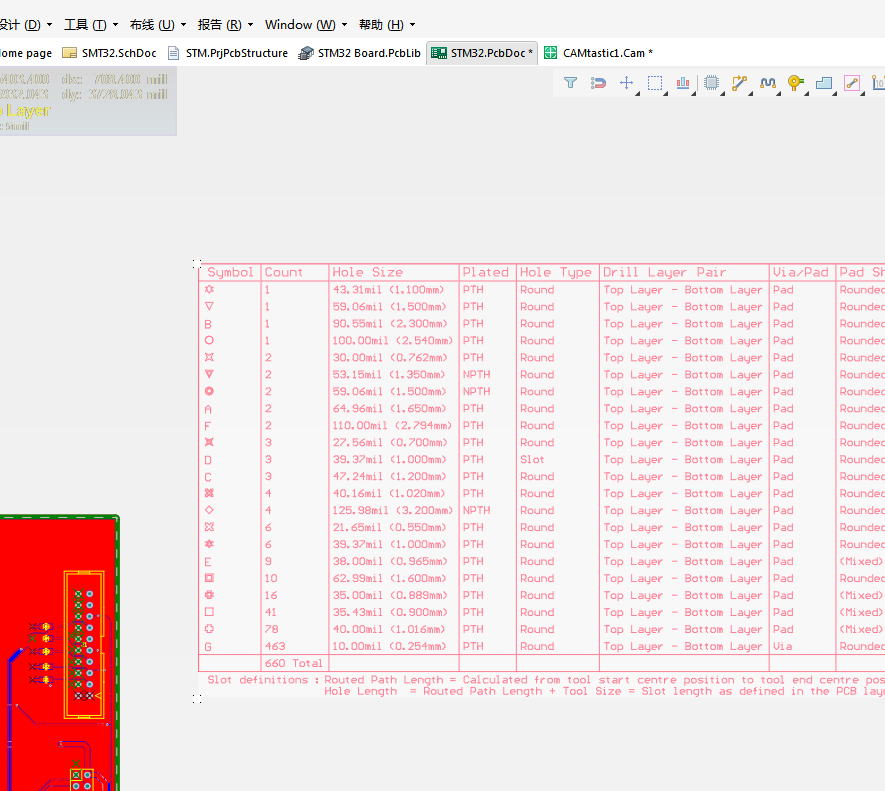

AD20在导出Gerber的时候,Dirll Drawing层的“.legend”出现Legend is not interpreted until output (即使在最终的输出也没有变化)。导致导出Gerber时并没有对应的显示标识。这个问题在高版本中最常见,通常是在放置钻孔表时,对应的选项没有进行设置。

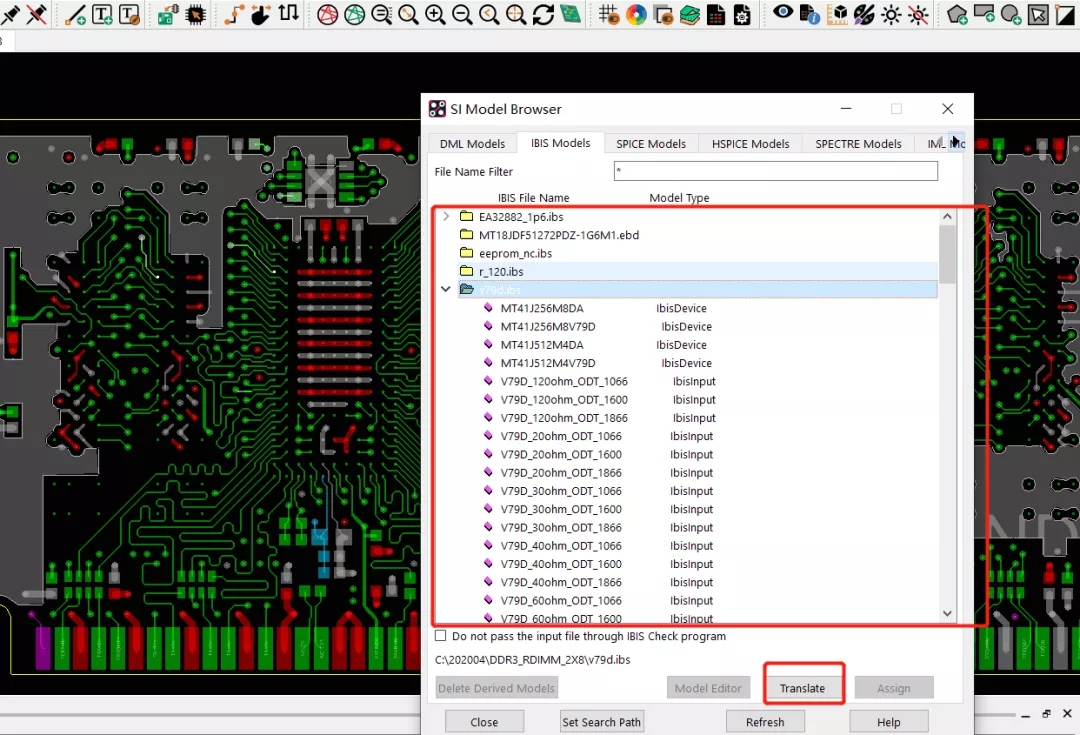

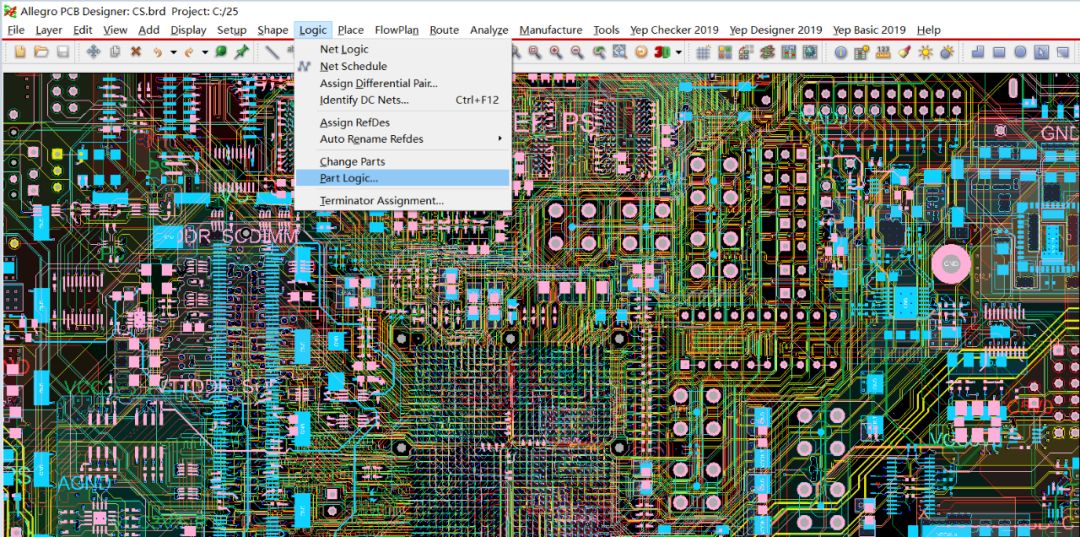

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

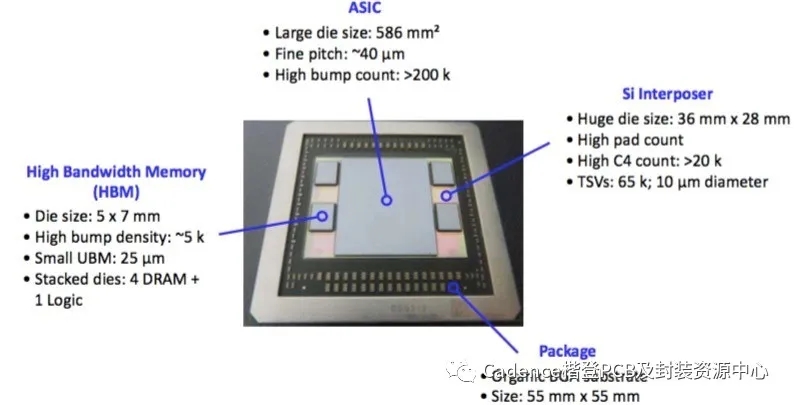

50多年来,半导体行业一直受益于摩尔定律。但是如今,半导体等比例缩小的时代已经结束。摩尔定律主要是作为一条经济法而存在——即集成电路上可容纳的晶体管数量,约每隔几年便会增加一倍。当然,是技术的发展使之成为现实;直到几年前,这一定律依然适用。高层次的经济主张是:每一代工艺将同一领域的晶体管数量增加一倍,成本仅增加15%,从而为每个晶体管节省35%的成本。但是因为当今的工艺愈发复杂,加之建造一个工厂的资本投入非常大(每台EUV步进机将耗资1亿美元),导致每一代晶体管都更加昂贵。因此我们发展出一个从7

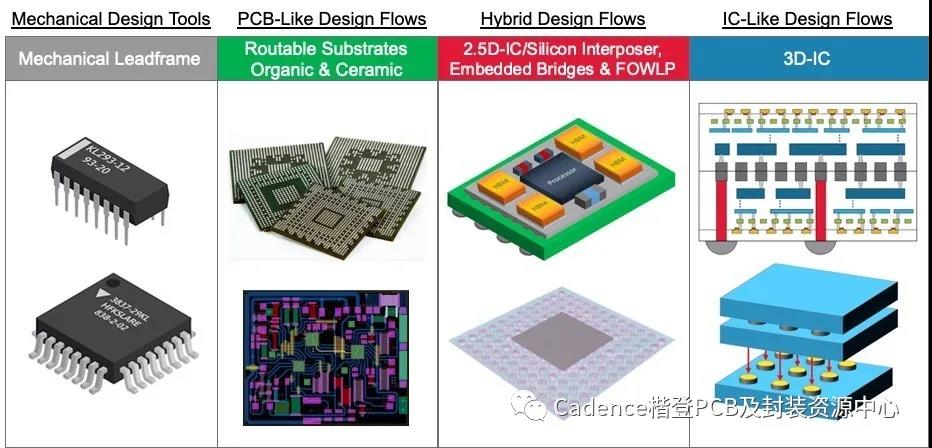

封装设计有许多处理方法: 采用以机械引线框设计封装本身 采用可布线的有机和陶瓷基板设计封装,这是一种PCB风格的设计流程 设计2.5D硅中介层、嵌入式桥和扇出型晶圆级封装(FOWLP)的混合设计流程 采用集成电路类设计流程设计具有硅穿孔(通常)的3D集成电路

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

扫码关注

扫码关注