- 全部

- 默认排序

在高速数字电路设计中,过孔的寄生电感问题是电子工程师经常面对的问题之一,寄生电感的存在很容易影响电路的性能,甚至引发意想不到的问题,因此必须及时计算电感然后解决问题,那么如何计算首先在计算寄生电感问题之前,必须先了解寄生电感到底是什么?简单

寄生电感怎么来的

最近在整理电感的内容,忽然就有个问题不明白了:寄生电感怎么来的呢?一段直直的导线怎么也会存在电感,不是只有线圈才能成为电感吗?想到以前看的书,这个寄生电感的存在大家都默认是有的,貌似也没有人怀疑这个东西是真的存在吗(还是只有我没怀疑)?说到芯片,就是引脚寄生电感,走线长点,就是引线电感这些东西,说到

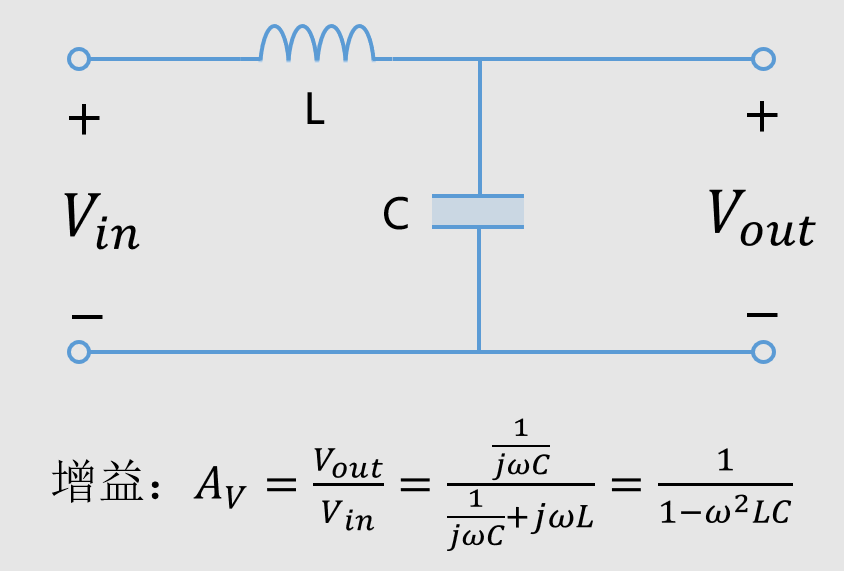

LC串联谐振的意义

我一直有一个感觉:咱们硬件工程师,会遇到各种各样的问题,亦或是各种各样的现象,总会有一个非常简单的解释,一句话或者是几句话,我们见多了这个解释,就自以为明白了,当别人再问起我们的时候,我们也会拿这句话去给别人解释。比如说,寄生电感这个字眼就经常出现,特别是引线电感。我们解释一些问题的时候都是直接套用

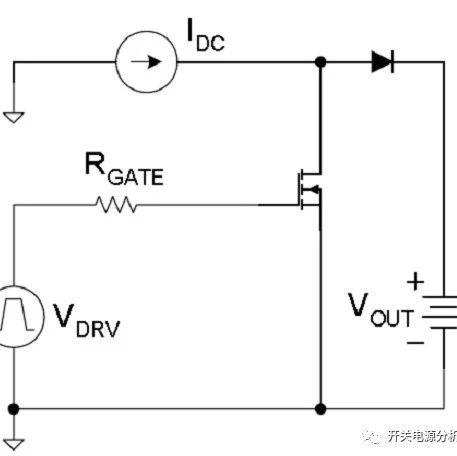

MOS管导通和关断过程

最近一直在说MOS管的知识,就有朋友留言说能具体说一下MOS管的导通和关断过程吗,那我们今天来说一下MOS管的导通和关断具体过程。 为了更好的理解MOS管的导通和关断过程,我们一般会将电路中的寄生电感忽略掉,下面我们以一个最简单的钳位感应开关模型来说明。 对于MOS的导通过程我们可以

MOS管导通和关断过程

最近一直在说MOS管的知识,就有朋友留言说能具体说一下MOS管的导通和关断过程吗,那我们今天来说一下MOS管的导通和关断具体过程。 为了更好的理解MOS管的导通和关断过程,我们一般会将电路中的寄生电感忽略掉,下面我们以一个最简单的钳位感应开关模型来说明。 对于MO

过孔的寄生电感如何计算?

在高速数字电路设计中,过孔作为层间连接的关键元素,其寄生电感对电路性能有不可忽视的影响,而寄生电感的存在会削弱旁路电容的滤波效果,进而影响整个电源系统的稳定性,所以电子工程师必须计算过孔的寄生电感,将影响降到最低。1、过孔的寄生电感计算公式

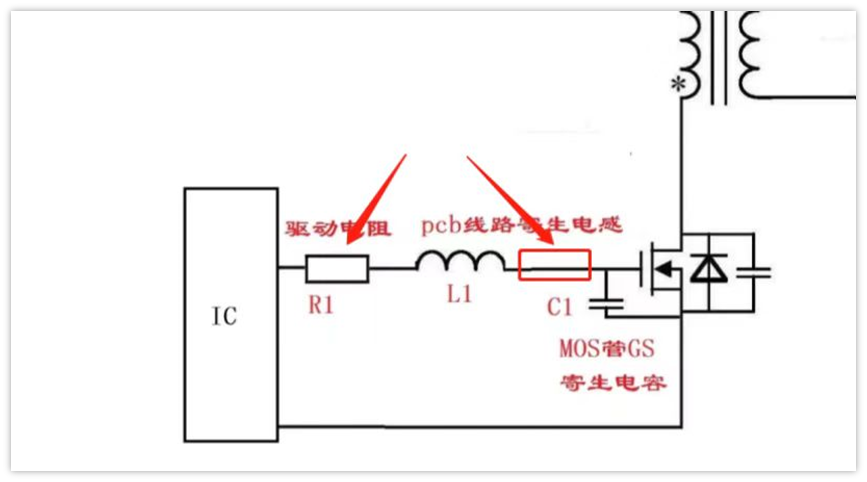

前一段时间有个兄弟问了个问题,把我问住了,问题是这个:如上图,串联的电阻R1到底是放在靠近IC端,还是靠近MOS端?(注意,图中的L1是走线寄生电感,并不是这里放了个电感器件) 我们具体沟通的情况是这样的: 这位兄弟说大部分工程师和IC原厂都是这么做的,但是没有说为什么,我当时也不清楚。但是这个问题

在高速数字电路设计中,过孔(金属氧化孔)的作用是连接各层印制导线,但过孔本身存在的寄生参数,包括寄生电容和寄生电感,会对电路性能产生显著影响,所以必须要严格计算,判断其是否可控。1、寄生电容过孔对地的寄生电容可以通过以下公式计算:C=1.4

穿心电容作为一种特殊类型的电容器,可消除高频干扰噪声,特别是在高频电子设备中,被广泛应用在高频滤波领域。但很多电子小白不太清楚这个特殊电容凭什么能滤波,下面细说下!①寄生电感极小:穿心电容设计使其寄生电感非常小,这降低了旁路阻抗,从而在高频

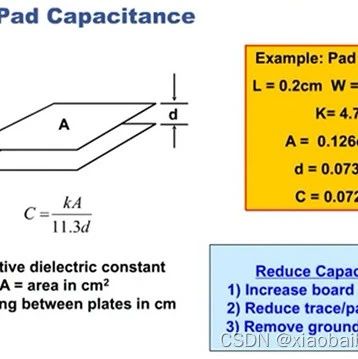

在高速或高频电路板中,PCB中的寄生效应非常明显,这些寄生电容和寄生电感会引起串扰、EMI、信号完整性等问题。在处理高频、高速和混合信号PCB时,需要做一些特殊处理,以减小寄生效应对信号的影响。为了减小寄生电容和电感的影响,我们需要知道它们是怎么产生的,才能对症下药。本节我们先来了解如何计算PCB的

扫码关注

扫码关注