- 全部

- 默认排序

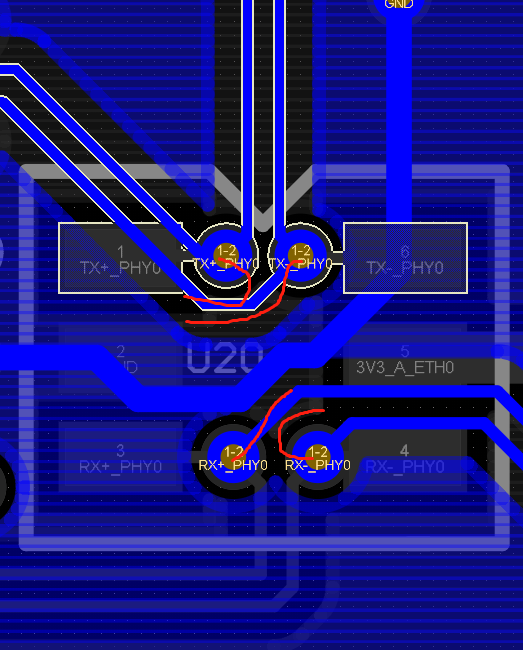

差分走线要注意耦合出线2.时钟信号包地需要再地线上打上地过孔3.差分走线不满足间距规则4.网口差分需要进行对内等长,误差5mil5.小块孤铜后期可以挖掉以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

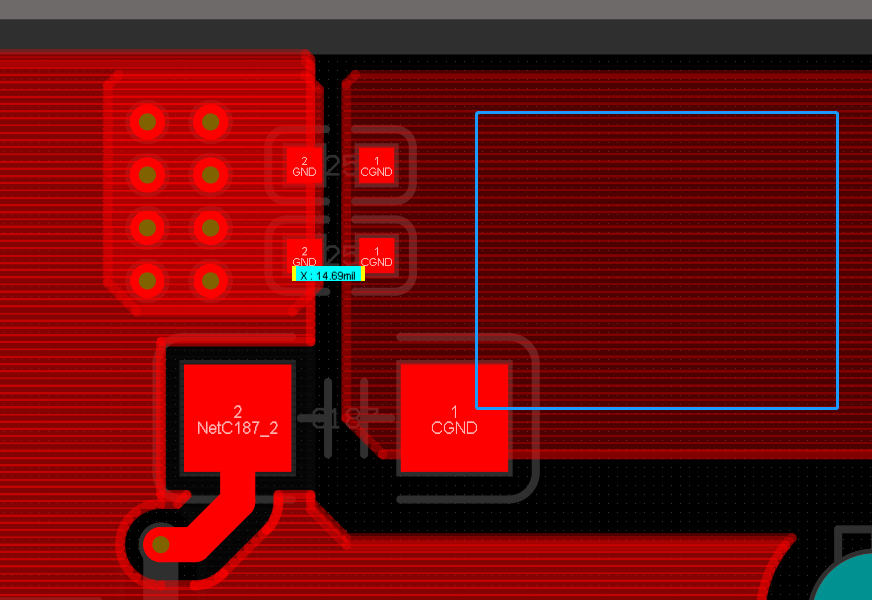

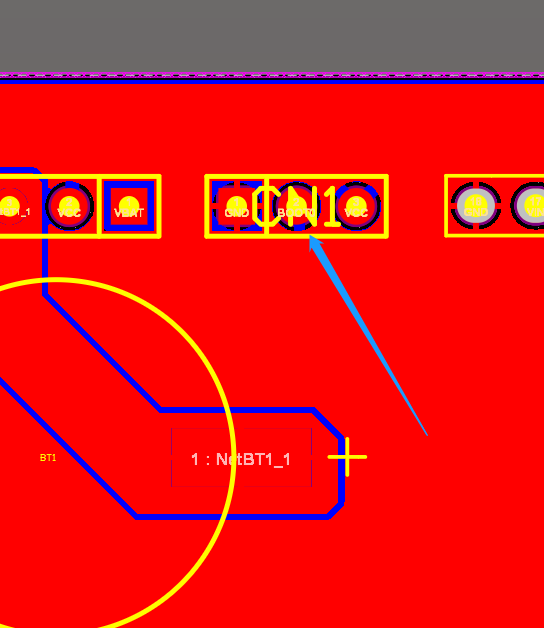

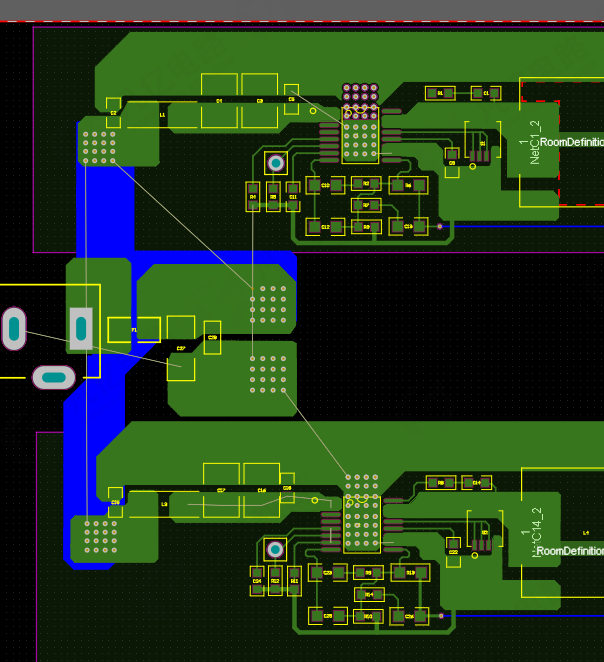

跨接器件旁边要多打地过孔2.注意不要多打孔3.注意过孔不要上焊盘4.注意器件摆放不要干涉以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.co

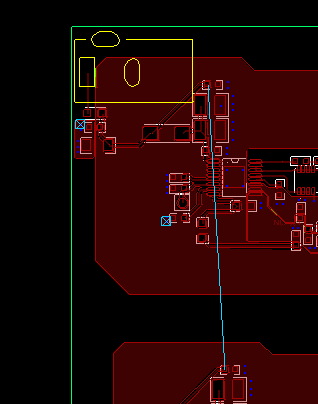

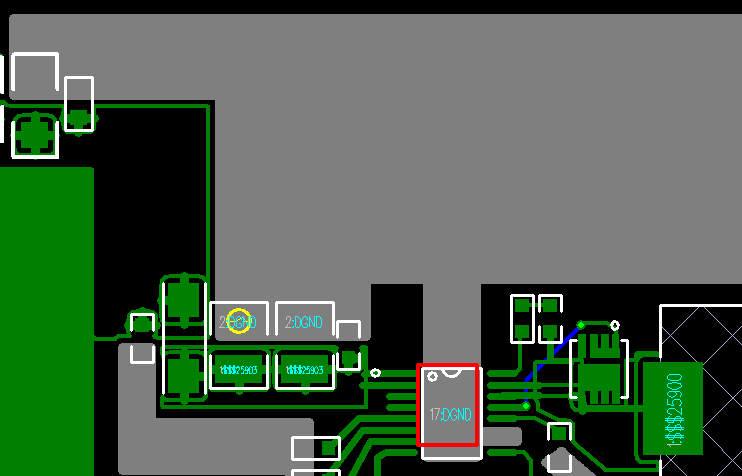

有飞线没连接这里电容应该以容值从大到小的顺序连接反馈也应该从最后一个电容处拉出这里应该铺铜连接dcdc要单点接地这些地方不能打地过孔以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:

器件位号丝印后期设计完成需要调整,不要重叠:注意板上过孔是否盖油,不要开窗:注意看下工程里面原理图是空的:铺铜注意按照左边钝角绘制,不要直角:可以优化。类似的情况自己优化下。注意晶振底部不要走线:建议是PCB板框放在机械层:器件位号都放到器

差分建议包地 已经打了地过孔直接拉线包上就行了:回流地过孔打在差分打孔换层的两侧:注意此处的扇孔,不要吧内层平面割裂了:差分等长GAP需要大于等于3W:注意差分等长误差:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB

设计完之后注意需要整体调整器件位号,不要覆盖在器件上,整齐的排列在器件旁边:这种没处理的自己后期都处理下。过孔建议是盖油处理,不要开窗:此处的20MIL是否满足载流:整板铺的GND铜皮,但是GND网络并未连接上:需要设置铜皮连接属性之后再去

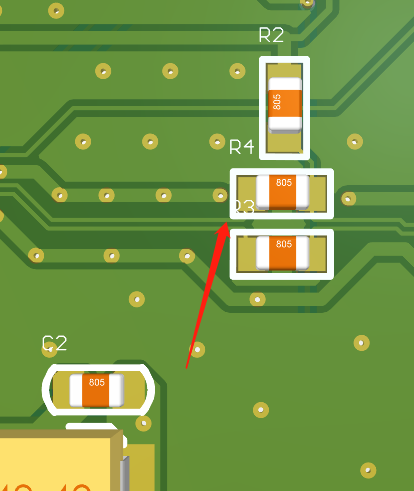

没有打孔,两路dcdc分别在芯片下方打孔连接到底层大gnd铜皮焊盘不要从长边出线,要从短边出线布线不要出现锐角不要任意角度铺铜、布线底层整版铺铜处理器件中心对齐以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程

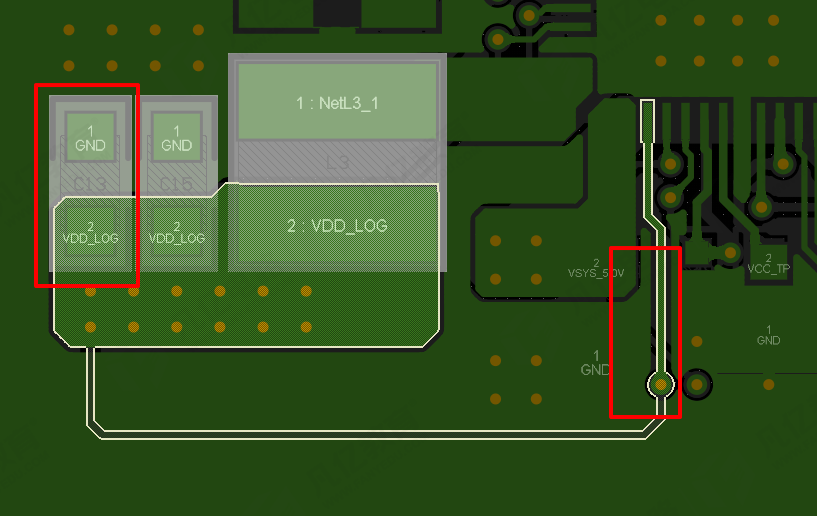

1.器件靠近管脚放置,反馈的电容靠近引脚放置2.铜皮要覆盖到焊盘中间,不能只覆盖焊盘的一角3.过孔要打到最后一个器件后方4.主要电源需要加宽走线保持接入接出线宽一致。5.走线在焊盘内应和焊盘保持宽度一致,出焊盘后在尽快加宽6.存在飞线没有连

1.存在多处飞线没有处理2.过孔没有网络导致铜皮没有连接3.相邻大电感应朝不同方向放置4.走线没有连接到孔5.多处铜皮没有网络6.底层应该整版铺铜7.布线网络不同造成短路和天线报错8.铜皮没有连接到大铜皮造成开路9.铺铜尽量避免直角以上评审

存在开路,后期自己选择铜皮重新铺铜2.反馈线要从最后一个电容后面取样,线宽10mil3.注意电感下面尽量不要放置器件和走线,后期自己调整一下器件位置4.底层需要添加阻焊进行开窗,散热过孔需要开窗处理以上评审报告来源于凡亿教育90天高速PCB

扫码关注

扫码关注