- 全部

- 默认排序

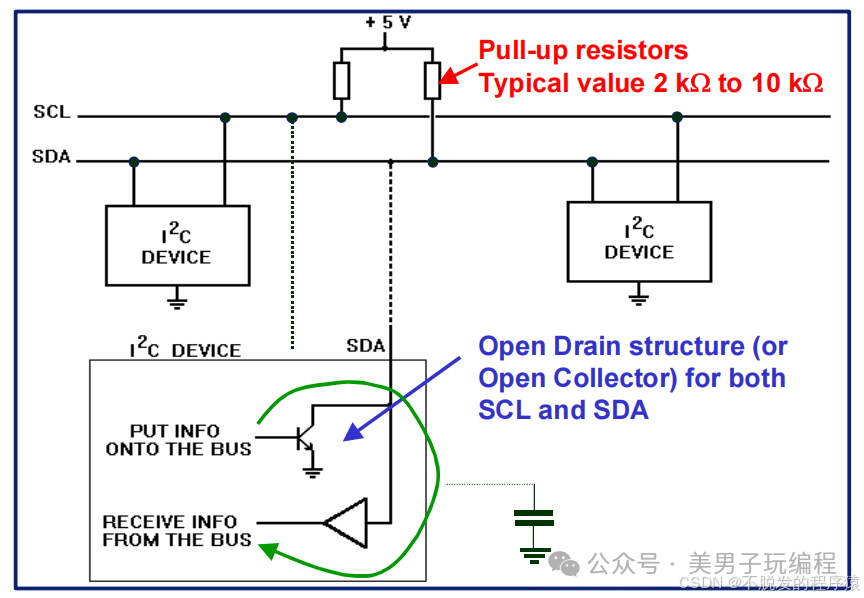

I2C 死锁是指总线被卡住,无法继续通信的情况,通常由从设备意外拉低 SDA 或 SCL 线引起,导致主设备无法发起新的事务。死锁的常见成因包括:噪声或干扰:外部电磁干扰可能导致 SCL 的时钟边沿丢失或 SDA 数据错误。例如,噪声可能使从设备误认为通信仍在进行,从而保持 SDA 低电平。启动时的

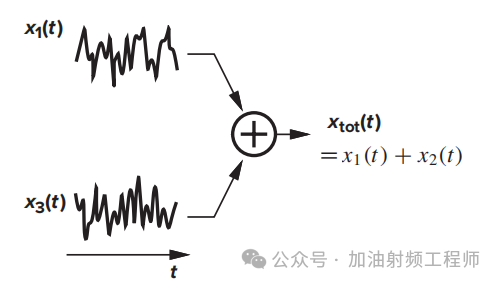

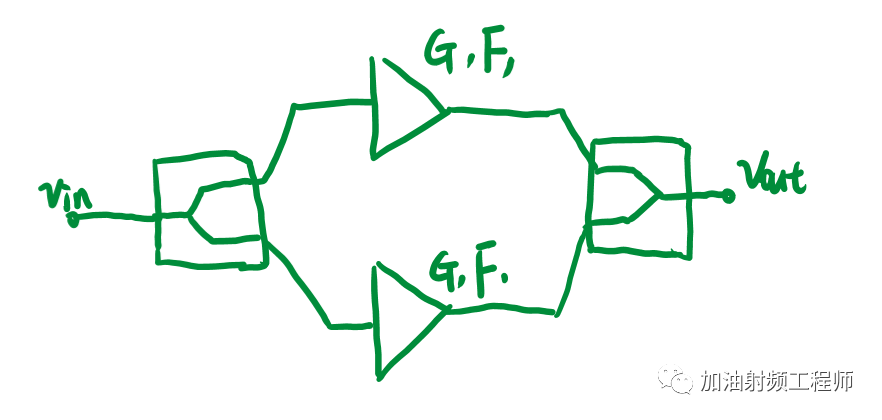

(1)前阵子,发了一篇文章,这种架构的噪声系数,你觉得会是多少?这篇文章是因为号友有相关的提问。文章的留言处,有号友说,那相控阵的话,信噪比,如果有N路的话,信噪比就能好10logN。当时看到这些留言的时候,说实话,是有一点小蒙的。虽然我没有做过相控阵列,但是理智上,觉得号友们说的应该没有问题,要不

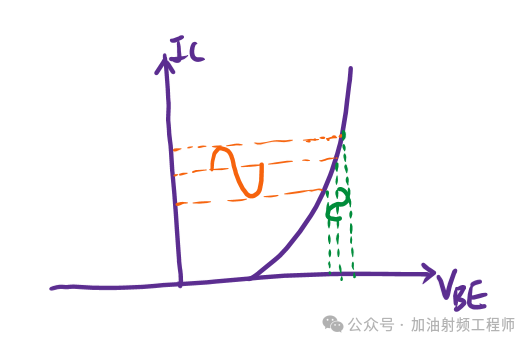

BJT放大器的偏置电路

(1)在低噪声放大器的设计中,可能会花很多时间去考虑把噪声系数设计小,把带宽设计宽,把驻波设计好,但是可能对于偏置电路就没有那么关注。主要可能是因为偏置电路的结构相对固定,而且射频微波放大器的管子,一般都给出了相应静态工作点下面的S参数,选好想用的S参数,选一个偏置电路,计算器件值就可以了。但是,偏

半导体行业经过多年发展,历经无数次升级淘汰,现阶段是石英晶振主导市场,但在部分产品应用,MEMS硅晶振又是不二选择,这两类晶振有什么不同?如何选?1、精度与稳定性石英晶振:短期稳定性(±0.02ppm)和相位噪声(低至150ps)表现优异,

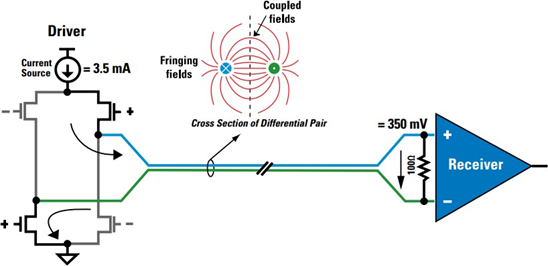

LVDS概述LVDS (Low Voltage Differential Signaling)是一种小振幅差分信号技术,它使用非常低的幅度信号 (250mV~450mv)通过一对平行的 PCB 走线或平衡电缆传输数据。在两条平行的差分信号线上流经的电流及电压振幅相反,噪声信号同时耦合到两条线上,而接

(1)有号友问了一个问题,就是,多输入单输出的系统,噪声系数应该怎么算呢?两路输入,算是同幅同相的,那这个噪声系数该怎么算呢?接触到这个问题后,我在脑子里演算了一下,给的回答是这样的。但是,显然这个回答没有说服力,无仿真,无推导。(2)首先,先用ADS进行一下简单的S参数仿真。用一个信号源 功分器来

开关电源在现代电子设备中扮演着至关重要的角色,但其输出的纹波和噪声电压往往成为影响系统性能的关键因素。虽然这种话题谈的不少了,但还是继续谈,免得部分小伙伴们没看到!一、减少EMI干扰采用金属外壳做屏蔽,降低外界电磁场辐射干扰。在电源输入端增

有没有大神有例子啊?实在搞不明白啊主要就是将一些电路,如低噪声放大器、主放大器等的输入输出端口(这些输入输出的阻抗都是已知的)匹配到50欧姆的示波器接口上还有就是如何进行仿真调整啊?

扫码关注

扫码关注