- 全部

- 默认排序

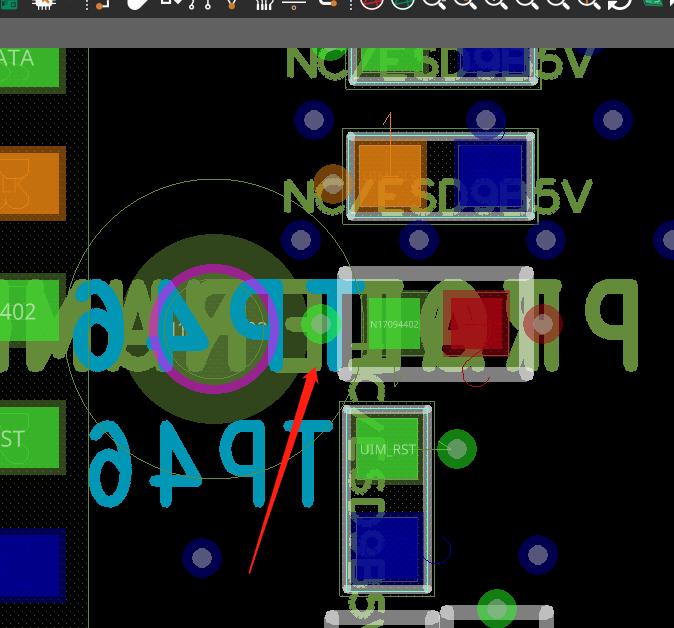

SIM:注意测试点跟器件以及过孔的间距,此处右侧器件可以整体往右边挪动一点:注意铜皮尽量设置动态铜皮,将静态转换下:电感内部挖空掉,在当前层:TF:注意器件之间可以空出点间距留出来扇孔,扇孔不要离焊盘太远:时钟信号包地保全一点,还有 空间可

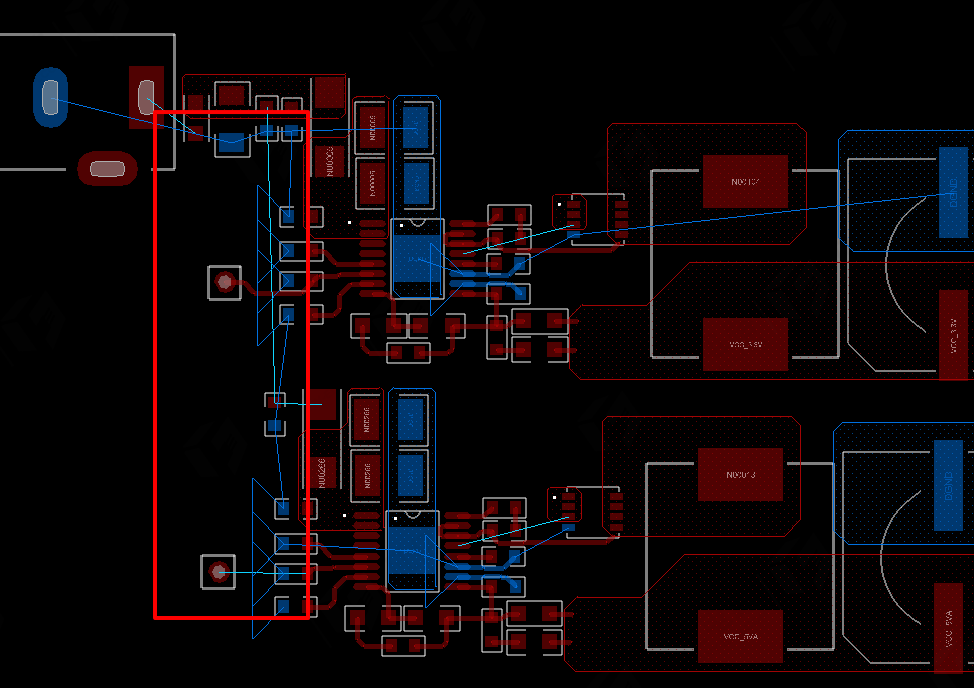

多处飞线没有连接铺铜尽量用动态铜皮电源输出路径铺铜加宽载流,按原理图顺序放置封装反馈路径应连接到电路最后端,走线即可主输出和反馈信号正确示范一路dcdc电路地信号连接通,在芯片下方打孔接地相邻电路电感应朝不同方向垂直放置问题很多,需要认真改

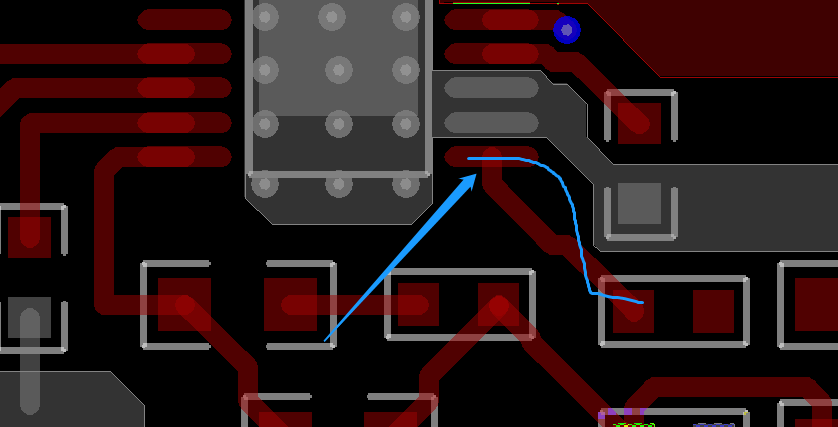

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.走线尽量不要走直角,建议45度3.铺铜注意层的问题,器件在top层,铜皮在bottom层4.模块复用后铜皮变静态铜皮,需要自己调整成动态铜皮,后期自己处理一下5.采用单点接

请教一下,allegro的pcb,导出gerber的时候,需要把板子上的动态铜皮全都转成静态铜皮吗?

扫码关注

扫码关注