- 全部

- 默认排序

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

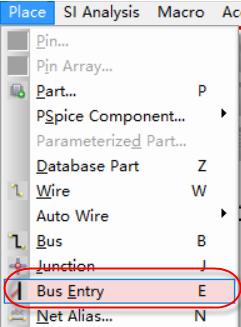

我们创建好总线,给总线命名好以后就需要将创建好的总线与个分支信号连接起来,操作的步骤如下所示:第一步,放置总线入口Bus Entry,点击菜单Place→Bus Entry或者按快捷键E来进行放置,如图3-28所示;第二步,Bus Entry会悬挂在鼠标上,按快捷R可以进行旋转,选择好正确的方向,然后放置到总线上,与总线进行连接,如图3-28所示;第三步,在放置Bus Entry的时候,放置好一个以后,按快捷键F4可以进行快速放置,也可按住Ctrl键,鼠标拖动来进行快速放置,如图3-28所示;&

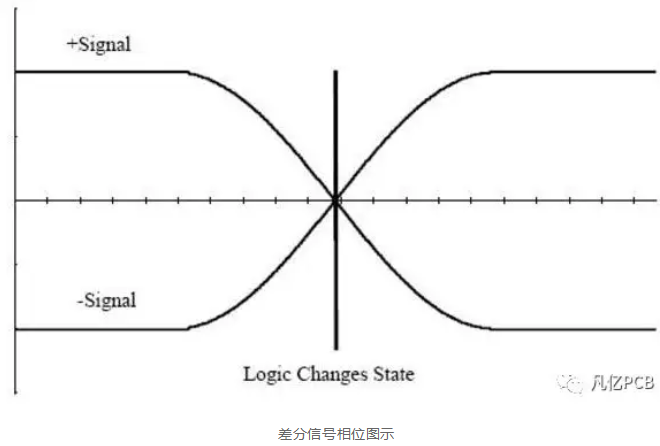

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

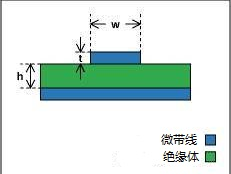

PCB中的信号线分为两种,一种是微带线,一种是带状线。 微带线,是走在表面层(microstrip),附在PCB表面的带状走线,如图1-43所示, 蓝色部分是导体,绿色部分是PCB的绝缘电介质,上面的蓝色小块儿是微带线(microstrip line)。由于microstrip line(微带线)的一面裸露在空气里面,可以向周围形成辐射或受到周围的辐射干扰,而另一面附在PCB的绝缘电介质上,所以它形成的电场一部分分

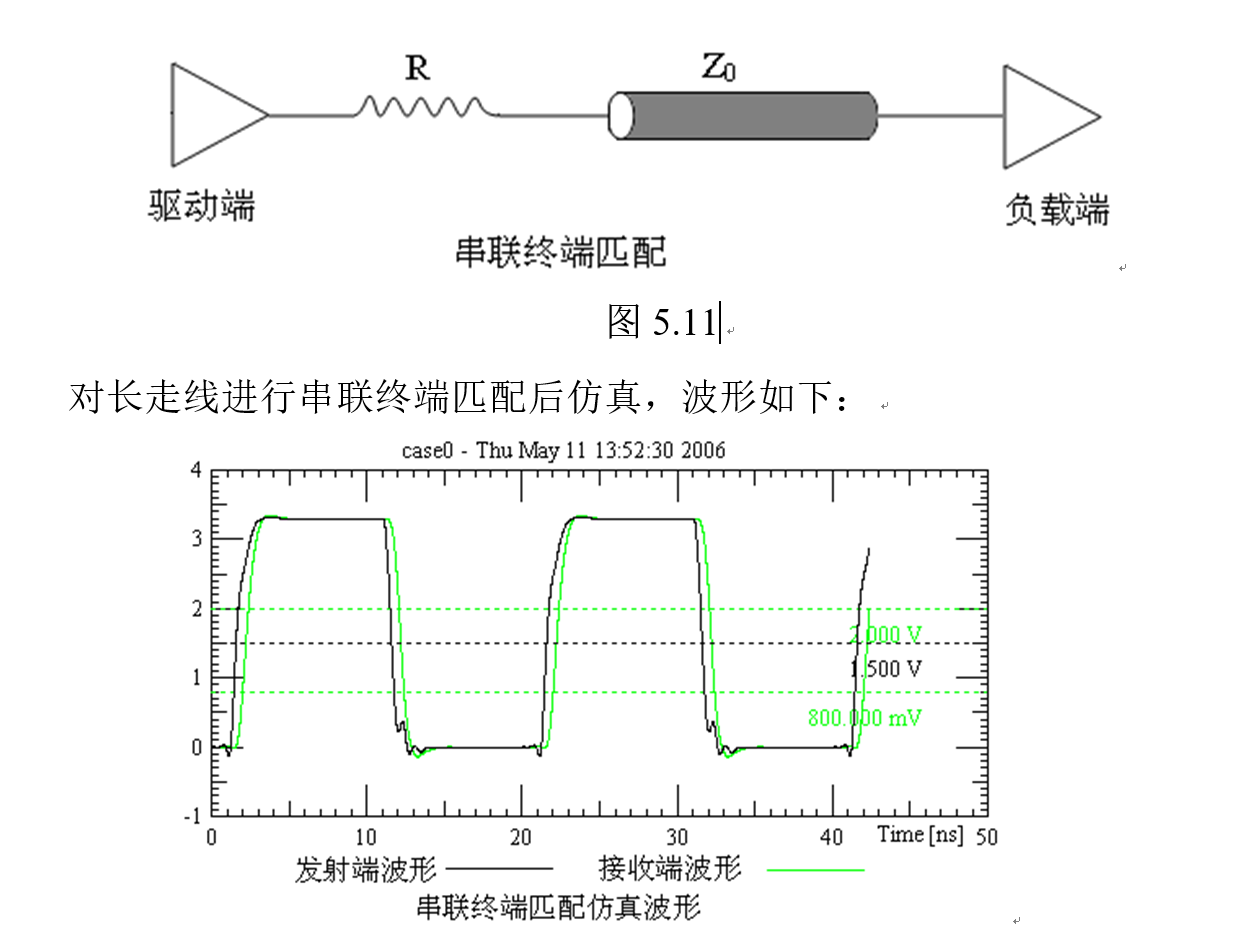

串联终端匹配技术,也称之为后端终端匹配技术,不同于其它类型的终端匹配技术,是源端的终端匹配技术。串联终端匹配技术是在驱动器输出端和信号线之间串联一个电阻。驱动器输出阻抗R0以及电阻R值的和必须同信号线的特征阻抗Z0匹配。对于这种类型的终端匹配技术,由于信号会在传输线、串联匹配电阻以及驱动器的阻抗之间实现信号电压的分配,因而加在信号线上的电压实际只有一半的信号电压。

戴维南终端匹配技术或者也叫做双电阻终端匹配技术,采用两个电阻来实现终端匹配,R1和R2的并联组合要求同信号线的特征阻抗Z0匹配。R1的作用是帮助驱动器更加容易地到达逻辑高状态,这通过从VCC向负载注入电流来实现。与此相类似,R2的作用是帮助驱动器更加容易地到达逻辑低状态,这通过R2向地释放电流来实现。

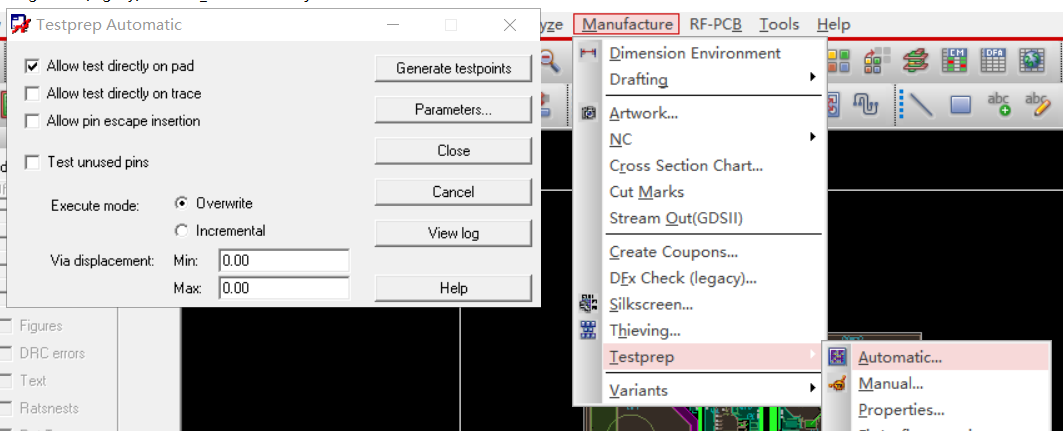

cadence allegro Allow test directly on pad:允许测试点在焊盘上,允许时将自动替换已有的过孔。Allow test directly on trace:允许测试点在信号线上,允许时测试点可以直接在信号线上。Allow pin escape insertion:允许从引脚上自动引出测试点。Test unused pins:无网络引脚添加测试点。

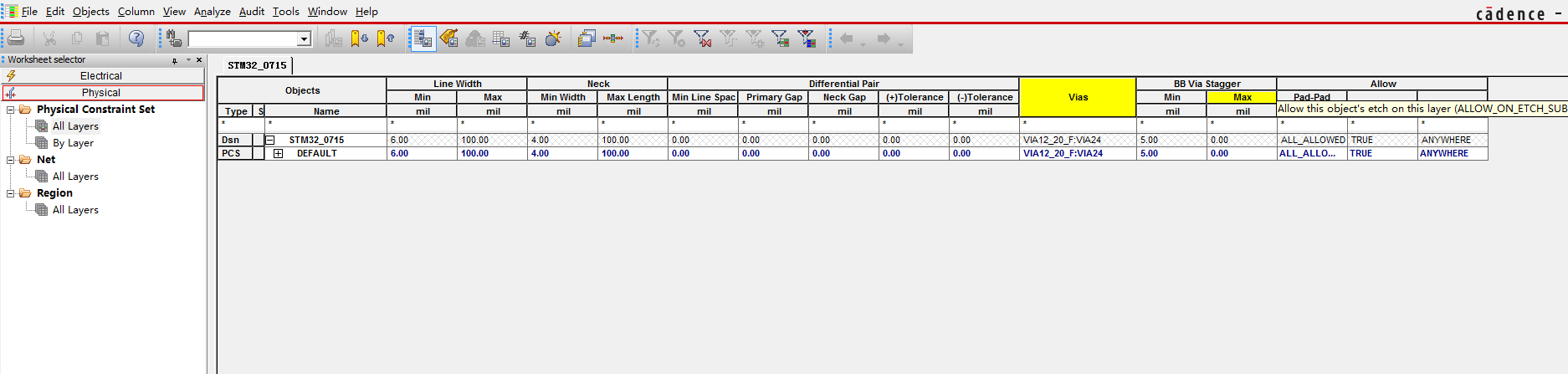

物理约束规则介绍

物理规则包括设置线宽和指定过孔库等的属性规则,在设置规则之前,需要把层叠等参数设置好。默认的为default规则。Default规则是指铺铜的单线50Ω阻抗的信号线规则,通常需要设置以下参数。(1)Line width:线宽根据阻抗计算结构进行设置,Min问默认线宽,Max为允许的最大线宽,默认为0表示不限制最大线宽,通常Min的数值不小于4mil。

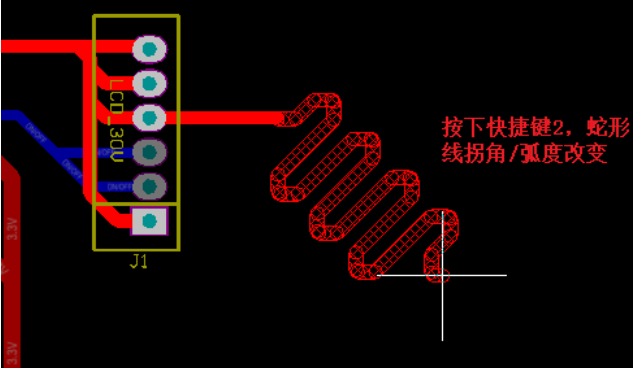

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。

扫码关注

扫码关注