- 全部

- 默认排序

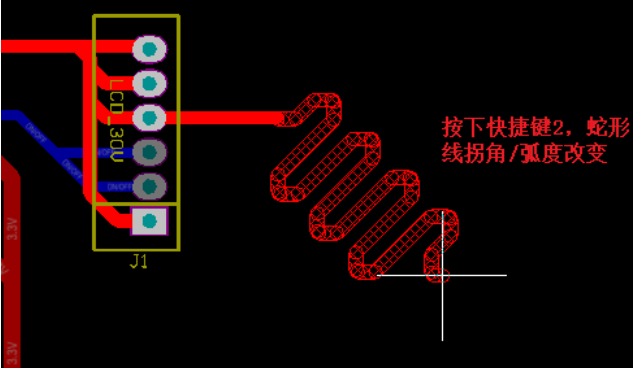

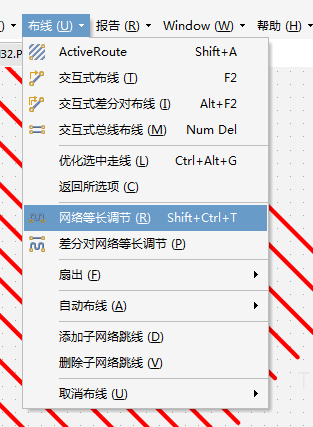

PCB设计当中,为了满足时序匹配的要求,我们通常对数据总线进行等长,那么等长的时候,我们需要用到蛇形走线,那关于蛇形等长的参数设置及要求是怎么样的呢,我们又需要去学习呢?

差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面: a.抗干扰能力强,b.能有效抑制EMI,c.时序定位精确, 那么在实际设计当中,Altium Designer软件当中差分是怎么定义添加的,又是怎么设置相关规则的呢?我们一起来学习下吧!

FanySkill集成了使用Allegro软件进行PCB设计时辅助设计人员提高工作效率的20多个Skill功能。包含了封装制作、PCB布局、PCB布线等PCB设计过程中大概率会使用到的功能。Skill大部分内容为网友共享的开源内容或共享的加密Skill,本工具的源码内容完全开放给广大使用者,可方便使用者进行Skill内容学习和Skill工具自主订制,学习者不仅可使用本 工具提高自身工作效率,亦可以DIY一套自己的Skill工具。

★ 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★交互式模块化快速布局★BGA扇孔出线的方式、BGA的快速拉线方法★菊花链拓扑结构的认识及设置★掌握蛇形等长走线,掌握★了解常见EMC的PCB处理方法3W规则的应用

★掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★交互式模块化快速布局★BGA扇孔出线的方式、BGA的快速拉线方法★掌握DDR的设计方法★掌握蛇形等长走线,掌握3W规则的应用★了解常见EMC的PCB处理方法。

★掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★掌握DDR3设计的知识要点★掌握3W原则的PCB设计★了解T点拓扑结构及设计规则★掌握蛇形等长走线,阻碍线的使用★掌握叠层阻抗计算的方法★了解常见EMC的PCB处理方法

1. 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程 2. 掌握DDR3设计的知识要点 3.掌握3W原则的PCB设计 . 了解菊花链拓扑结构及设计规则 . 掌握蛇形等长走线

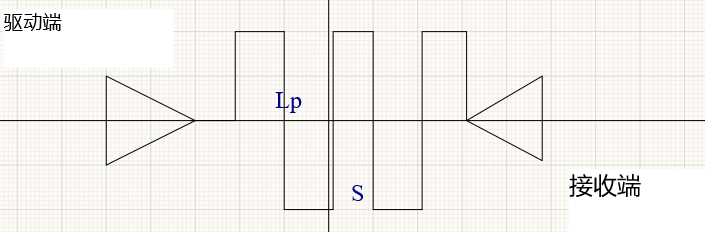

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

扫码关注

扫码关注