- 全部

- 默认排序

作为电子系统中的重要组件,放大器性能直接关系到信号传输的质量和准确性。要谈谈放大器,就不能少了失真现象,它在某种程度上可以评估放大器性能。那么,放大器的失真现象有哪些?如何区分?1、饱和失真发生在放大器输出达到其最大正电压时,信号的正半部分

示波器是一种用于测量和显示电信号随时间变化波形的仪器。其核心组成部分确保了信号的精确捕捉与显示。下面将简短谈谈示波器的具体组成结构,希望对小伙伴们有所帮助。1、显示电路示波管控制电路2、垂直(Y轴)放大电路信号放大单元3、水平(X轴)放大电

作为嵌入式系统的代表,51单片机应用广泛,其正常运作依赖稳定而精确的时钟信号,要想信号稳定,就离不开时钟振荡电路,它决定了单片机的执行速度及同步操作的时序。51单片机的时钟振荡电路可分为内部和外部时钟振荡方式,以此满足不同需求。1、内部振荡

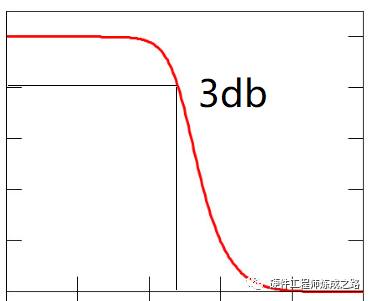

上期说到了换示波器探头,第一次使用需要对探头进行补偿电容的调节。使用示波器还有一个重要的点需要知道,那就是测试高频的时候需要用x10档,而不要用x1挡。这一点可能很多人都知道,但并不一定知道更深一点的原因,那么,我们就来说一说。 无缘高阻示波器探头带宽提一下,示波器探头的带宽也类似一个通滤波器,一般

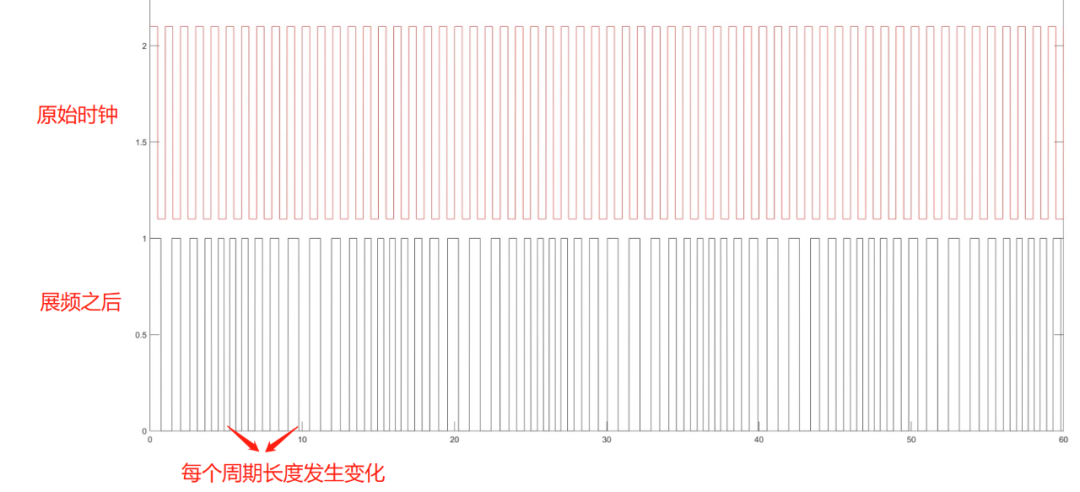

先前我们说了说:为什么时钟信号比数据信号更容易引起辐射超标?为什么时钟信号比数据信号更容易引起辐射超标?并且做了试验,如果认真看过的话,就会明白,周期性的信号是窄带频谱,特定的频率的幅值会很高,这对认证测试来说非常的不利。而一般时钟信号都是周期信号,这在电路中是少不了的。有没有什么办法,改造下时钟的

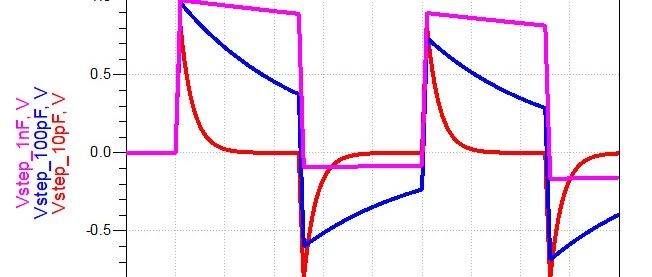

我们经常见到信号中串有耦合电容,如下结构。AC耦合电容的作用有:隔离直流分量;允许电容两端使用不同level的电压值;防止热插拔时的瞬态电流;协议要求,检测对端用;等等...这些不是我们的重点,下面我们来直观的看一下,信号通过电容后的影响;对于一个没有AC耦合电容的100MHz信号波形如下: 此

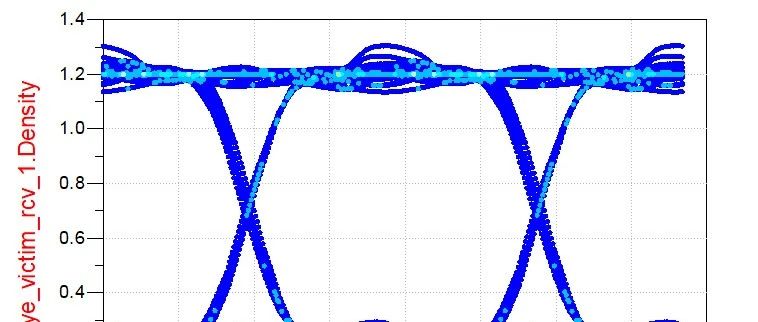

信号包地反而更差?

信号包地目的有两种,一是包地线负责回流,二是负责隔离,也就是防止串扰。 但是有时候包地线处理不好,反而会使信号变得更差。 对于如下结构,DDR4的DQ信号之间为了防止彼此串扰,用了包地线; 1、下面我们来看一下,不考虑邻近的信号线和包地线,单根信号线上的信号: 信号为点对点结构,接收

随着无线技术的高速发展,无线定位技术早已在各个领域广泛应用,虽然市场上有各种各样的无线定位技术,但究其根本,大致上可归类为以下七类!一、红外线定位工作原理:通过红外线发射设备发射红外线,待测节点的光学传感器接收信号并计算距离。优点:设备相对

逻辑分析仪作为电子设计和调试中的重要工具,其选型直接关系到测试结果的准确性和效率。以下是在选购逻辑分析仪时需要关注的六大注意事项,以确保所选设备能够满足实际需求。一、采样频率确保被测信号的频率不超过逻辑分析仪最大定时采样频率的1/3。若需测

在高速数字电路设计中,信号回流路径(Return Current Path)是一个至关重要的概念,是工程师的重要知识点,它直接关系到信号的完整性和系统的稳定性。本文将简要介绍下信号回流路径,希望对小伙伴们有所帮助。1、信号回流路径是什么?定

扫码关注

扫码关注