- 全部

- 默认排序

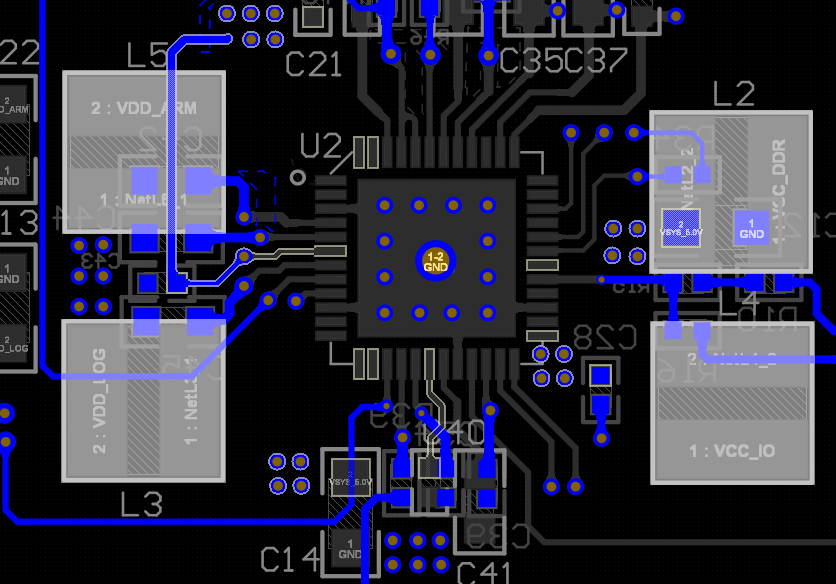

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

注意变压器除差分信号外,其他信号走线需要加粗处理2.电容尽量靠近管脚均匀摆放3.地网络需要就近打孔,连接到地平面4.注意晶振需要包地处理5.走线间距太近,后期容易造成短路,自己后期优化一下走线路径6.走线等长线之间需要满足3W规则7.时钟信

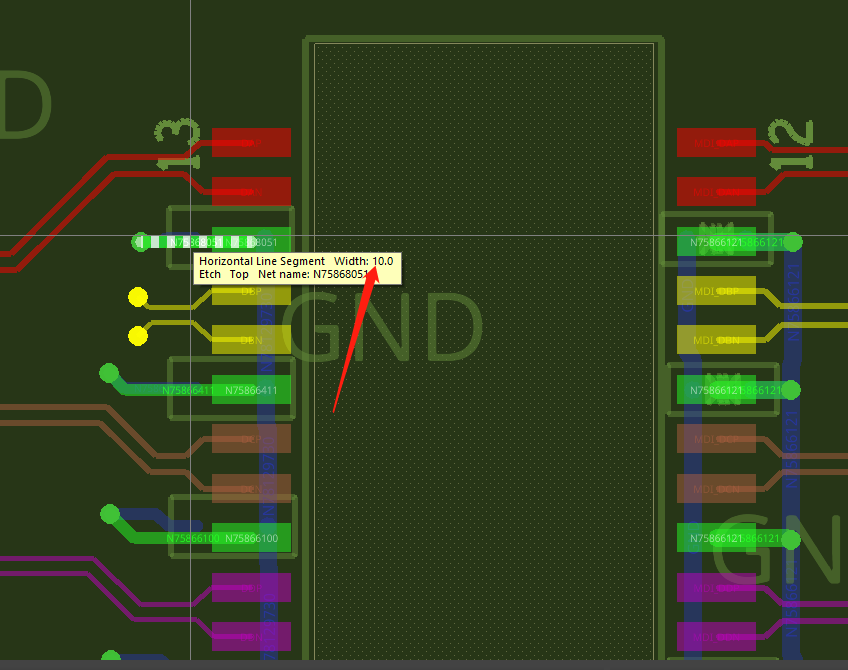

1、XA7K160T-1FFG676Q Kintex®-7 (FPGA) IC 400 11980800 162240 676FCBGAXA Kintex®-7(汽车)FPGA针对大批量汽车应用的性能和功耗进行了优化。7系列FPGA采用最先

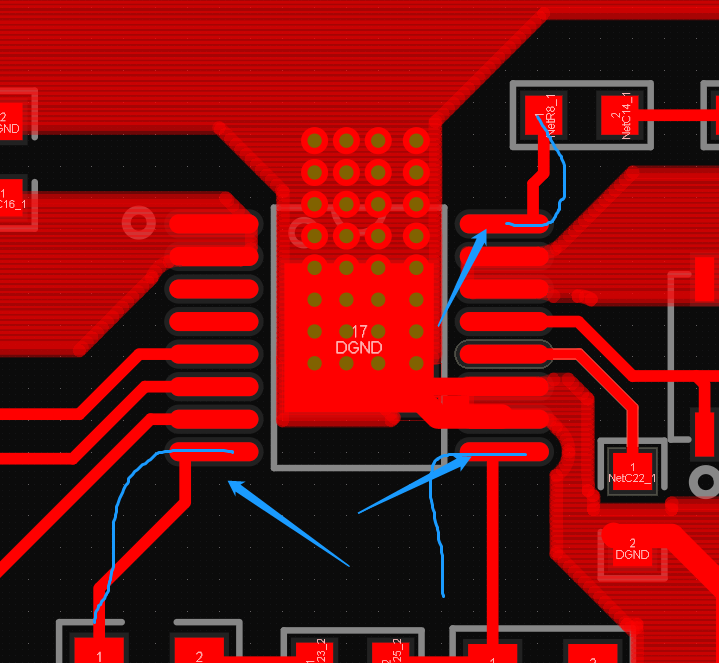

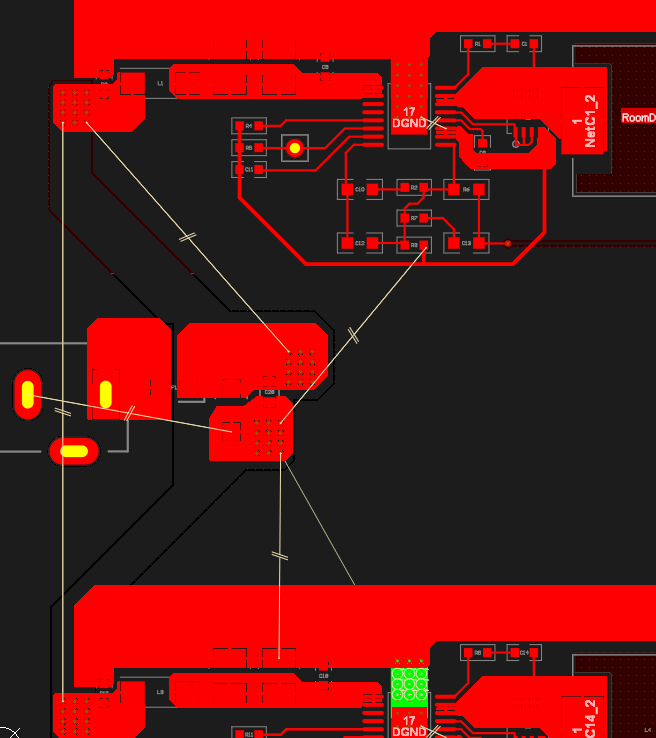

注意铜皮需要在优化一下,尽量不要有直角和任意角度2.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊3.元件摆放需要优化一下,尽量中心对其摆放4.采用单点接地,其他地方不要打孔,直接连接在芯片下面打孔进行回流5.散热焊盘中心

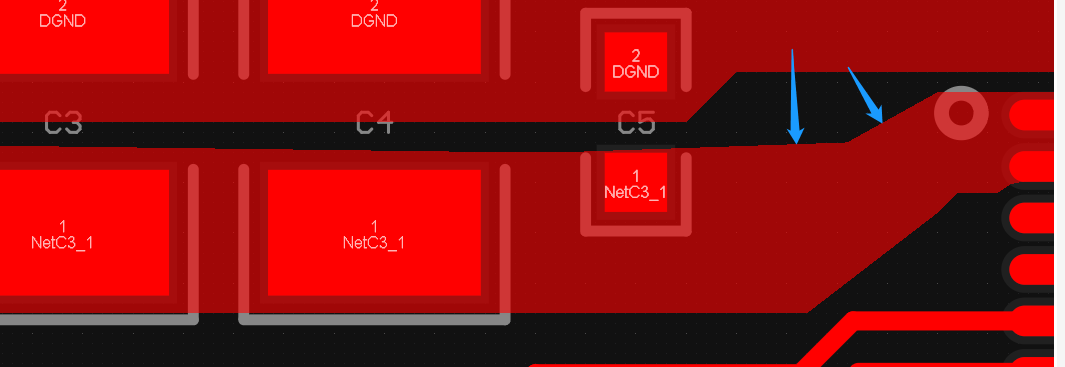

铜皮需要优化一下,注意不要有任意角度和直接2.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊3.相邻焊盘是同网络的,不能直接相连,需要先连接焊盘之后在进行连接4.此处铜皮需要优化一下5.注意器件摆放尽量中心对齐处理6.地网

作为电子设备的重要组成部分,开关电源性能的稳定性和可靠性将直接影响着整个系统的运行效果,在开关电源设计过程中,合理的布局不仅能提高电源效率,减少电磁干扰,还能优化散热性能,提升产品的整体性能,下面将探讨开关电源元器件布局的优化策略。一般来说

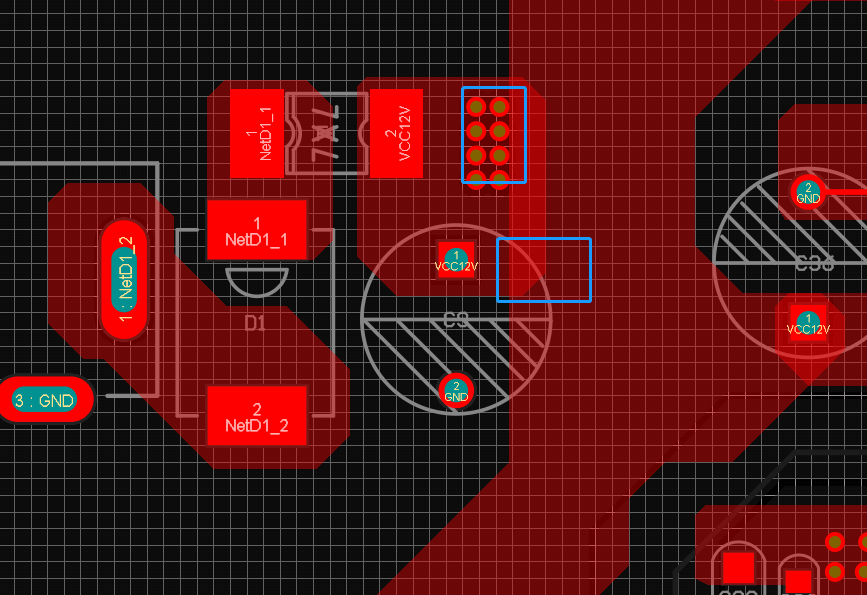

注意焊盘出线规范后期自己优化一下2.电感所在层的内部需要挖空处理3.要注意pcb需要生成板框后期自己按照画的形状按DSD生成板框4.此处铜皮需要优化一下5.散热过孔需要开窗处理6.存在无网络铜皮以上评审报告来源于凡亿教育90天高速PCB特训

电感底部不要放置器件,优化下布局:电感内部的铜皮需要挖掉:信号走线不能从电阻电容内部穿过,优化下走线路径:整体需要特别处理的就是电感底部的电容,不能放在电感底部,需要优化布局。其他的DCDC以及LDO没什么问题。以上评审报告来源于凡亿教育9

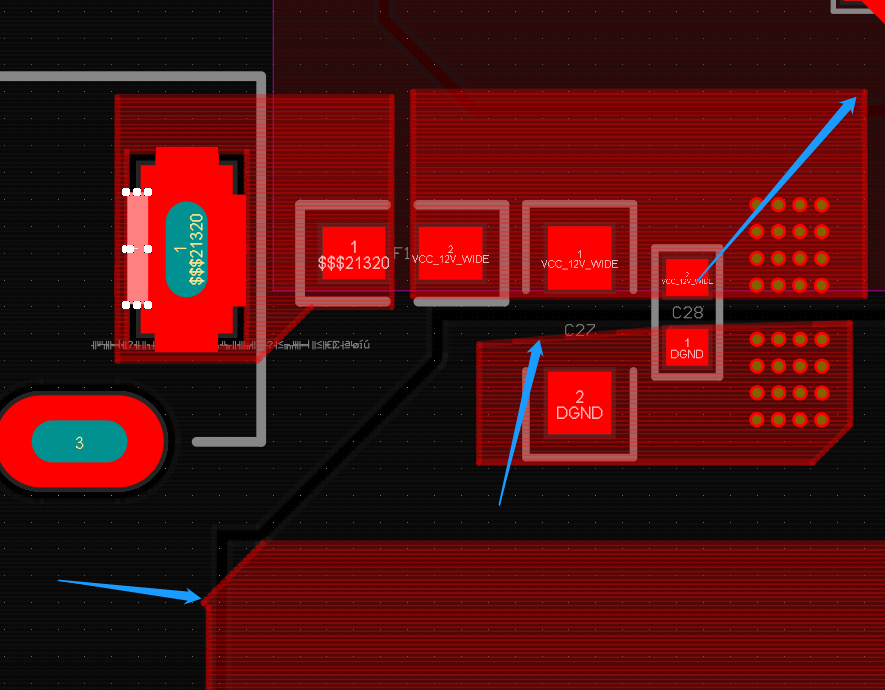

还存在飞线,网络没有连接完全:12V电源信号都没有连接上:铺铜尽量不要直角,钝角铺铜,优化下:电感内部挖空的区域是除了焊盘的区域:此处焊盘出线必须拉出焊盘再去拐线,不能直接从中心拉下来:此处还都是短路报错,自己检查下:除了IC焊盘上的过孔开

输出打孔要打在电容后面输入电容要靠近管脚摆放,越近越好,尽量少打孔后期自己调整一下布局3.布局需要优化一下,尽量紧凑,器件中心对齐,更美观4.有多余的焊盘5.输入地和输出地尽量连接在芯片中间进行回流6.注意焊盘出线规范7.散热焊盘中间需要打

扫码关注

扫码关注

![汽车级 (FPGA) XA7K160T-1FFG676Q现场可编程门阵列、XAZU3EG-1SBVA484Q [SoC FPGA] 片上系统](https://api.fanyedu.com/uploads/image/76/9210d5c0818cb4b8ad7c0fd298b00d.png)