- 全部

- 默认排序

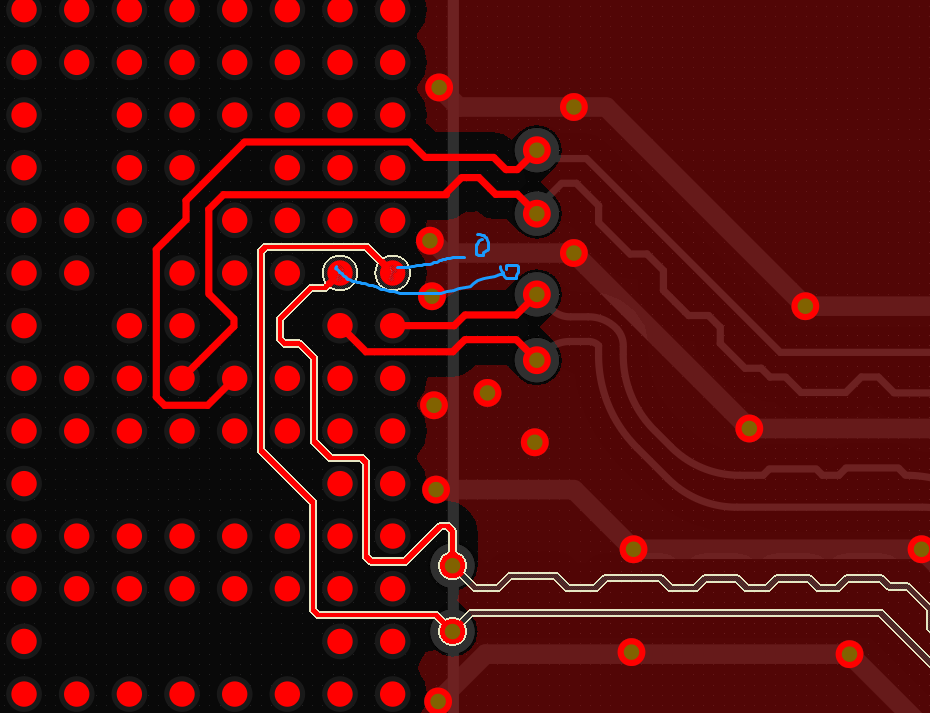

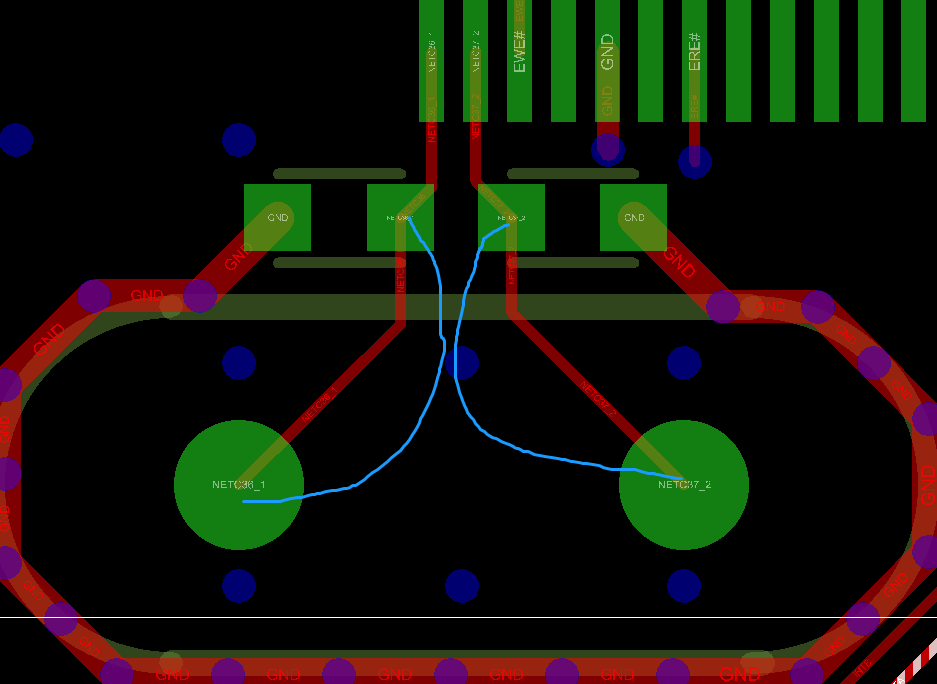

差分走线不满足差分规则,出线不耦合2.此处直接扇孔去底层连接3.差分线修理不当4.此处一个地不用进行处理,直接铺铜即可此处走线需要优化一下以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系

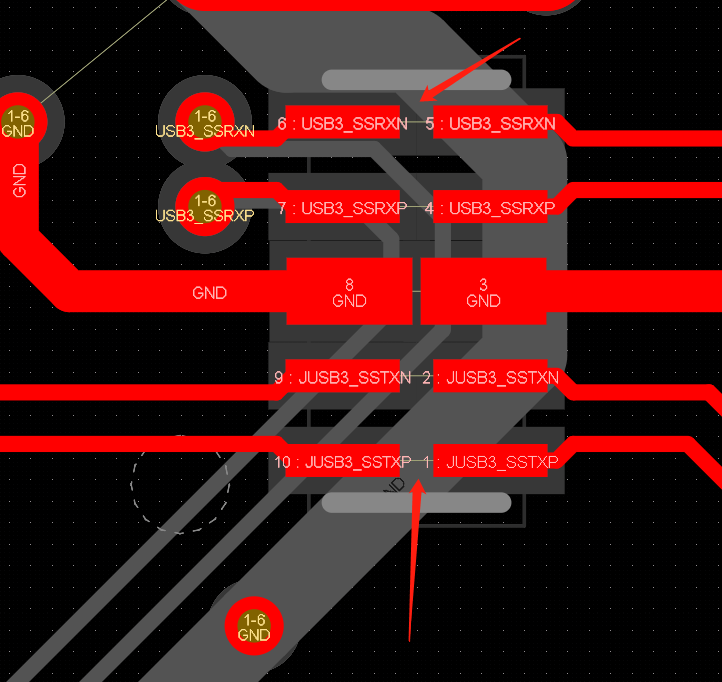

此处存在开路2.差分换层打孔尽量对齐,走线尽量耦合3.差分对内等长不规范,锯齿状等长不超过线距的两倍4.tpye-c差分对内等长误差5mil5.此处走线需要优化一下6.器件摆放尽量中心对齐7.过孔需要盖油处理以上评审报告来源于凡亿教育90天

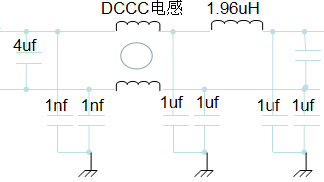

【现象描述】:XX产品传导电压法,按照车企标准等级5,全频段超标严重。测试结果(优化前):测试布置:供电电路(最大电流25A):【根因分析】:1)第一段(0.15-0.30 MHz),以差模为主;第二段(0.53-1.8 MHz),差模+共模;第三段(10 MHz左右),以共模为主;第四段(108

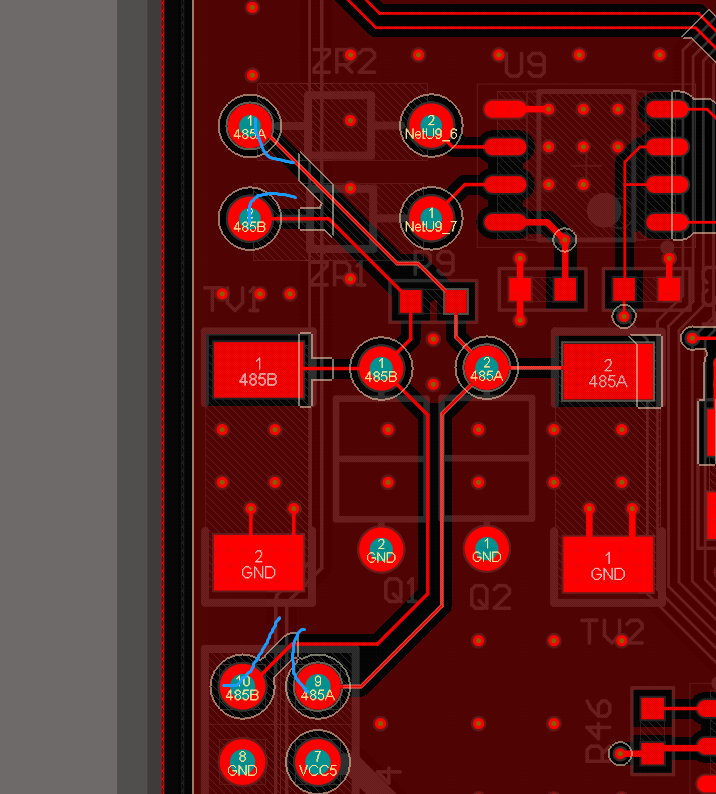

1.485需要走内差分处理2.模拟信号需要单根包地,一字型布局3.晶振走内差分需要优化一下4.跨接器件旁边尽量多打地过孔,不同的地间距建议2mm 5.除差分外,其他信号都需要加粗到20mil6.网口差分对内等长误差5mil7.模拟信号单根包

SX05-0B00-00 高性能12Gb/s SAS扩展器,采用全新的功耗优化设计,提供一流的功耗利用率和SAS技术的最新增强功能。36口、28口和24口扩展器占地面积更小,集成了ARM Cortex-R4处理器,用于系统初始化、LED管理

概述1、ADCLK846BCPZ 是一个1.2GHz LVDS/CMOS,扇出缓冲区优化的低抖动和低功耗操作。可能的配置范围从6 LVDS到12 CMOS输出,包括LVDS和CMOS输出的组合。两条控制线用于确定输出的固定块是LVDS还是

“智能”建筑的兴起引起了整个医疗保健行业的关注,因为它能够优化空间使用、为患者和临床医生提供更好的体验、更可持续的运营以及更严格的物理和网络安全。事实上,最近的一份报告指出,到 2025 年,全球所有行业的智能建筑市场将达到近 1100 亿

什么是微控制器?微控制器是一种集成电路(IC)设备,通常用于通过微处理器单元(MPU),存储器和某些外围设备来控制电子系统的其他部分。这些设备针对需要处理功能以及与数字,模拟或机电组件进行敏捷,响应性交互的嵌入式应用进行了优化。提到这类集成

晶振走内差分需要再优化一下2.模拟信号走一字型布局,没空间就调整旁边的器件和走线3.跨接器件旁边尽量多打地过孔,间距建议2mm,贴片器件建议离定位孔远一下可以参考一下此图4.地址线,控制线和时钟信号未创建等长组进行等长5.此处走线能拉直尽量

器件摆放太近,建议2mm2.晶振尽量靠近芯片摆放,走内差分,并包地处理3.注意TX,RX等长线之间需要满足3W规则4.TX整组包地少一根TXD35.电源信号可以在电源层处理6.此处差分走线需要优化一下7.变压器除产信号外,其他的都需要加粗到

扫码关注

扫码关注