- 全部

- 默认排序

内核方面,我们对 IPC 进行了优化;移除了 c99 的依赖;修复了互斥锁优先级反转的问题;完善了 API 注释。 组件方面,我们对 libc 进行了重大更新;新加了串口 v2 版本、rt-link、C++11 组件;完善了文件系统、SAL

正常放置的时候是我们先放形状然后放置管脚,如果先放管脚再放我们的形状就会关掉,优先级问题。

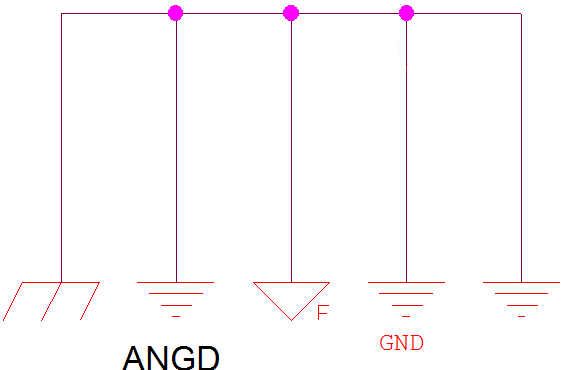

答:我们使用Orcad软件进行原理图的绘制的时候,总会遇到这样的问题:我们有多个地,网络名称是不同的,但是我们后面是统一连接在一起的,这时候最终导入到PCB之后,只会显示一个网络名称,我们想知道最终显示网络名称的优先级是什么呢?我们这里呢,一一给大家揭开这个谜底:第一步,我们绘制这样一张原理图,放置很多地,使用不同的网络名在同一张原理图中,如图3-238所示,它们所连接的网络分别为AGND、GND、GND_EARTH、GND_POWER等; 图3-238 各类不同的地放置示意图第二步,

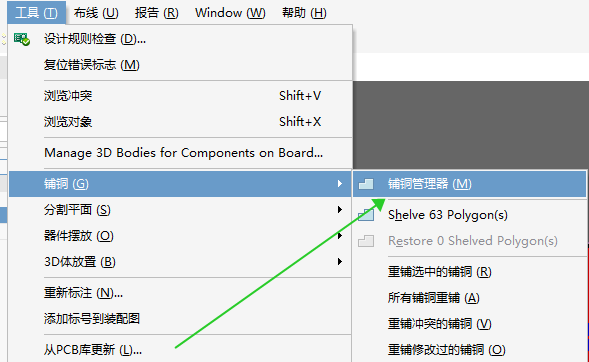

答:我们在进行设计的时候,如果是在同一层进行铺铜处理,当出现有两个或者两个以上的铜皮重叠的情况出现,如图6-106所示,A铜皮与B铜皮重叠在一起,A铜皮的优先级要高于B铜皮,所以A铜皮是保持原来的形状的,B铜皮会自动避让一块。

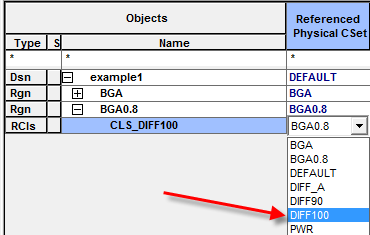

答:在进行PCB设计布线时,优先是根据阻抗线宽进行走线设计,但是在BGA区域为了方便出线,一般会添加区域走线规则,当然能够满足阻抗线宽的情况下,尽量使用阻抗线宽。这里,我们讲解一下,如何设置可以让差分阻抗线宽的优先级高于区域规则线宽,操作如下所示:

保护企业资产和信息以及确保团队成员的安全应该是任何企业的两个最高优先级。据BusinessWire称,到2025年,调查和安全服务市场的价值将攀升至4171.6亿美元。但是,由于复杂的工作流程和越来越多的网络攻击,安全团队在许多不同的商业环

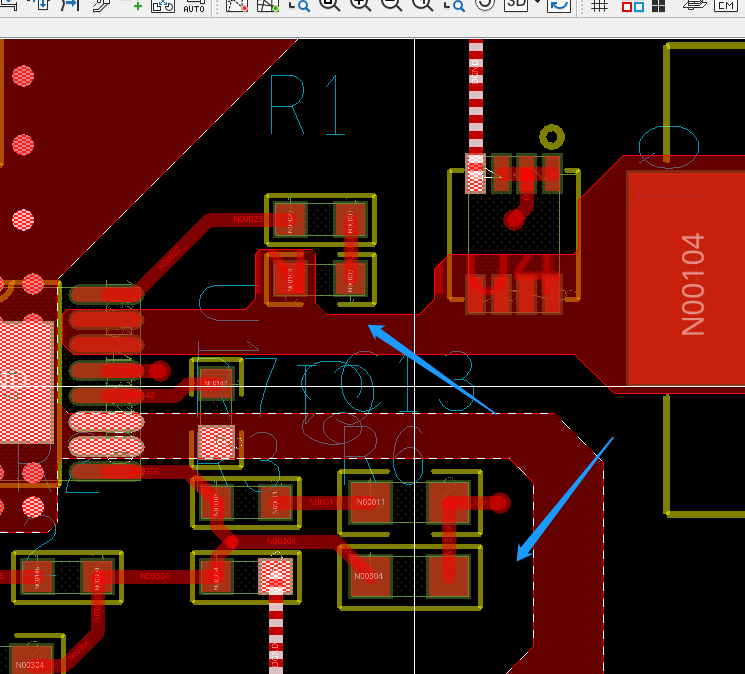

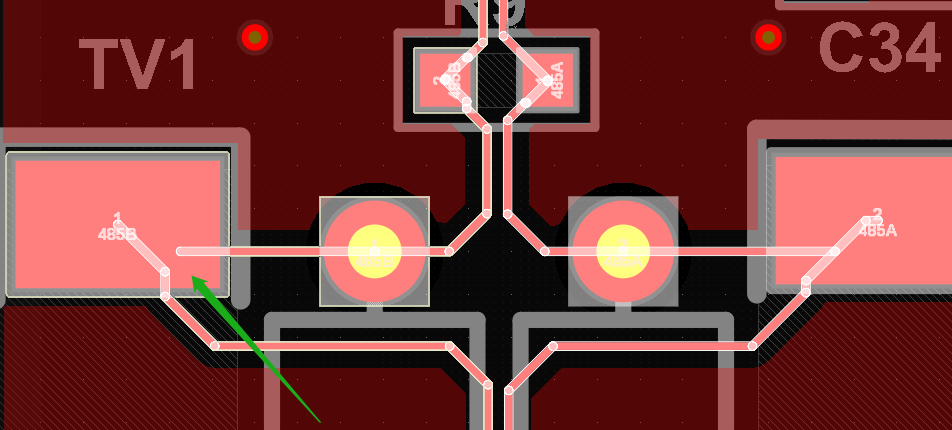

配置电阻电容注意布局可以向下向上放置,中间腾出空间优先放置主干道上的器件:主干道上的器件布局优先级最高。建议吧静态铜皮转换为动态铜皮,设计基本放置动态铜皮:反馈信号走个8-12mil即可:注意器件丝印最好调整下,不要重叠了:注意同焊盘网络连

还存在较多飞线,基本上是电源以及地没有连接:电源主干道器件尽量靠近管脚,不要间隔那么远,主干道器件优先级最高,其他的配置电阻电容可以调整的:电源输出的反馈信号也没有连接:器件尽量整体中心对齐处理下:此处电源连接的线宽完全满足不了载流大小,需

走线并未完全连接,要连接到焊盘中心:注意铜皮尽量钝角,不要直角:铺了铜皮连接,里面就不用走线了:注意电源模块对应的GND过孔也是打在最后一个输出电容的管脚后面:注意下布局,电源模块布局走线优先于主干道,布局布线优先级最高,路径尽量短:电感内

扫码关注

扫码关注

![AD19关于 [Warning] SQ.SCH Extra Pin 1 in Normal of part 的解决办法](https://api.fanyedu.com/public/uploads/huodong/20200903/cb6329590cf852a4f8373a1271407463.png)