- 全部

- 默认排序

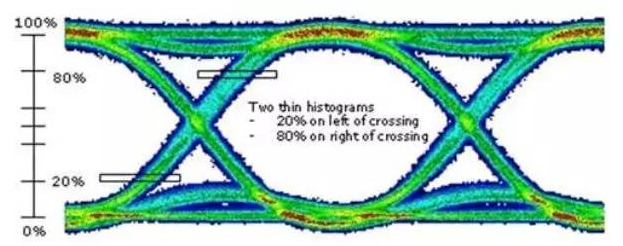

眼图,是由于示波器的余辉作用,将扫描所得的每一个码元波形重叠在一起,从而形成眼图。其是指利用实验的方法估计和改善(通过调整)传输系统性能时在示波器上观察到的一种图形。观察眼图的方法是:用一个示波器跨接在接收滤波器的输出端,然后调整示波器扫描周期,使示波器水平扫描周期与接收码元的周期同步,这时示波器屏幕上看到的图形像人的眼睛,故称 为 “眼图”。

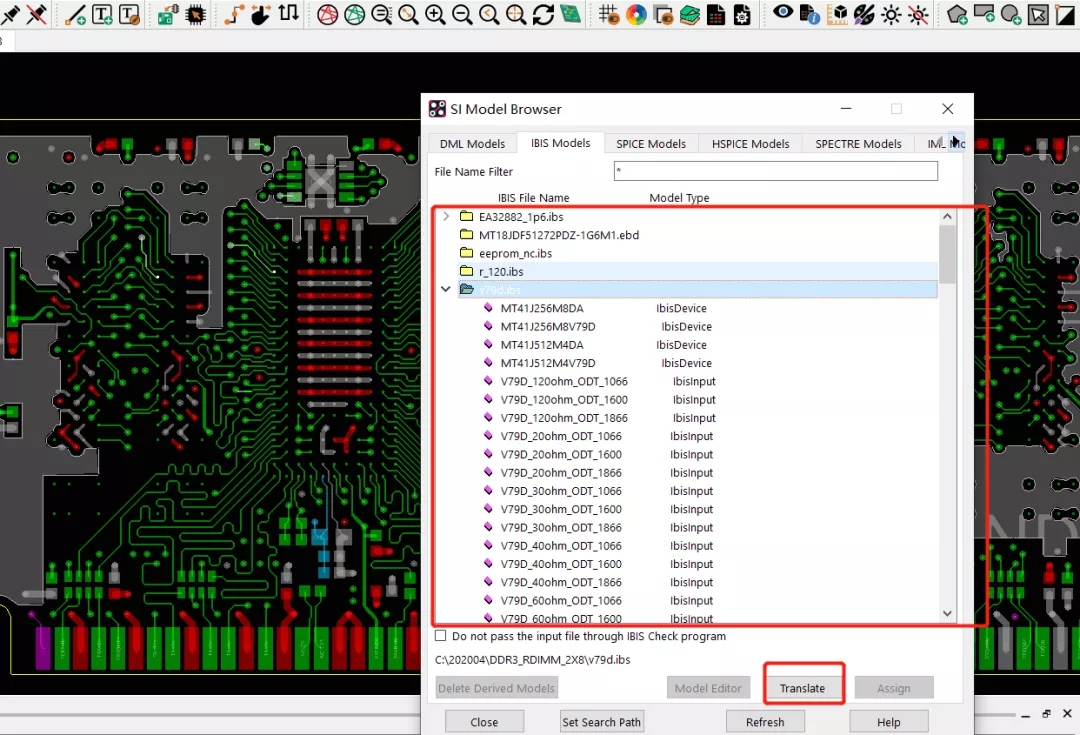

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

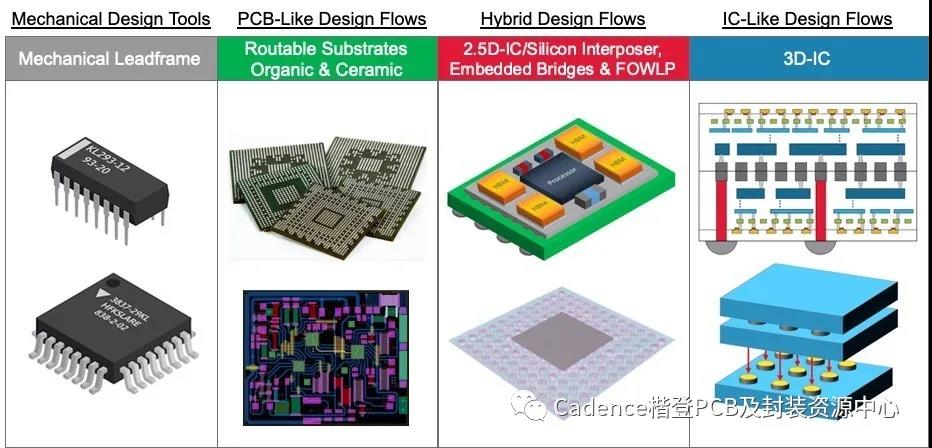

封装设计有许多处理方法: 采用以机械引线框设计封装本身 采用可布线的有机和陶瓷基板设计封装,这是一种PCB风格的设计流程 设计2.5D硅中介层、嵌入式桥和扇出型晶圆级封装(FOWLP)的混合设计流程 采用集成电路类设计流程设计具有硅穿孔(通常)的3D集成电路

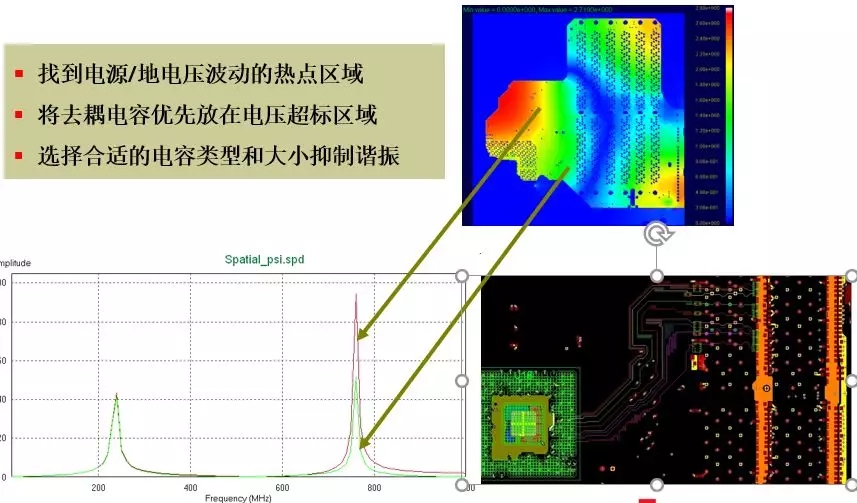

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

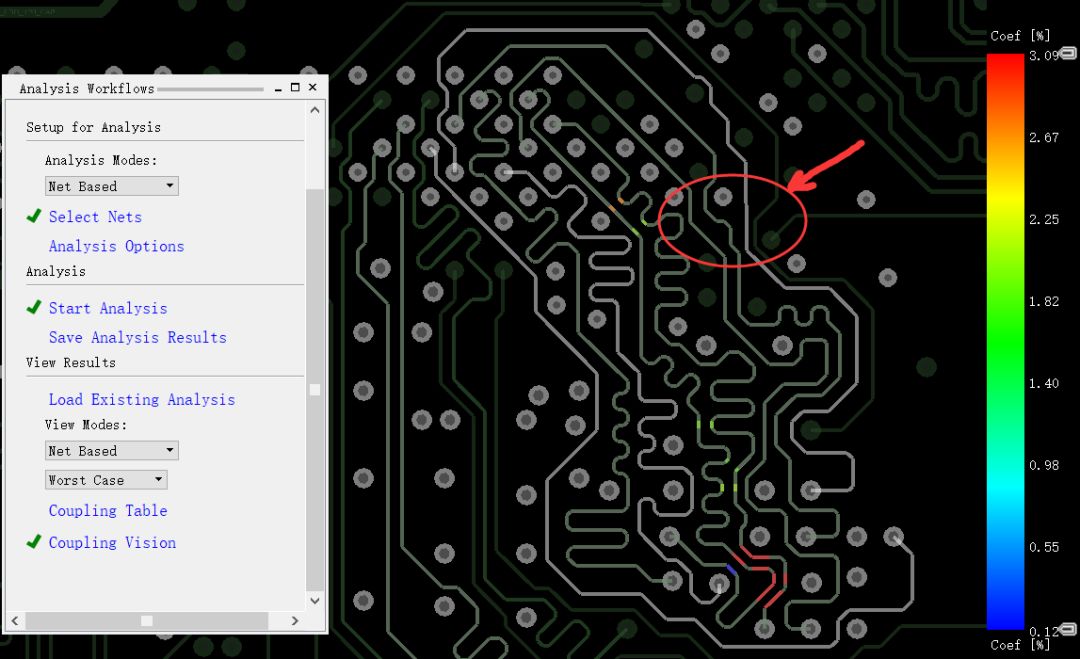

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

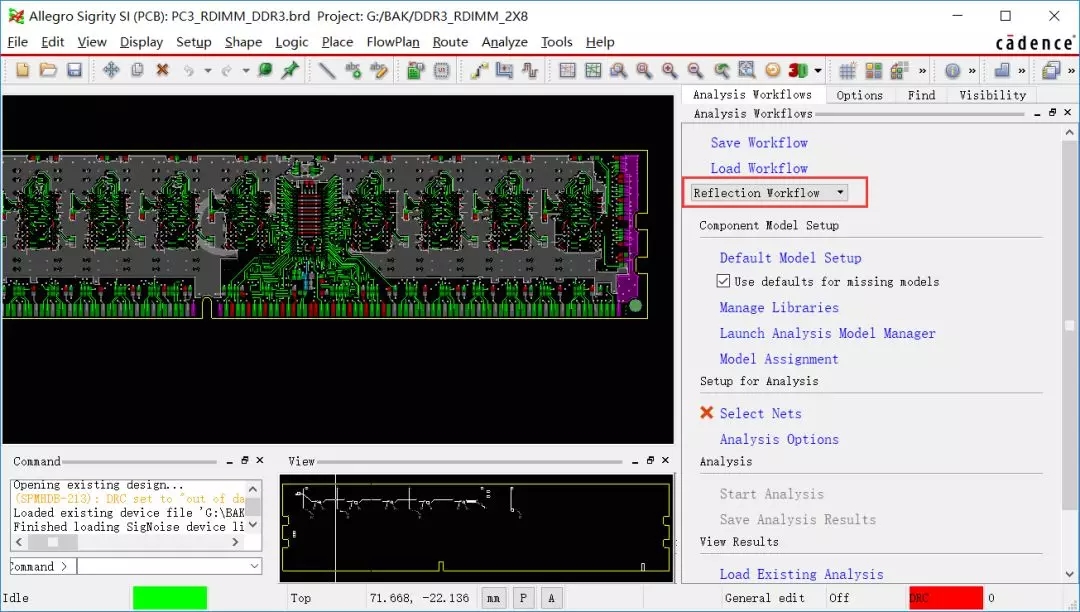

反射(reflection)和我们所熟悉的光经过不连续的介质时都会有部分能量反射回来一样,都是信号在传输线上的回波现象。此时信号功率没有全部传输到负载处,有一部分被反射回来现象。

FPGA(现场可编程门阵列)自诞生以来就一直在冲击着专用集成电路(ASIC,Application Specific Integrated Circuit)芯片界的神经。在20世纪80年代中期,RossFreeman和他的同事从Zilog手中购买了这项技术,并着手创办了针对ASIC仿真和教育市场的Xilinx。(Zilog出自埃克森美孚石油公司,因为在20世纪70年代,人们已经开始担心石油会在30年后枯竭,这一点在今天仍然适用)。同时,Altera也以类似的技术为核心成立。 FPGA是由电路编程

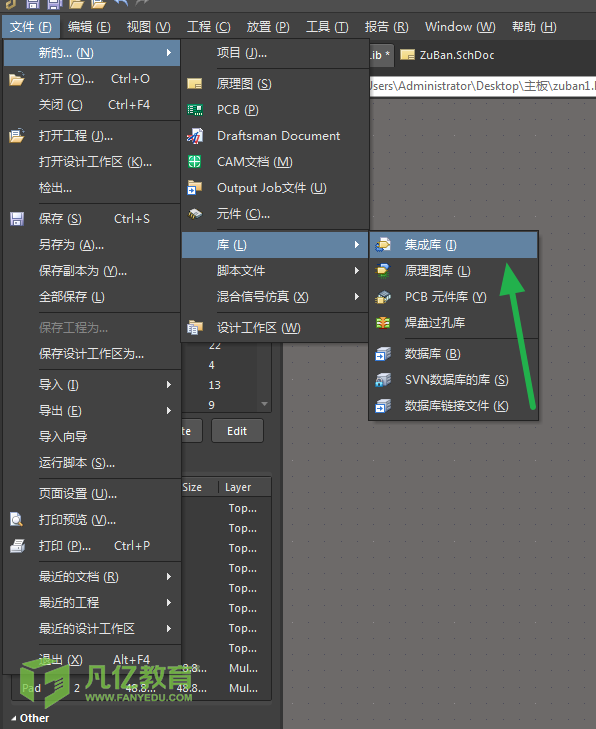

首先我们来解释一下什么是集成库?集成库就是可以让原理图的元件关联好PCB封装,电路仿真模块,信号完整性模块,3D模型等文件,方便我们在进行PCB设计的时候直接调用存储。

三极管电路图设计 电灯泡控制开关电路仿真实验-三极管不仅可以对模拟信号放大,也可作为控制开关使用,作为开关使用的三极管处于截止与饱和状态。

关于 R8 R9 R7 R10 的阻值选择问题,倘若太大的话, 比如10K 不管开关断开还是闭合,好像都没什么用,电阻上部分电流被拉低,一直为低电平,虽然仿真对,但终究有问题

扫码关注

扫码关注