- 全部

- 默认排序

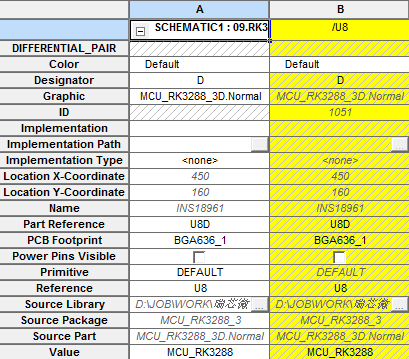

答:通常我们在编辑元件属性的时候会看到这样的界面,如图3-147所示,最直观的定义,白色的是“Instance”,黄色的是“Occurrence”。如果在“Root Schematic”放置器件会自动带有一个“Instance”和一个“Occurrence”,非“Root Schematic”放置器件只有“Instance”。为什么要分“Instance”、“Occurrence”?这种设置对设计是必要的吗?这个还要从Capture 的层次式原理图设计来讲。 图3-147 occurr

答:做封装时设置的原点,主要为了方便设计和生产。它的主要作用有以下几点:首先,制作封装时,一般都需要取一个位置为参考位置放置焊盘,此时,原点可以当作一个参考位置。其次,在PCB设计时,可以将原点当作一个参考位置,可以抓取原点进行器件的摆布,如果做封装时原点位置设置好,有利于PCB的设计,如果做封装的时候没注意原点位置,比如将原点位置设置得离焊盘很远,在做PCB设计抓取器件时非常不方便。最后,在PCB设计结束后,可以出具GERBER文件以便PCB生产和贴片,一般出GERBER时会一起出一个器件的原

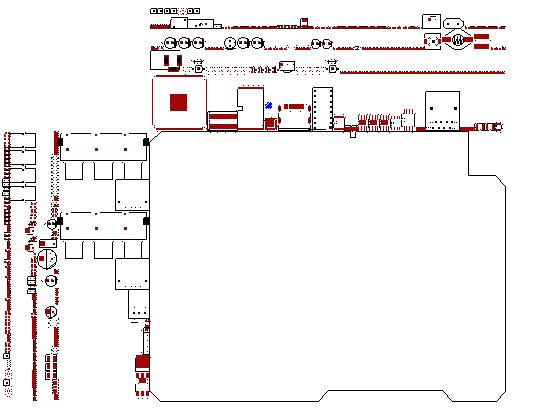

答:很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么PCB板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:

答:简单来说,数字地是数字电路部分的公共基准端,即数字电压信号的基准端;模拟地是模拟电路部分的公共基准端,模拟信号的电压基准端(零电位点)。

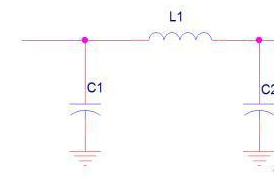

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

(1)首先我们在进行TRIAC其驱动电路设计的时候,我们一般不直接进行驱动,而是通过DIAC或者Photo-TRIAC即光学的双向可控硅配合来使用进行驱动电路的设计,为什么呢?

(1)首先大家要明白一点,EPAD主要是在QFN和DQFN封装相关的IC中会进行如此设计(2)什么叫QFN和DQFN呢?上图 ,如下:

一、为什么要学EMC?身为企业,您或许有这样的EMC烦恼:产品EMC问题层出不穷!! 没有专业的EMC工程师!! 多款产品研发进度滞后!!…………

扫码关注

扫码关注