- 全部

- 默认排序

在电子设计中,印刷电路板(PCB)的地线处理是一个至关重要的环节,若地线设计不当,不仅影响电路性能,还有可能导致后续项目无法正常运行,所以必须郑重了解地线的设计不当会带来哪些问题?1、信号串扰当不同功能的地线直接连接在一起时,可能会出现信号

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

在高频PCB设计中,如何降低串扰问题的影响,是很多电子工程师必须考虑的首要问题,串扰,即信号线之间的互相干扰,可能导致信号失真、误码率上升,从而影响整个电路的性能和稳定性,那么如何从布局布线方面入手?1、利用地线隔离在布线空间允许的条件下,

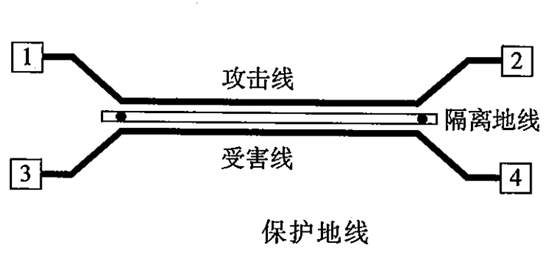

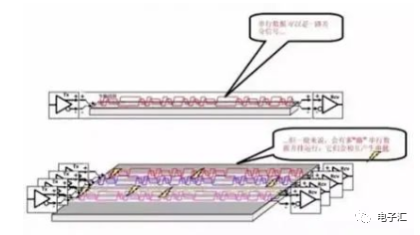

包地与串扰

工程界常常使用保护地线进行隔离,来抑制信号间的相互干扰。的确,保护地线有时能够提高信号间的隔离度,但是保护地线并不是总是有效的,有时甚至反而会使干扰更加恶化。使用保护地线必须根据实际情况仔细分析,并认真处理。保护地线是指在两个信号线之间插入一根网络为GND的走线,用于将两个信号隔离开,地线两端打GN

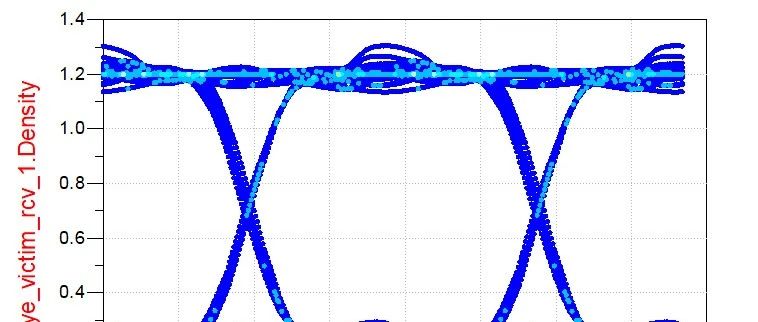

电子工程师如何观察眼图?

在高速互连系统的设计和维护中,信号完整性的分析是很重要,很多电子工程师经常会通过“眼图”工具来评估系统性能,眼图是一种累计的数字信号图形,包含了丰富的信息,可反映码间串扰和噪声影响,进而评估系统的优劣程度,那么如何观察眼图?1、跨接示波器至

随着PCB设计复杂度越来越高,对信号完整性的分析除了反射、串扰及EMI之外,稳定可靠的电源供应也成为了大家重点研究的方向之一,特别是在低压大电流和高速设计供电场景中,电源的波动往往会带来致命的影响,于是,电源完整性PI(Power Inte

在高速数字电路设计中,要根据电路合理选择端接方式,选择适当,有利于确保信号完整性、减少反射和串扰,本文将针对常见的端接方式,分析其特点、适用场景及关键参数,希望对小伙伴们有所帮助。1、串联端接①特点在源端串联一个电阻RS,使源端反射系数为零

在高速信号传输系统中,工程师必须确保信号质量,以此提高系统稳定性。但是随着信号频率的不断提升,信号完整性(SI)问题日益凸显,反射、串扰、衰减等问题层出不穷。如果在系统中增加测试点,是否会加剧SI问题?1、测试点有什么用?①监控信号状态测试

信号包地反而更差?

信号包地目的有两种,一是包地线负责回流,二是负责隔离,也就是防止串扰。但是有时候包地线处理不好,反而会使信号变得更差。对于如下结构,DDR4的DQ信号之间为了防止彼此串扰,用了包地线;下面我们来看一下,不考虑邻近的信号线和包地线,单根信号线上的信号: 信号为点对点结构,接收端内部ODT端接,信号质量

信号串扰知识讲解

在射频电路研究学习的过程中,相信大家都遇到过在电路中信号频率的变高、边沿变陡、电路板的尺寸变小、布线的密度变大等问题,这些几乎是不可避免的问题。这种影响信号完整性的问题叫做串扰,在电路计中普遍存在,有可能出现在芯片、PCB板、连接器、芯片封装和连接器电缆等器件上。如果串扰超过一定的限度就会引起电路的

扫码关注

扫码关注