- 全部

- 默认排序

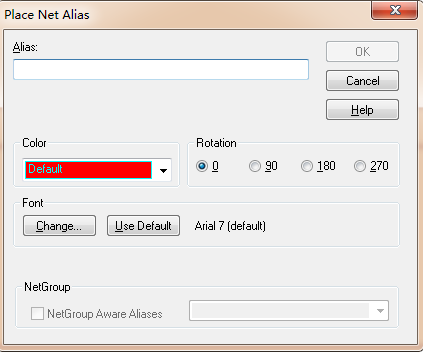

答:Net Alias的中文含义就是网络标号的意思,它的作用于Wire的功能其实是一致的,都是让两个或者多个网络连接在一起,区别在与Wire是直接连线,把相同的网络连接在一起,非常直观;而 Net Alias则是放置相同的标号,通过相同的标识把网络连接在一起,本质是一致的。Net Alias的使用方法如下所示:第一步,首先在要放置网络标号的网络上放置一段Wire,用于放置Net Alias;第二步,点击菜单Place→Net Alias…,或者按快捷键N,放置网络标号,在弹出的属性对话

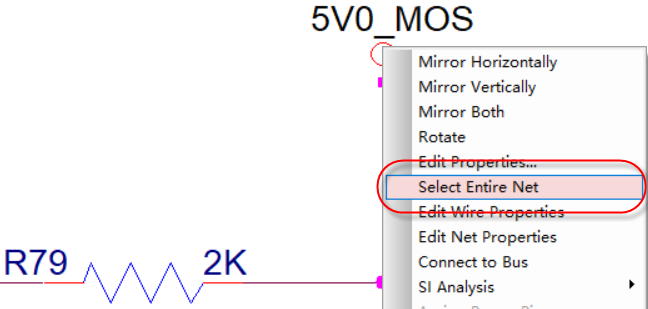

答:orcad在绘制原理图过程中,需要对器件进行移动,有如下几种操作的小技巧,如下列所示:Ø 鼠标左键选中元器件,按住鼠标左键不松,就可以对元器件进行任意位置的拖动,若此元器件已经与其它电路相连,这些连线会跟着一起移动;Ø 按住Ctrl键,再使用鼠标左键进行元器件的拖动,其作用是复制一个元器件,不做任何连接,与选中元器件、按Ctrl+C的功能是一致的;Ø 拖动元器件的时候,若是连接关系不动、只移动走元器件,操作的方法就是按住Alt,然后左键拖动元器件,则只拖动改元器

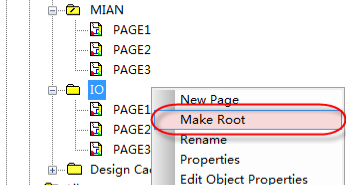

答:在使用Orcad软件绘制原理图时,通常会把一个工程下面对应的不同部分的原理图绘制在一起,如图3-184所示,这样方便后期的检查与查看,这样做有一个问题,你会发现输出网表的时候,不能全部输出,一下子只能输出一个文件的网表。这里我们给大家讲述一下怎么输出所有文件的网表: 图3-184 原理图不同的工程示意图第一步,我们选中原理图的根目录时,点击输出网表的命令,输出的网表都是最上面的那个MIAN的三页图纸的网表;第二步,我们需要输出下面的IO的三页图纸的网表,需要将IO原理图

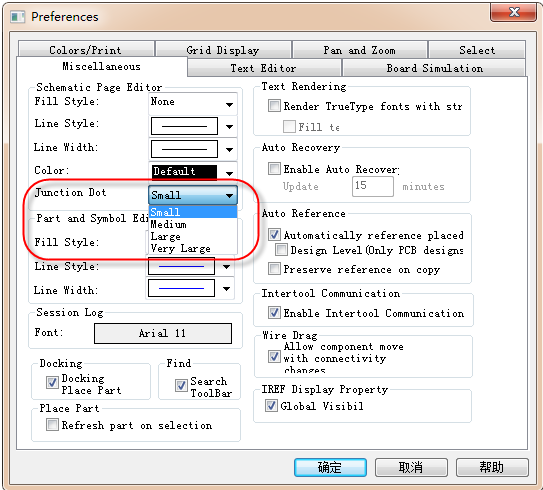

答:我们在使用Orcad软件进行原理图的绘制,相同的网络的连接点处,连接在一起的时候,系统会自动生成连接点,也就是Junction点。默认的Junction点是比较小的,容易看不清楚,所以这里会有这样的一个疑问,这个Junction点是否可以对它的大小进行修改呢,答案是肯定的,是可以进行修改的,具体操作的办法如下:第一步,我们需要对参数进行设置,选中原理图的根目录,DSN文件,执行菜单命令Options,在下拉菜单中选择Preferences,进行参数的设置;第二步,进入参数设置界面之后,我们需

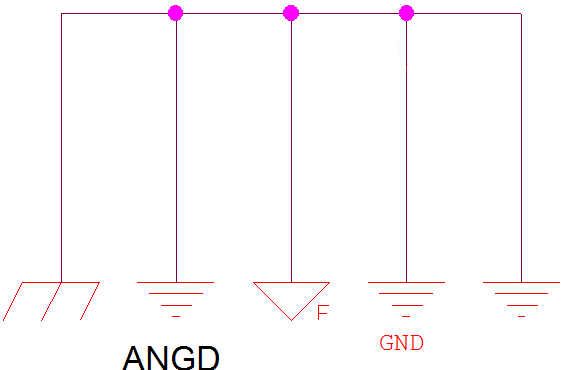

答:我们使用Orcad软件进行原理图的绘制的时候,总会遇到这样的问题:我们有多个地,网络名称是不同的,但是我们后面是统一连接在一起的,这时候最终导入到PCB之后,只会显示一个网络名称,我们想知道最终显示网络名称的优先级是什么呢?我们这里呢,一一给大家揭开这个谜底:第一步,我们绘制这样一张原理图,放置很多地,使用不同的网络名在同一张原理图中,如图3-238所示,它们所连接的网络分别为AGND、GND、GND_EARTH、GND_POWER等; 图3-238 各类不同的地放置示意图第二步,

答:用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_top层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。一般放置占地面积是根据不同的器件类型放置不同尺寸大小,具体大小可参考以下尺寸。Chip元件, place_bound层器件最大外围尺寸(焊盘和丝印中取大值)

答:做封装时设置的原点,主要为了方便设计和生产。它的主要作用有以下几点:首先,制作封装时,一般都需要取一个位置为参考位置放置焊盘,此时,原点可以当作一个参考位置。其次,在PCB设计时,可以将原点当作一个参考位置,可以抓取原点进行器件的摆布,如果做封装时原点位置设置好,有利于PCB的设计,如果做封装的时候没注意原点位置,比如将原点位置设置得离焊盘很远,在做PCB设计抓取器件时非常不方便。最后,在PCB设计结束后,可以出具GERBER文件以便PCB生产和贴片,一般出GERBER时会一起出一个器件的原

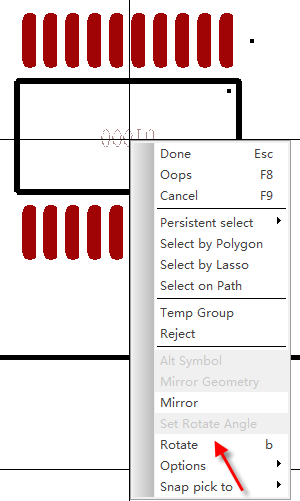

答:在Allegro软件中有两个旋转命令,一个是spin命令,一个是Rotate命令,我们这里讲述一下两个命令的使用方法解析,具体如下所示:首先,Rotate命令,这个命令是不能单独使用的,必须搭配Move命令一起使用,执行移动命令,选择需要移动的对象,将对象吸附在鼠标上,点击鼠标右键,选择Rotate命令,如图5-162所示,在Optins面板可以设置旋转的参数;

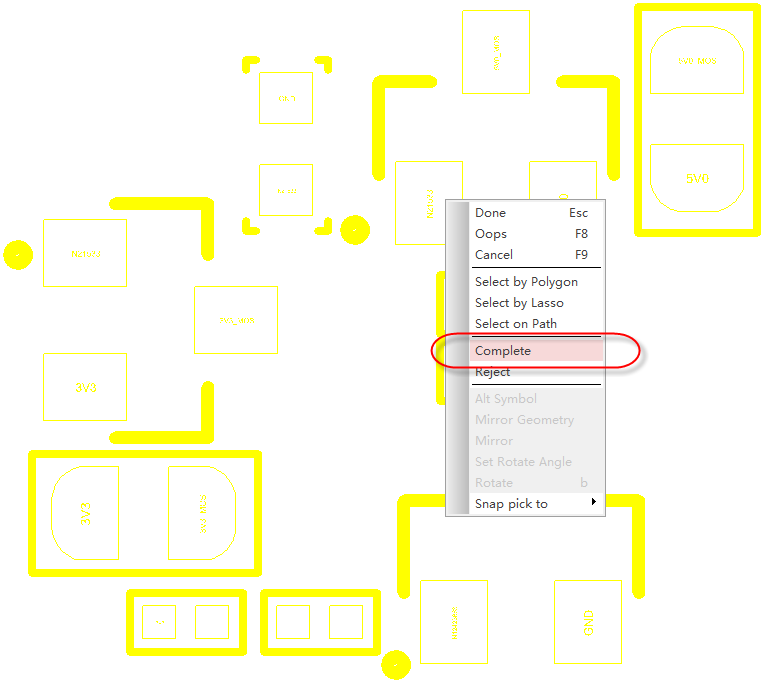

答:所谓的Temp Group,就相当于临时创建的Group组,用于很多元素的选择,用于一起执行某项命令,比如移动、复制等等。执行完命令之后呢,Group组就打散了,不存在了,我们以移动命令为例,讲解一下如何使用Temp Group功能。

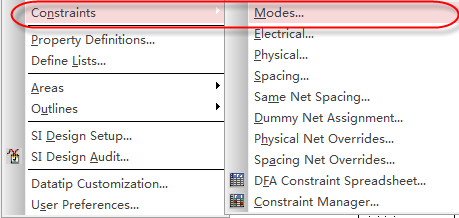

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

扫码关注

扫码关注