- 全部

- 默认排序

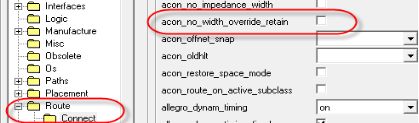

答:在Allegro PCB中,会经常切换走线线宽,一般Allegro PCB默认是记忆走线线宽的,即走完一个信号在连接一个新的网络线时,软件会默认使用连接上一个网络所使用的线宽。可以通过设置,让软件不执行自动记忆上一次走线宽度。

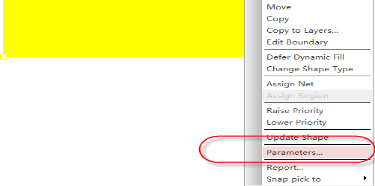

答:一般在使用Allegro软件设计时,铺铜都会铺实铜,但是对于如FPC设计,通常需要铺网格铜,以满足PCB的弯折性要求。具体操作的步骤如下所示:第一步,首先使用Shape-Polygen选项,在PCB上画一个铜皮,此时画出来的铜皮是实心的,如图6-297所示;

答:在做封装时,一般会添加2种类型的器件编号,即装配字符和丝印字符,这2种类型的器件编号分别是添加到Ref Des-Assembly_Top层、Ref Des-Silkscreen_top层。

答:使用Allegro进行布线时,一般需要将走线从焊盘中心走出来,如果走线没从中心出来,可按以下步骤进行设置:

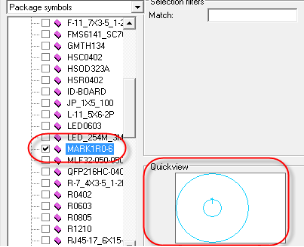

答:在设计PCB时,一般需要添加Mark点到PCB上,以方便PCB贴片。一般有2种方法可将Mark点添加到PCB上。

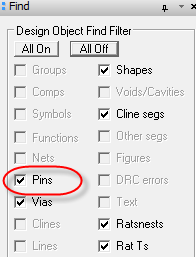

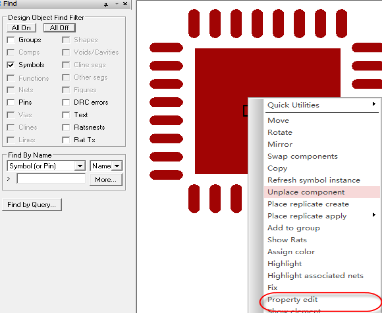

答:使用Allegro进行PCB设计时,一般我们不能将一个封装里的焊盘管脚单独移动,通常是整个封装一齐移动。如若需要将焊盘单独移动,可按以下步骤处理:

答:使用Allegro软件进行PCB设计,一般会使用约束规则辅助设计,当设计时有对象违反了设置的约束规则,软件会以DRC标记的形式提醒设计者。

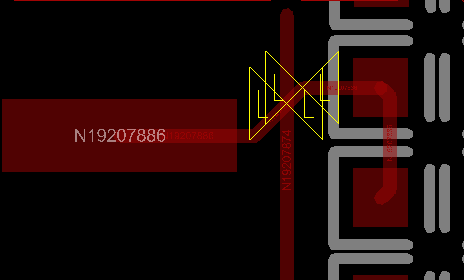

答:我们PCB布局完成之后,需要对网络进行扇出,一般空的管脚、空的网络不需要进行扇出,为了提高布线效率,我们会对空的网络进行高亮显示,具体的操作步骤如下所示:

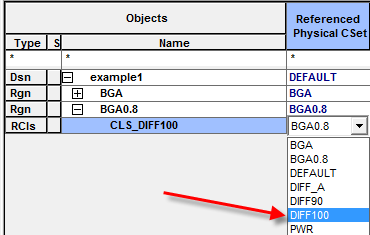

答:在进行PCB设计布线时,优先是根据阻抗线宽进行走线设计,但是在BGA区域为了方便出线,一般会添加区域走线规则,当然能够满足阻抗线宽的情况下,尽量使用阻抗线宽。这里,我们讲解一下,如何设置可以让差分阻抗线宽的优先级高于区域规则线宽,操作如下所示:

答:一个完整的PCB封装是由许多不同元素组合而成的,不同的器件所需的组成元素也不同。一般来说,封装组成元素包含:沉板开孔尺寸、尺寸标注、倒角尺寸、焊盘、阻焊、孔径、热风焊盘、反焊盘、管脚编号(Pin Number)、管脚间距、管脚跨距、丝印线、装配线、禁止布线区、禁止布孔区、位号字符、装配字符、1脚标识、安装标识、占地面积、器件高度。

扫码关注

扫码关注