- 全部

- 默认排序

本套视频的目的是让工程师能够通过15个项目分析实例学习快速的掌握好通用频域和时域分析高速互联问题的技巧方法,将方法融入到自己的高速互联分析中去,从而科学地解决自己的项目存在的问题。

我们看到跟随电子设计速度越高越高,体积越来越小,功率越来越高,工程师所面临的问题越来越多,也越复杂和多样。这就要求工程师能够掌握好Cadence sigrity2019 /Clarity/ Celsius等分析工具的使用技巧,能够在整个设计过程中解决高速问题。将这种方法让设计不用在设计过程的后期进行耗时的仿真-修复-仿真的迭代。让工程师通过以制造容限来建立拓扑和模型进行分析从而使得产品的电汽性能最优化以及成本最小化。用综合的设计和仿真分析方法来应对解决突出的技术难题。

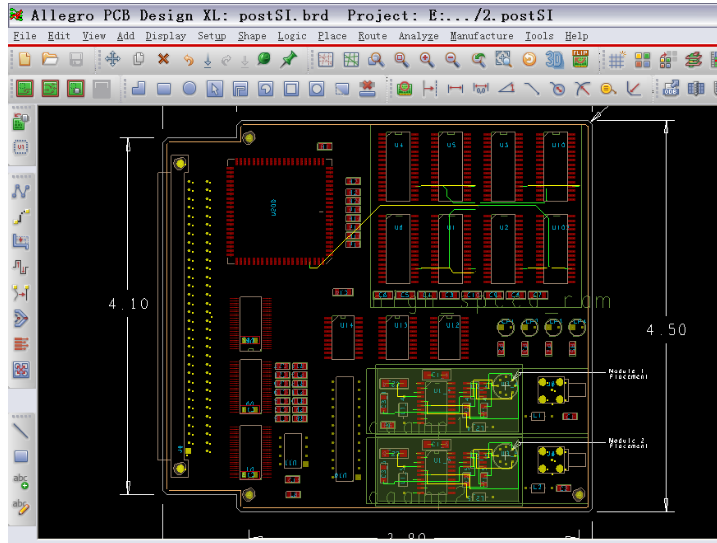

Cadence17.4软件的界面变化后,软件的功能也进行了很大的调整,更加能够适应高速电路和高密度,柔性和刚柔结合设计,背钻异形槽孔的设计等。

Cadence17.4软件的界面变化后,软件的功能也进行了很大的调整,更加能够适应高速电路和高密度,柔性和刚柔结合设计,背钻异形槽孔的设计等。

Cadence17.4软件的界面变化后,软件的功能也进行了很大的调整,更加能够适应高速电路和高密度,柔性和刚柔结合设计,背钻异形槽孔的设计等。

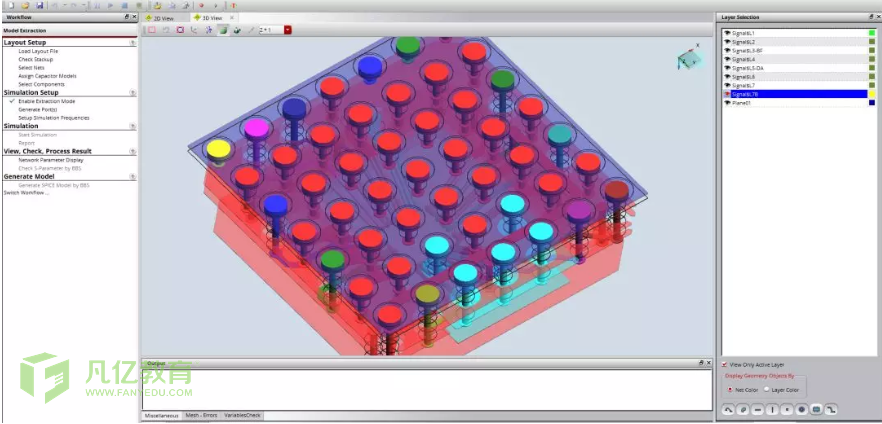

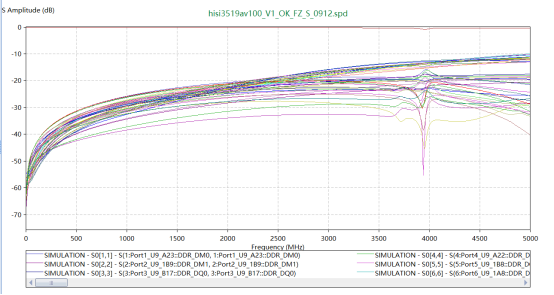

在IC封装的分析中,为了能够提取到更加趋近于真实测量结果的S参数(或者其他参数),需要在封装体上添加假性球体和参考层,下面来讲解在sigrity™ PowerSI®工具中添加假性球体和参考层的方法。

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

扫码关注

扫码关注

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第二部]](https://api.fanyedu.com/public/uploads/image/course/20200518/92b8de8dc1073a42c2d24b16c709e55e.jpg)

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第一部]](https://api.fanyedu.com/public/uploads/image/course/20200516/146c7f84154ccbf93c281a00756c6906.jpg)

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第三部]](https://api.fanyedu.com/public/uploads/image/course/20200519/55b5b9f147397aa1097829400b322791.jpg)