- 全部

- 默认排序

双列直插封装(dual in-line package)也称为DIP封装或DIP包装,简称为DIP或DIL,是一种集成电路的封装方式。DIP插件工艺是在SMT贴片工艺之后,是PCBA工艺中的一部分,DIP插件是指不能被机器贴装的大尺寸元器件

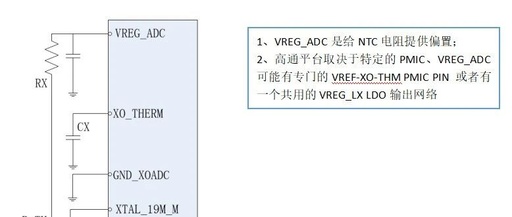

高通晶振设计指导

前言:1、随着目前PCB越来越小,越来越薄,导致更加严重的散热问题2、XTAL_IN/XTAL_OUT和GND_line可以作为热源的传热路径,导致GPS/GNSS受到影响。3、布局区域约束要求晶振布局必须靠近PMIC 一、布局要求1、晶振需要远离PMIC,需要保证XTAL_IN/OUT的距离在3~

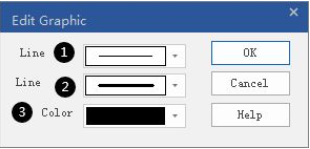

设计当中,可以通过放置辅助线来标识信号方向或者对功能模块进行分块标识。1)执行菜单命令“Place-line”(快捷键“Shift+L”),激活放置状态。2)在一个合适的位置单击鼠标左键,找到下一个位置单击鼠标左键确认结束点。3)在放置之后

华为、中兴国际近四年来以致面对美国的无理打压,都遇到了列入实体清单并断供资源,度过了艰难岁月,为避免华为等站起来,美国正在劝说多国政府封杀华为等,如今德国或将被吹动。近日,据德国媒体Zeit Online报道,德国政府计划禁止本国电信运营商

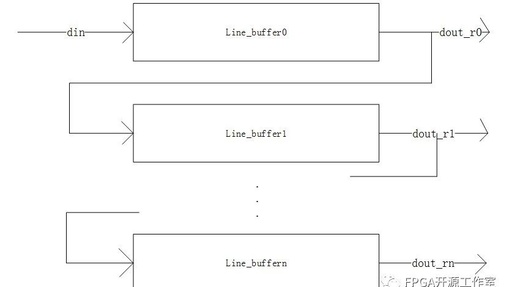

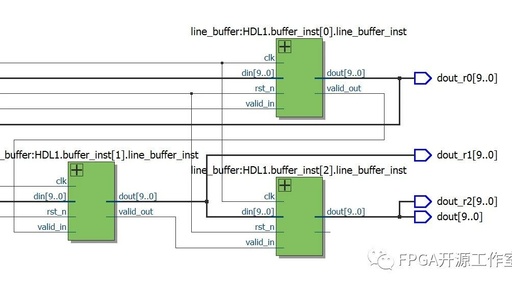

FPGA图像处理之行缓存(linebuffer)的设计一背景知识 在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。FPGA实现图1 行缓存菊花链

FPGA图像处理之行缓存(linebuffer)的设计二作者:OpenS_Lee01背景知识 在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。0

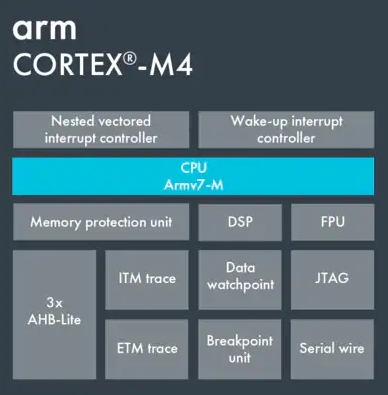

一、STM8S105S4T6CIC MCU 8BIT 16KB FLASH 44LQFPSTM8S105S4T6C Access line 8位微控制器提供16KB 闪存程序存储器,以及集成的真数据EEPROM。STM8S105x4/6 A

在电子领域中,LISN是一个充满神秘感的工具,常常被用于电磁兼容性测试。本文将深入探讨LISN的本质是什么,以及它在电子领域中扮演的关键角色。1. 认识LISNLISN,全称为line Impedance Stabilization Net

对工程师来说,在高速PCB设计中选择合适的传输线类型,对信号完整性很重要,而传输线结构可分为微带线(microstrip)与带状线(stripline),那么如何选择?1、信号速度与插入损耗若设计涉及高速信号传输,且追求更低的插入损耗,应优

如果您曾经尝试过去除设计的某个区域,您可能会发现这个过程比想象的更加复杂。如果我们使用显示元素(show element)功能来选择该区域中的铺面,就会选中整个形状。这样可能会超出到想要修改的区域之外;区域周边走线也会较为曲折。我们是否要删除整个 cline,再重新连接其他的线?是否会分段删除、减少

扫码关注

扫码关注