- 全部

- 默认排序

SQLite是一种强有力的嵌入式关系数据库,由D.Richard Hipp开发出来的,可实现数据库必备的一些基本功能。这种数据库在使用上市非常方便的也具有很多特征,在嵌入式培训时,也会学到和接触SQLite数据库的应用和技巧。

PIC单片机系列产品是英国微芯企业(Microship)的商品,共有三个级別,即基础级、初级、高級,是当今市场占有率提高更快的单片机之一,CPU选用RISC构造,各自有33、35、58条指令,属精减指令集,另外选用Harvard双结构,运作速度更快,它能使程序存储器的浏览和数据信息存储芯片的浏览并行计算,这类指令流水线结构,在一个周期时间内进行两一部分工作中

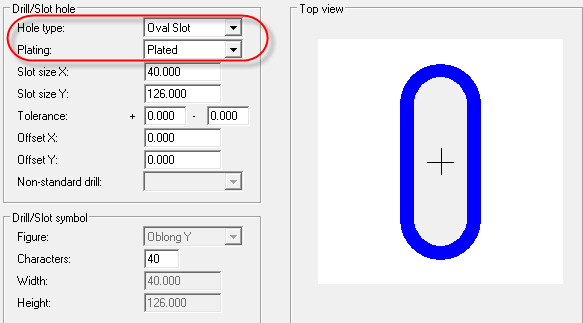

什么叫做槽孔?

槽孔,顾名思义,就是不规则的钻孔。我们常规的普通Dip的封装的钻孔都是圆形的钻孔,但是实际生活过程中,我们有些元器件的安装定位脚位是长方形或者椭圆形的,我们把这一类的不规则的钻孔统一称之为槽孔。在PCB的加工过程中,对于插件的钻孔有两种刀具,一种叫做钻刀,用来钻圆形的通孔,另外一种叫做铣刀,用来钻槽孔,槽孔在PCB看到的效果如图1-18所示。 图1-18 焊盘编辑器中槽孔示意在Allegro软件中,输出钻孔文件的时候,要特别注意,圆形钻孔的输出与槽孔的输出是不一致的,圆形的钻

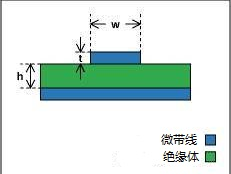

PCB中的信号线分为两种,一种是微带线,一种是带状线。 微带线,是走在表面层(microstrip),附在PCB表面的带状走线,如图1-43所示, 蓝色部分是导体,绿色部分是PCB的绝缘电介质,上面的蓝色小块儿是微带线(microstrip line)。由于microstrip line(微带线)的一面裸露在空气里面,可以向周围形成辐射或受到周围的辐射干扰,而另一面附在PCB的绝缘电介质上,所以它形成的电场一部分分

目前嵌入式开发的难度随着实验平台的不断发展而变得越来越容易,即使没有太多的硬件知识也可以进行嵌入式开发,这无疑降低了开发门槛,也促进了嵌入式开发的发展。通常情况下,实验平台都会自带操作系统和开发环境,在连接到PC之后就可以进行嵌入式开发了。目前,在嵌入式系统开发过程中使用的语言种类有很多,但仅有少数的几种语言得到了比较广泛的应用,主要有C语言、Python和JavaScript等几种。

1、深南电路:无锡封装基板工厂已有部分关键客户认证完成并进入量产状态 2、江西生益科技项目建设再提速 3、依顿电子:公司具备5G线路板生产能力 4、富士康在印度的iphone组装业务受清关延误被迫暂停 5、江西宏业铜箔:5G铜箔已满足目前国内高频高速的高端铜箔的使用要求

如果在提交Gerber文件给生产厂家的时候,同时生成ipC网表给厂家核对,那么在制板时就可以检查出一些常规的开路,短路的问题,可以避免一些损失。

Altium designer(后面简称AD)版本介绍从1985年Altium公司成立以来经历几个决定性的事件:1991年Altium公司将公司总部迁至美国并在发布了世界上首款基于Microsoft Windows运行的PCB设计系统;1999年Altium公司成功完成ipO并在澳大利亚证券交易所(ASX)上市;2013年Altium公司生产的首个原生3D软硬结合板电子设计系统问世。我主要讲一下Altium公司的AD产品。这是一款专门为硬件工程师开发设计的一款产品,但后期AD成为了一个包含硬件设

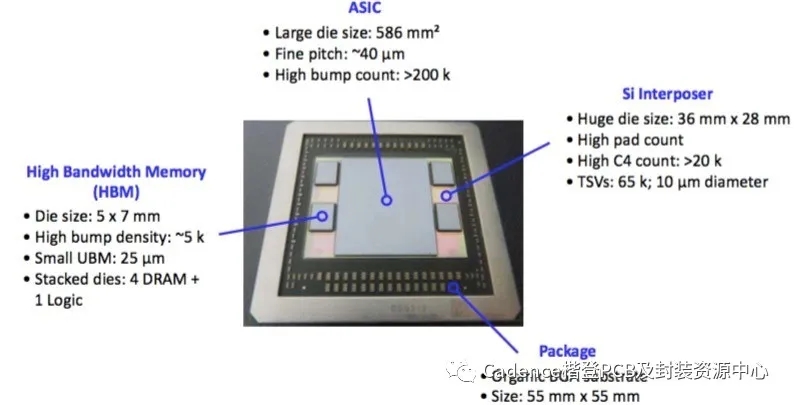

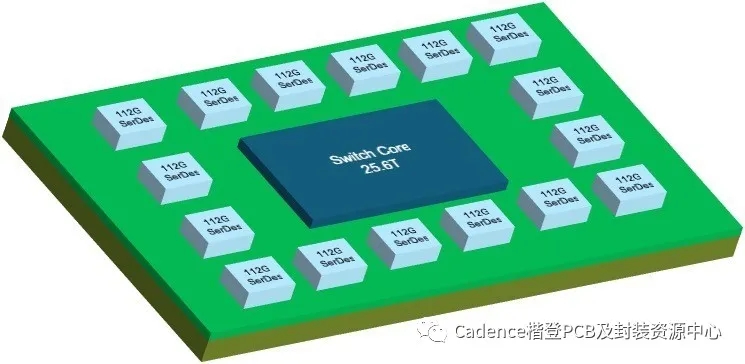

50多年来,半导体行业一直受益于摩尔定律。但是如今,半导体等比例缩小的时代已经结束。摩尔定律主要是作为一条经济法而存在——即集成电路上可容纳的晶体管数量,约每隔几年便会增加一倍。当然,是技术的发展使之成为现实;直到几年前,这一定律依然适用。高层次的经济主张是:每一代工艺将同一领域的晶体管数量增加一倍,成本仅增加15%,从而为每个晶体管节省35%的成本。但是因为当今的工艺愈发复杂,加之建造一个工厂的资本投入非常大(每台EUV步进机将耗资1亿美元),导致每一代晶体管都更加昂贵。因此我们发展出一个从7

HOT CHipS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是Intel的Lakefield芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用Intel的Foveros 3D技术组装。

扫码关注

扫码关注