- 全部

- 默认排序

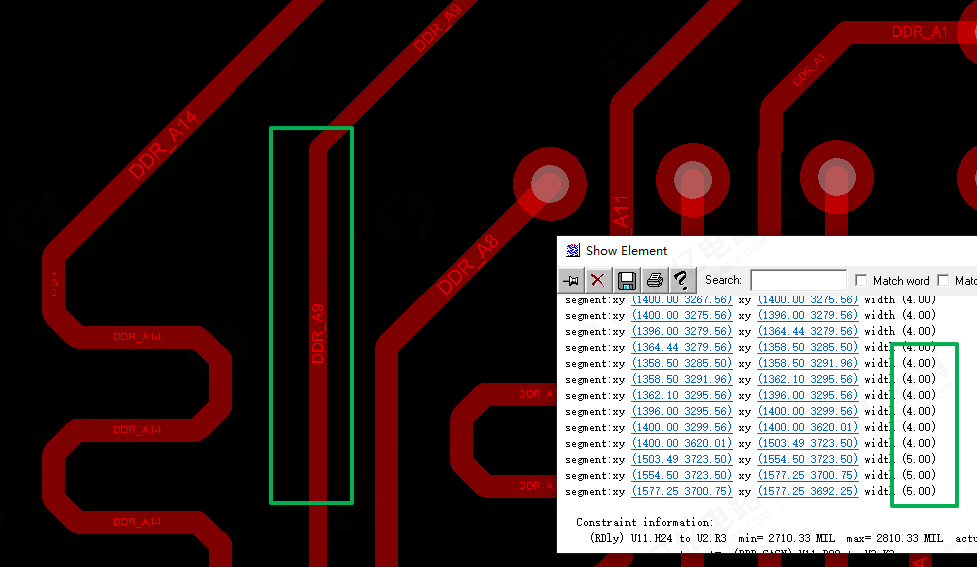

上次我们对不加端接电阻和加端接电阻之后的仿真结果做了分析之后我们得出在ddr采用菊花链拓扑结构的时候是需要加端接电阻的,这次我们看看ddr末端的端接电阻距离最后一片ddr远一点效果好一些还是近一点效果好一些。本次采用的案例依旧是我们上期的D

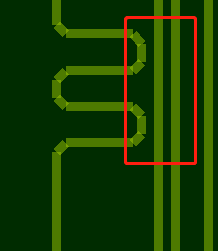

ddr3 2片:电感内部挖空处理。注意电源铺铜不要出现这种瓶颈处:等长线注意要保证3W间距,去调整出来:数据线需要满足等长误差,还存在报错:数据线也要满足3W间距自己注意走线跟过孔的间距规则:分割带尽量大于20MIL:以上评审报告来源于凡亿

DD3 四片:注意不要出现这种锐角走线:负片层并未赋予网络:注意设计完了之后检查下走线的连接性:并未保证3W间距原则:差分对内等长注意规范:差分对内等长误差为5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特

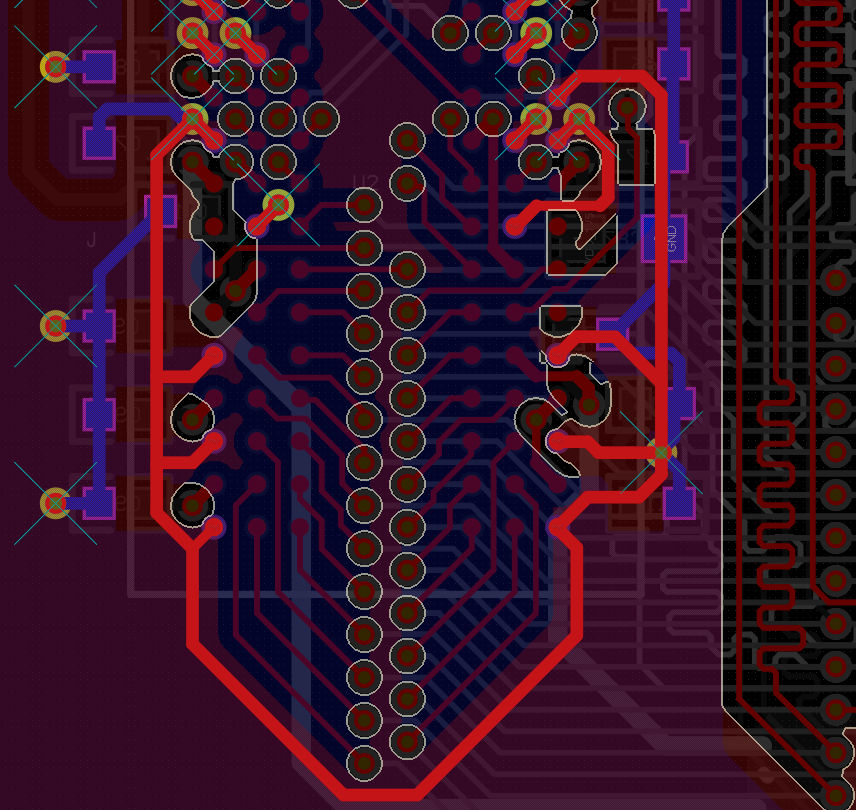

GND网络尽量就近打孔连接到地平面,尽量一个焊盘一个过孔后期自己优化一下器件摆放,地网络尽量靠近管脚差分出线要尽量耦合,后期自己优化一下差分对内等长误差5mil器件摆放间距不要太近,后期干涉不好焊接

个别线宽和其他走线不一致尽量避免小器件焊盘打孔等长绕线注意角度,部分绕线实际生产是直角以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com

此处不满足载流,后期自己铺铜处理一下,走线最少需要加粗到15mil以上载流计算都是以最窄处计算的2.注意数据线,地址线之间等长需要满足3W规则后期自己优化一下3.像此处的碎铜尽量挖空处理注意差分对内等长误差5mil其他没什么问题以上评审报告

走线需要优化,同网络的线也要保存3w差分对内不等长很多地方数据线不满足3w以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.

数据线线距不满足3w这里差分等长间距不能大于2Svref离数据线太近了以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.ht

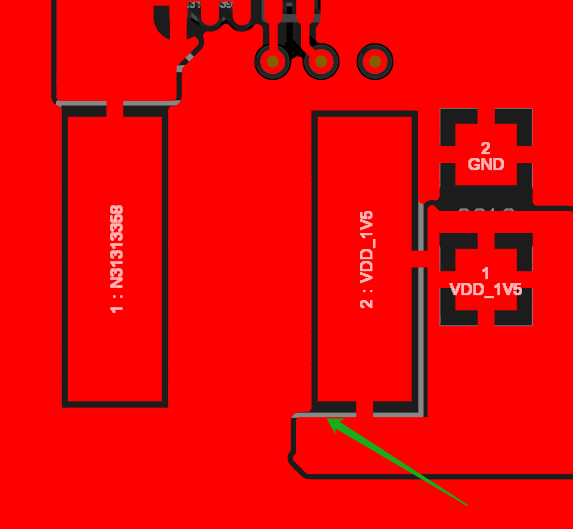

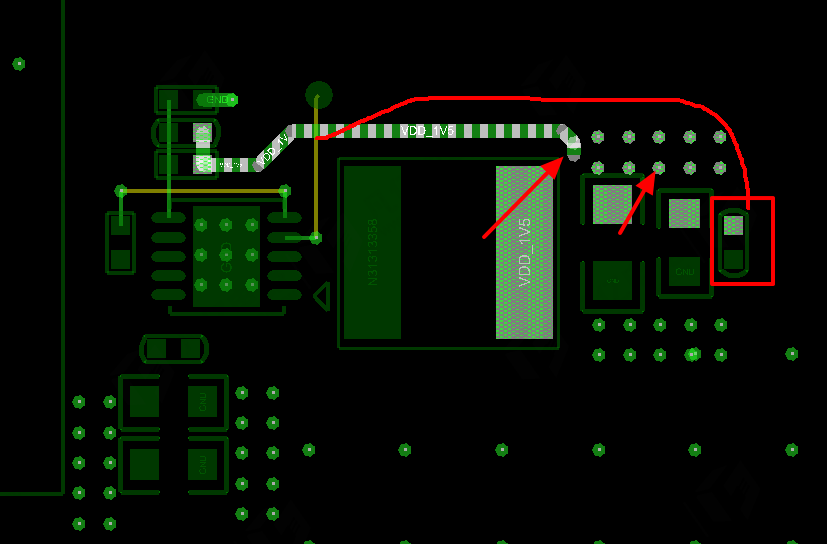

电源反馈信号要从最后一个器件连线,过孔要打到最后一个器件后方焊盘出线避免从长边出线布线保持3w间距规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.ta

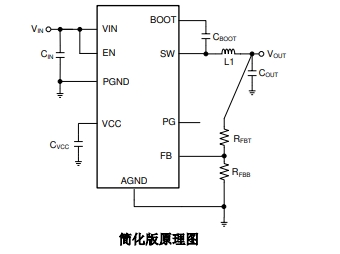

1、TPS53831RWZR用于 ddr5 服务器 DIMM 的高电流 PMICTPS53831 是适用于 ddr5 on-DIMM 电源的 D-CAP+™ 模式集成式降压转换器。该转换器具有可配置的电流范围,可为 DIMM 模块上的 DR

扫码关注

扫码关注