- 全部

- 默认排序

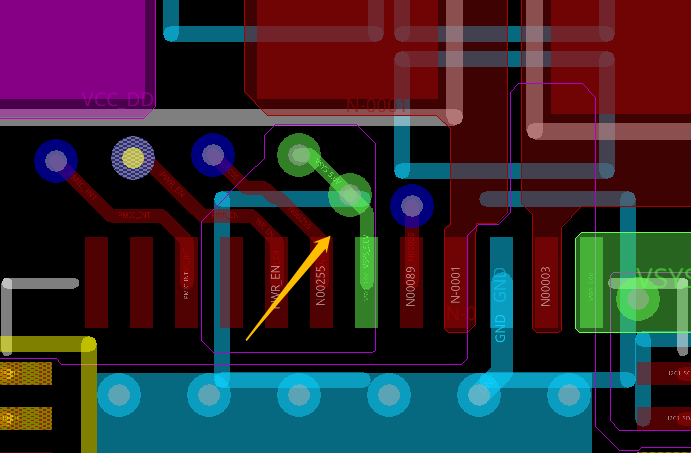

电感当前层的内部挖空处理:上述一致问题:注意不同地之间至少满足2MM间距:变压器信号除了差分信号,其他加粗20MIL走线:注意差分对内等长的GAP大于等于3W:焊盘扇孔注意对齐扇出:注意等长线之间满足3W间距原则可以调整下:注意的过孔之间的

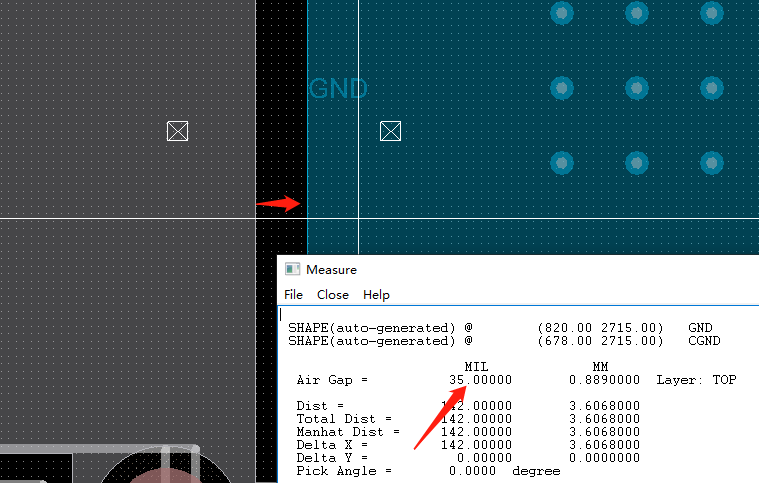

注意电源地跟机壳地之间满足至少2MM间距:器件注意放置完全,并且放置完成之后走线连接:把没有设计的器件布局布线设计下。变压器除了差分信号,其他信号也要走线连接完全:还存在多处飞线,存在信号没有连接完全:等长线之间需要满足3W间距:注意等长还

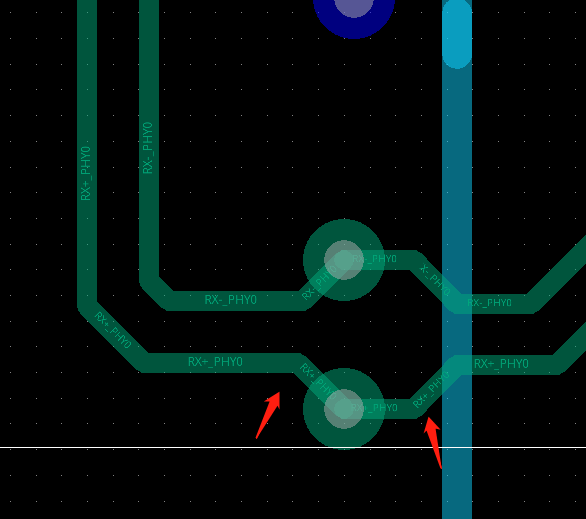

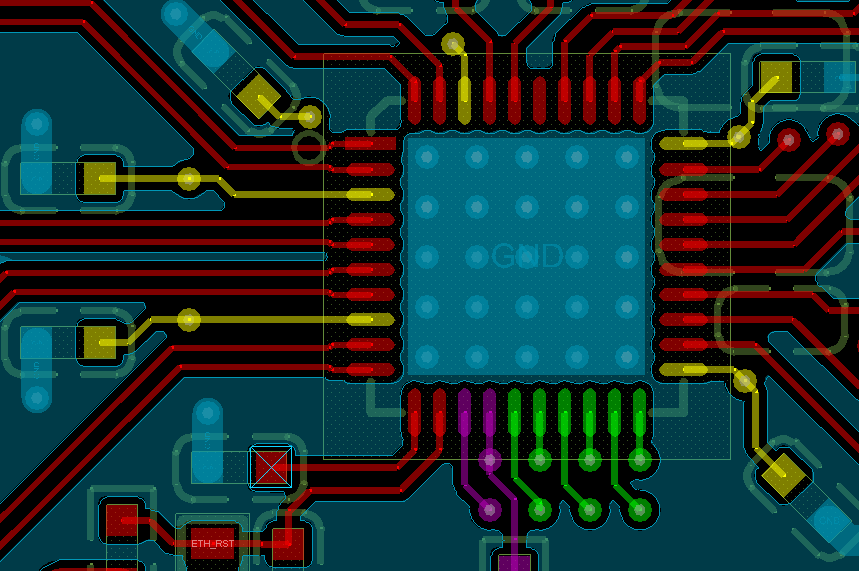

注意差分走线,此处的右边调整为左边形式走线:注意地网络顶层也没铺铜,GND层也没有进行负片分割,需要重新设计:PWR层也没有设置负片层进行分割或者是正片铺铜,建议重新设计下:电源跟地都没有处理。TX RX没有设置MGROUP等长:差分需要对

分割地之间的间距最少要1mm以上2.晶振需要走内差分,并包地3.焊盘中心出线至外部才能拐线处理,避免生产出现虚焊,走与焊盘同宽拉出来再进行加粗4.变压器除擦还分信号外,其他的都需要加粗到20mil5.变压器需要所有层挖空以上评审报告来源于凡

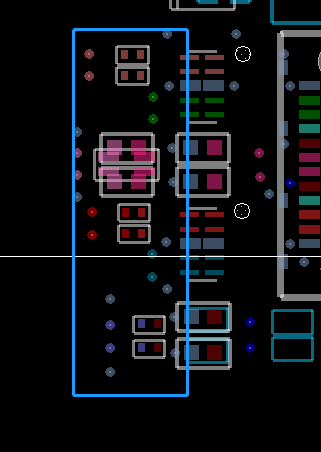

注意电感当前层的内部铜皮挖空:焊盘扇孔注意下对齐扇出:上述一致问题,优化下电感内部的挖空区域:个别信号没有联通:其他的没什么问题。

机壳地以及电源地没有正片铺铜处理也没有负片分割处理,注意地是需要处理的:变压器上除了差分信号,其他的加粗20MIL走线:电源层也并未处理电源 :TX RX信号之间用GND走线隔开:RX TX没有创建等长组进行等长:差分对内等长误差为5MIL

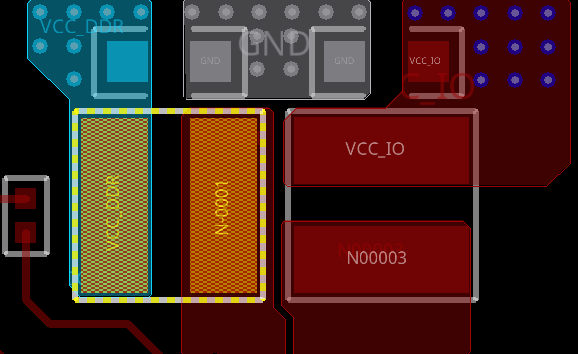

此处DCDC5.0V线宽满足不了载流:电感内部放置铜皮挖空区域,进行内部挖空:注意LDO电源的器件尽量整体中心对齐下:扇孔注意下对齐:看下此处的VCC-IO线宽是否能满足载流:器件注意对齐:以上评审报告来源于凡亿教育90天高速PCB特训班作

此处电源走线要注意满足载流2.晶振需要走内差分,并包地处理3.器件摆放不要挡住一脚标识4.注意等长线之间需要满足3W5.注意电源要满足载流6.变压器要所有层挖空处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班

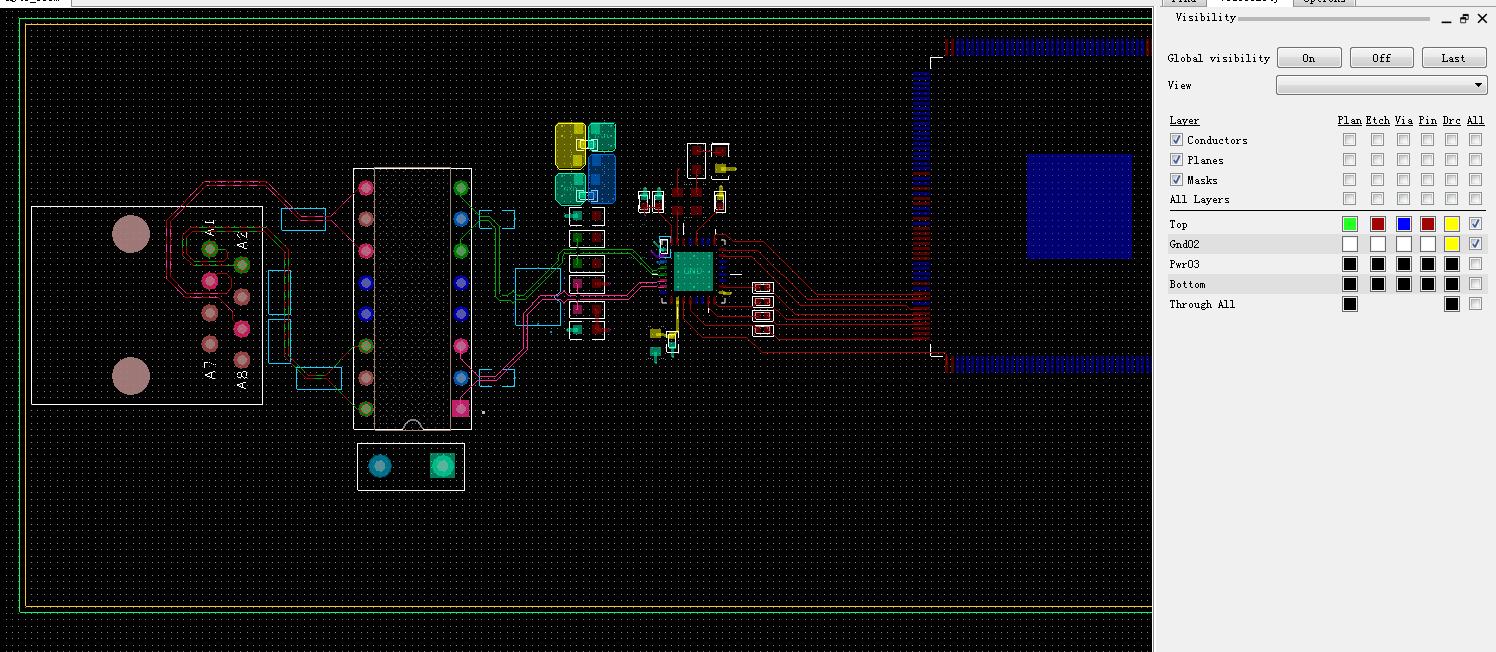

在PCB设计中,层叠结构的设置对于电路性能和信号完整性至关重要,对电子工程师来说,如何通过EDA工具来设置电路板的层叠结构不出差错,是一项重要且困难的任务,下面将谈谈如通过allegro设置电路板的层叠结构,包括层的选择、堆叠顺序、电源与地

注意器件尽量整体中心对齐:上述一致问题,器件整体对齐处理:注意差分打孔换层的回流地过孔,打在正左右两侧,调整下:注意差分从过孔拉出,前两组调整为第三组的模式:此处电源信号并未连接:注意差分对内等长误差为5MIL:其他的没什么问题。以上评审报

扫码关注

扫码关注

![全能19期-allegro_THE的_第三次作业[2]千兆网卡PCB设计](https://api.fanyedu.com/uploads/ueditor/image/20230711/1689056641694508.png)