- 全部

- 默认排序

有没有人注意到,在探讨数据中心服务器的硬件选择,很多人都不会选择FPGA(现场可编程门阵列),甚至会主动避免,这是为什么?针对这个问题进行探讨!1、编程门槛高FPGA的编程需要使用硬件描述语言(如VHDL、VERILOG),这些语言与软件开

VERILOG作为一种硬件描述语言(HDL),在FPGA开发、IC设计等领域具有广泛应用。为了编写出高效、可综合的VERILOG代码,开发者需要掌握一些具体而实用的编写建议。1、明确硬件实现概念理解硬件结构:在编写VERILOG代码前,需清

在VERILOG代码编写过程中,准确区分可综合与仿真语句是至关重要的。这不仅能够确保代码在硬件实现中的正确性和效率,还能在仿真阶段有效地验证设计功能。1、理解可综合语句可综合语句是指那些能够被综合工具(如FPGA综合器或ASIC综合器)转化

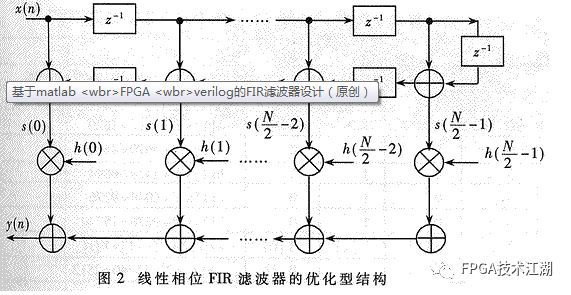

今天和大侠简单聊一聊基于matlab FPGA VERILOG的FIR滤波器设计,话不多说,上货。本次设计实现8阶滤波器,9个系数,由于系数的对称性,h(0)=h(8),h1(1)=h(7),h(2)=h(6),h(3)=h(5),h(4)为中间单独一个系数。根据公式:实现框图:推导出当系数N为偶数

.h .h用于告诉别人你的程序是用来做什么,一般应包括一些宏定义和变量,函数声明。(强调:接口,功能) .v .v文件是所有函数和变量的定义,用于告诉计算机,你的程序要做什么。 (强调:结构,实现)

我的乘法已经写了好久了,但是一直改来改去,今天终于完成了算是比较标准的一个程序吧,我把所有端口的宽度都用一个变量来表示,到时候直接改动变量的值就可以了。。。 之前,我给变量赋值的语句是这么写的: parameter e1=4'd8;///表示成数的指数位数//// parameter e2=4'd8

扫码关注

扫码关注