- 全部

- 默认排序

一、课程详情本次4 层 PADS DSP 芯片主控设计课程是一个难度适中的基于 DSP 芯片为主芯片的 4 层高速 PCB 设计项目,项目中涉及了 DSP、FPGA 芯片,使用了 SDRAM、FLASH、SRAM 等高速存储器模块。

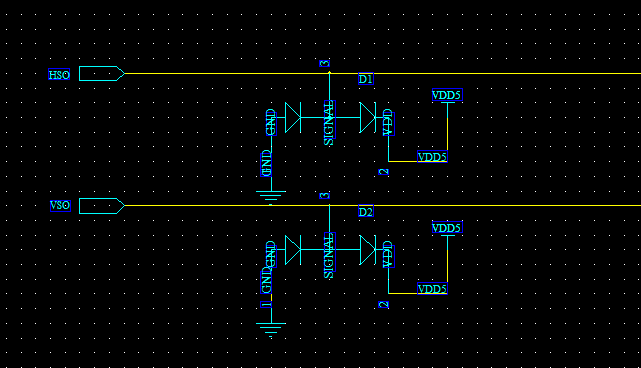

ESD、EMI、EMC设计是电子工程师在电子设计中遇到常见难点,电磁兼容性(EMC)就是指机器设备或系统软件在其电磁自然环境中符合规定运作并不对其自然环境中的一切机器设备造成难以忍受的电磁干扰的工作能力。因而,EMC包含2个层面的规定:一方面就是指机器设备在一切正常运作全过程中对所属自然环境造成的电磁干扰不可以超出一定的限制值;另一方面就是指器材对所属自然环境中存有的电磁干扰具备一定水平的抗扰度,即电磁敏感度。说白了电磁干扰就是指一切

Micro SD卡是一种极细小的快闪存储器卡,其格式源自SanDisk创造,原本这种记忆卡称为T-Flash,及后改称为Trans Flash;而重新命名为Micro SD的原因是因为被SD协会 (SDA) 采立。另一些被SDA采立的记忆卡包括Mini SD和SD卡。其主要应用于移动电话,但因它的体积微小和储存容量的不断提高,已经使用于GPS设备、便携式音乐播放器和一些快闪存储器盘中。

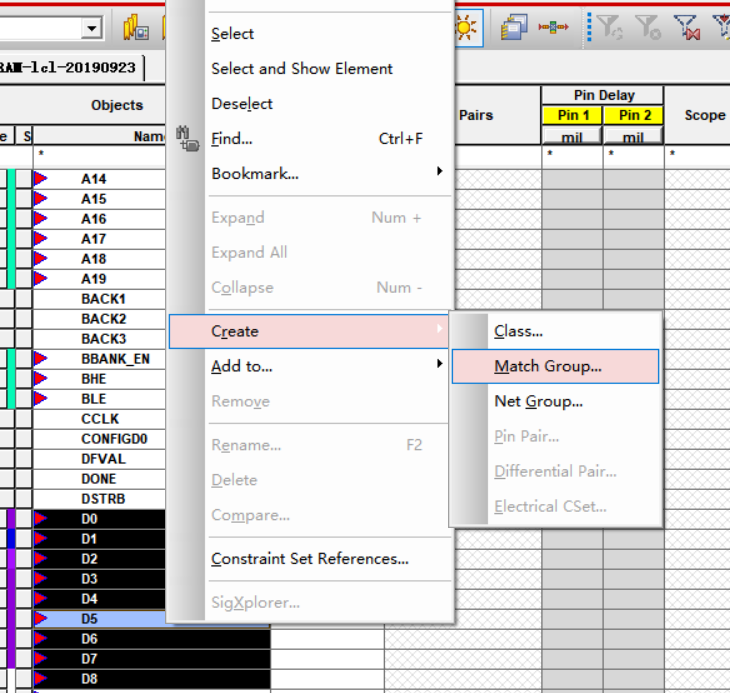

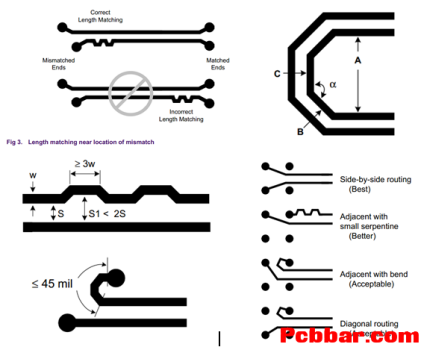

SDRAM信号线等长处理

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

开关电源eSD测试教程

1. 开关电源的几种保护OCP, OLP, OVP, OTP, ESD,UVLO分别是什么意逐周期电流限制保护(OCP),限制最大输出电流;过载保护(OLP),限制最大输出功率;VDD过压保护(OVP),限制最高输入电压;温度保护(OTP),限制工作时的最高温升;ESD静电保护,即静电释放,避免由于静电引起芯片或者电子元件损坏;以及低压关闭(UVLO),欠压锁定,限制最低入输入电压。过压保护开关和过载保护开关有什么区别?1、负载如果是阻性负载,当电源有故障,负载上的电压有可能大幅上升,而电流的上

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

英飞凌OptiMOS?源极底置功率MOSFET系列新添PQFN封装的40 V装置-OptiMOS SD 40 V低电压功率 MOSFET 提供两种版本:标准版和中央栅极版。中央栅极版针对多部装置并联作业进行了优化。

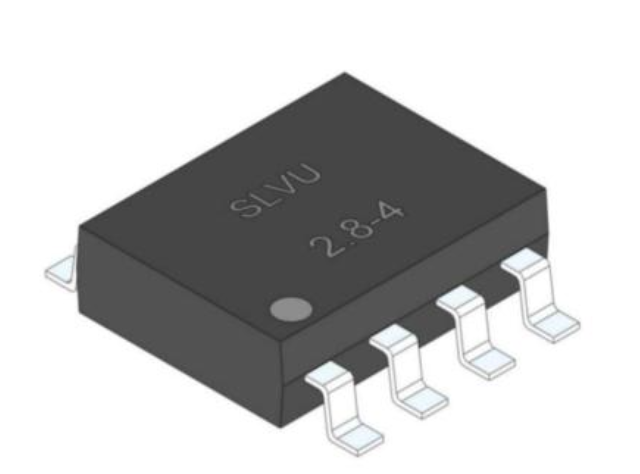

Littelfuse全新50A单向瞬态抑制二极管阵列系列适用于消费类电子产品-SP1250分散式单向瞬态抑制二极管采用专有的硅雪崩技术制造。该二极管阵列可为消费电子设备提供高ESD(静电放电)保护。

扫码关注

扫码关注