- 全部

- 默认排序

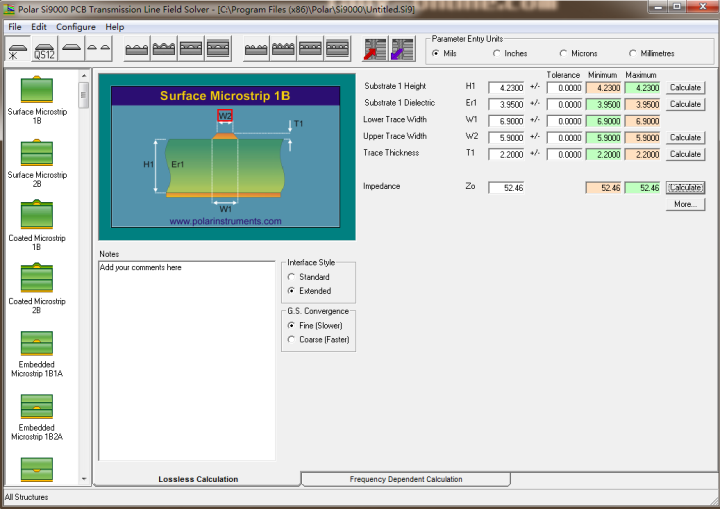

特性阻抗,体现在PCB板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对PCB板进行层叠设计,将PCB板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗线宽的计算,然后根据计算好的线宽来进行布线,即可达到控制特性阻抗的效果。如图1-21所示,1.6MM的厚度的PCB板的层压结构。TOP0.5oz +PlatingPP(2116)4.23GND021ozCore20.08ART031ozPP(1080*2)4.59PWR041ozCore20.08GND0

答:特性阻抗,体现在PCB板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对PCB板进行层叠设计,将PCB板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗线宽的计算,然后根据计算好的线宽来进行布线,即可达到控制特性阻抗的效果。如图1-21所示,1.6MM的厚度的PCB板的层压结构。TOP0.5oz +PlatingPP(2116)4.23GND021ozCore20.08ART031ozPP(1080*2)4.59PWR041ozCore20.08GN

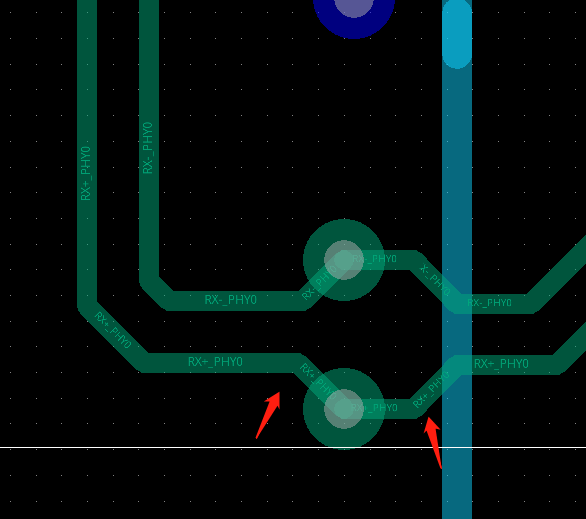

注意差分走线,此处的右边调整为左边形式走线:注意地网络顶层也没铺铜,GND层也没有进行负片分割,需要重新设计:PWR层也没有设置负片层进行分割或者是正片铺铜,建议重新设计下:电源跟地都没有处理。TX RX没有设置MGROUP等长:差分需要对

这个导入进来就是这样的,正在PCB摆放器件,规则还没改,类里面就添加了一个PWR。MCU和USB引脚都是绿色,看看是哪的问题。

老师,还有个问题想问下。4层板上有混合信号的话,在板子顶、底层是需要分割数字地、模拟地。那么内电层,第二层GND也需要分割吗?然后在顶层的一个位置,把数字地、模拟地连接起来?第三层电源层需要分割嘛?我看有的板子是把第三层PWR模拟部分也作为模拟地了

老师,这条GND线我已经设置成PWR类,然后我规则里也设置了PWR类的线宽最小10,最大60,为什么我连线的时候设置线宽为15的时候一直报错呢

IC器件的VCC引脚要不要直接打过孔到PWR电源层,还是导线连上电容后再从电容那里打孔到电源层像图上这样,就是直接IC打过孔接到电源层,不知道能否起到电源滤波作用?

扫码关注

扫码关注