- 全部

- 默认排序

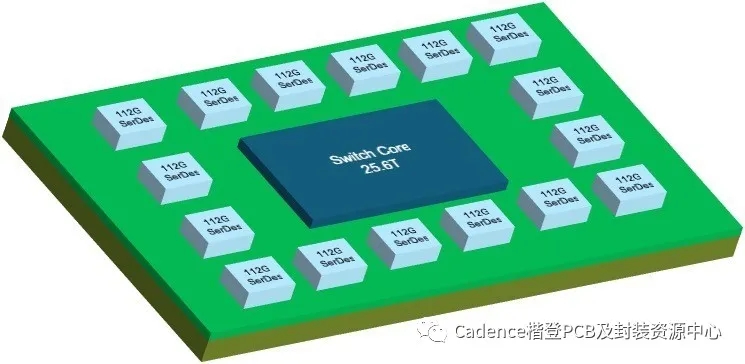

HOT CHIPS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是Intel的Lakefield芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用Intel的Foveros 3D技术组装。

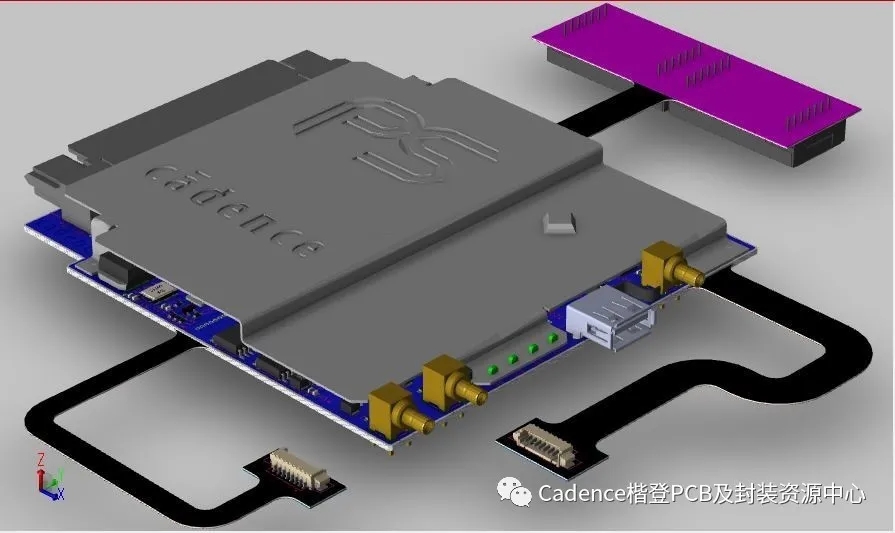

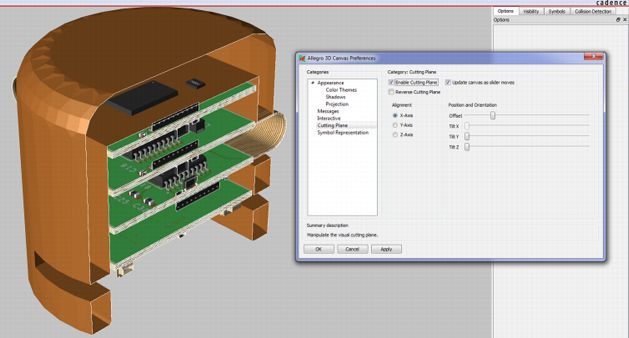

在Allegro17.4版本中,视图菜单中有两个3D绘制工具——3D Viewer和3D Canvas:

Allegro的全称是CadeNCe Allegro PCB Designer,是CadeNCe公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

Allegro的全称是CadeNCe Allegro PCB Designer,是CadeNCe公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

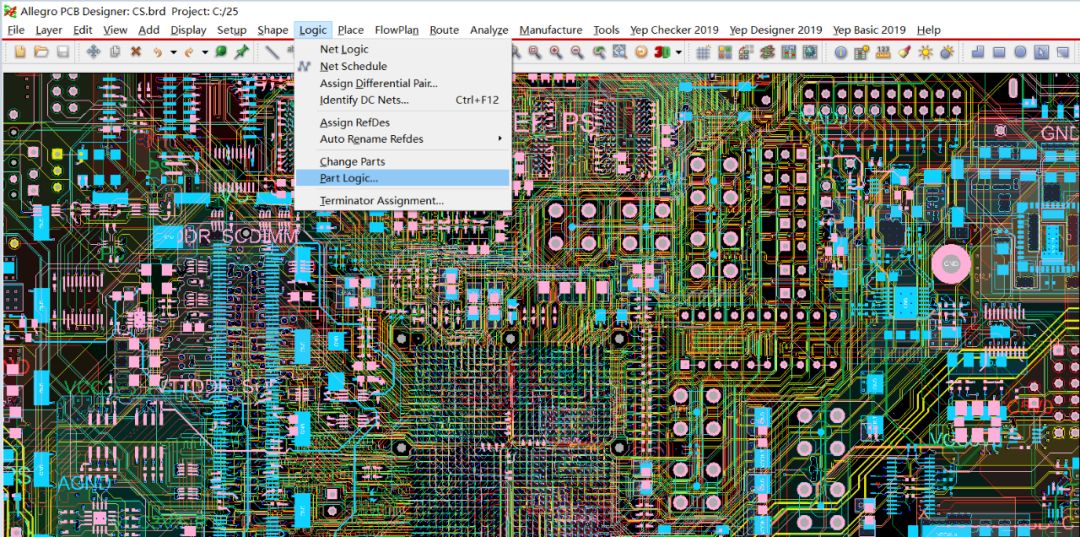

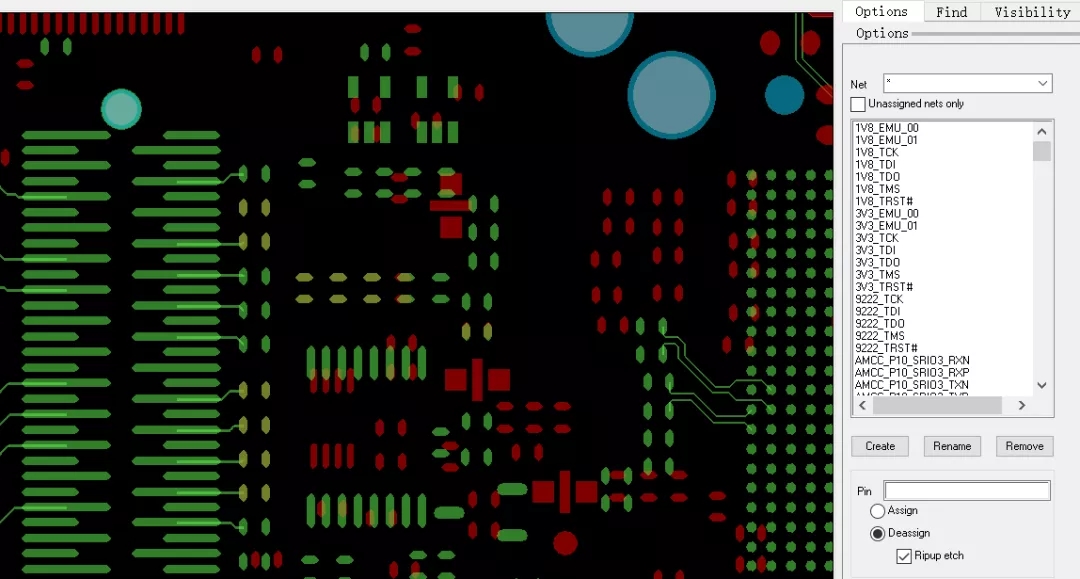

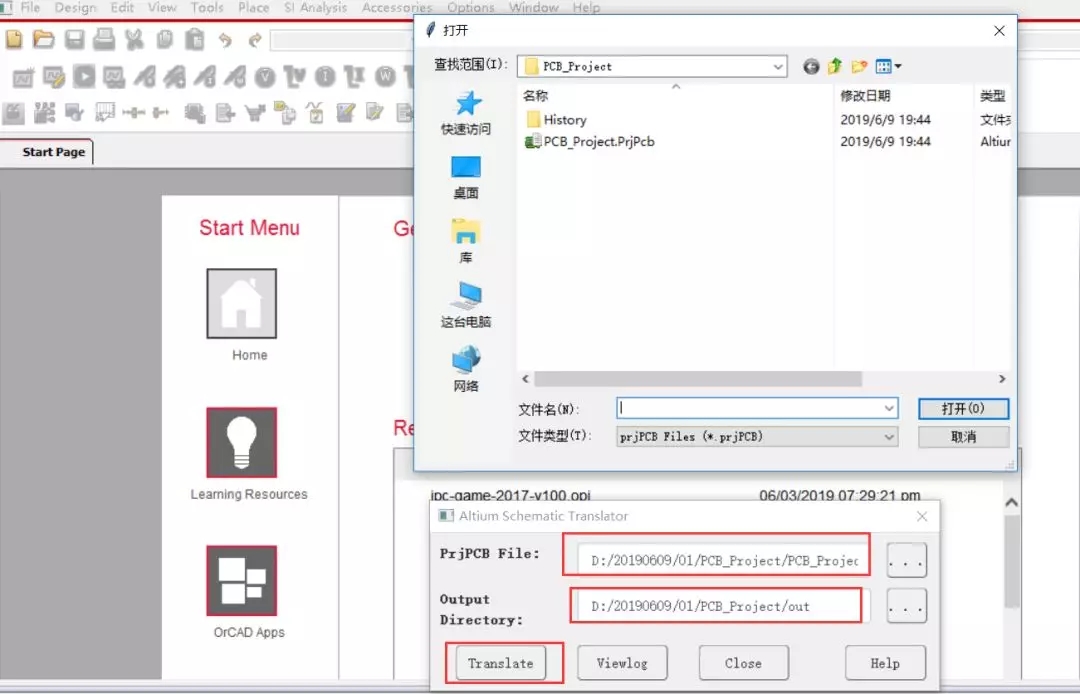

在项目实际的设计中我和小伙伴一样都遇到过很多麻烦的问题,有些时候原理图和PCB设计可能是由不同的工程师负责,由于种种原因可能需要在没有原理图的情况下直接对PCB进行操作。如更新元件封装和增加与删除元件等操作。接下来我们一起学习

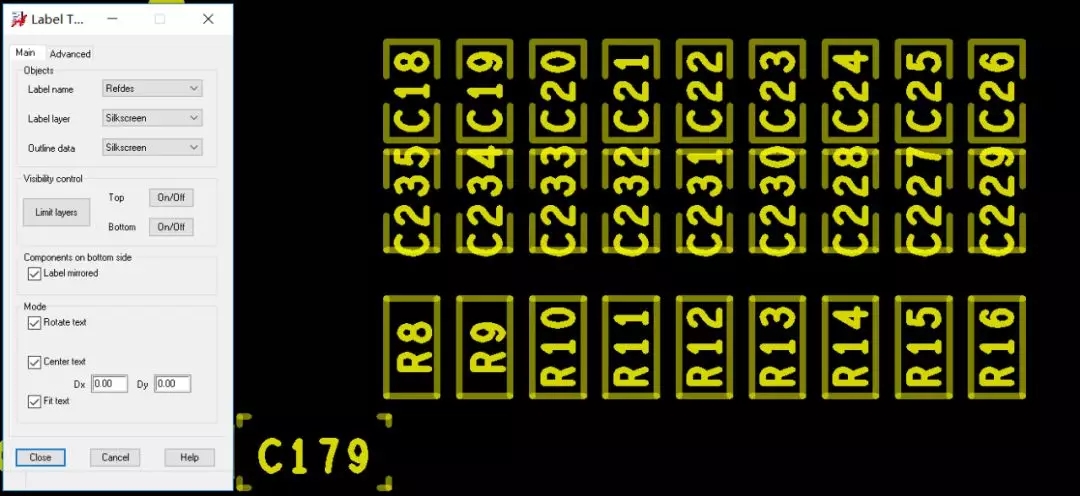

Allegro Productivity Toolbox组件所带来了很多高级命令,今天我们一起学的Label Tune就是其中一个。Label Tune是用来做批量的元件字符对齐操作的命令,可以支持对丝印、显示、装配层的字符对齐操作。我们知道PCB设计里面,丝印可以给贴片和识图的工程师提供一个位置参考,可以让工程师能够快速的找到元件在PCB上的位置。如下图所示,这样整齐的丝印排列可以让工程师快速定位元件位置。

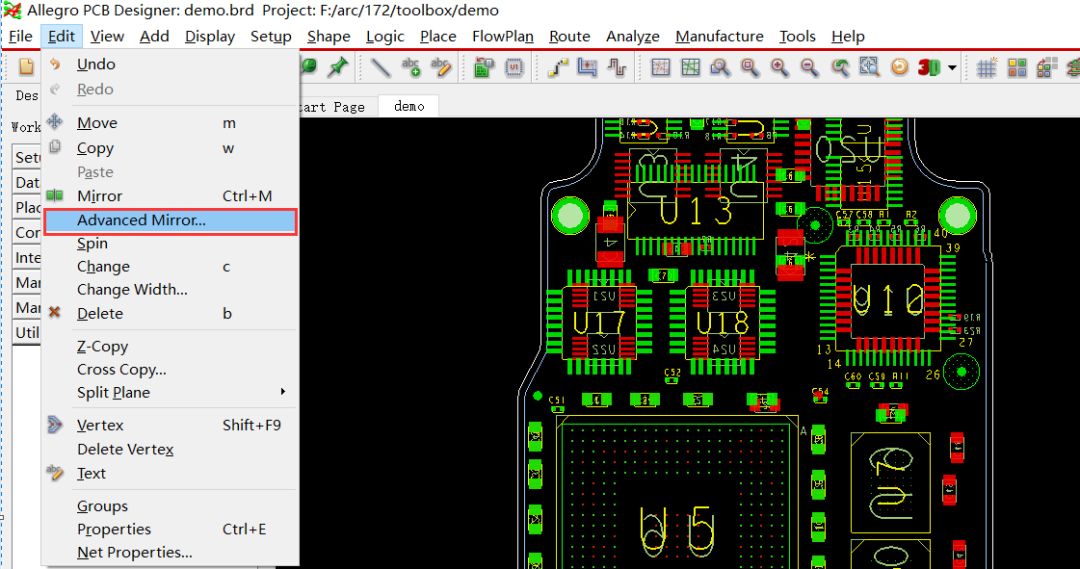

Allegro PCB Designer是一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。 在这个专题中,我们将介绍在该套件下的一个Toolbox选项组件下的AdvaNCed Mirror高级镜像功能。

各位小伙伴大家好,CadeNCe Allegro 软件一直以来,都能够支持3D PCB的模型制作和预览功能,但是一直以来立体感和视角的效果都不够理想。为了能够给工程师更加直观的PCB立体设计体验,CadeNCe做了很大的努力。从Allegro 17.2开始,Allegro已经能够支持立体的三维PCB设计和交互预览功能,能够让工程师在三维模式下进行交互Layout。今天我们将来一起体验学下逼真的3D功能吧。

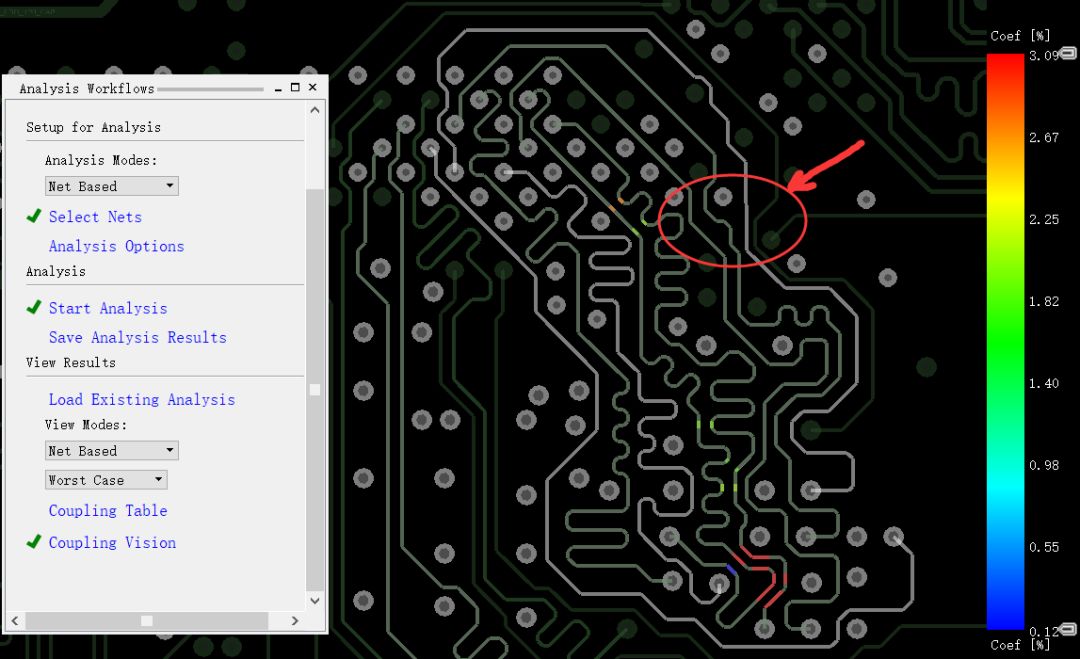

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

OrCAD Capture作为行业标准的PCB原理图输入方式,是当今世界最流行的原理图输入工具之一,具有简单直观的用户设计界面。不管是用于设计模拟电路、复杂的PCB、FPGA和CPLD、PCB改版的原理图修改还是用于设计层次模块,OrCAD Capture都能为设计师提供快速的设计输入工具。

扫码关注

扫码关注