- 全部

- 默认排序

HOT CHIPS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是Intel的LakefieLD芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用Intel的Foveros 3D技术组装。

随着数字电路应用领域越来越多,可编程逻辑器件(Programma Logic Device,PLD)在其带动下也成为大火的电子器件之一,这也促使了PLD芯片制造工艺的日益完善,所以我们接下来将盘点可编程逻辑器件PLD芯片制造工艺。可编程逻辑

随着微电子技术的发展,FPGA逐渐替代PDL等可编程逻辑器件应用在各个领域,但CPLD因其独特的特点性质,仍然比FPGA更适合应用在部分领域,但由于很多小白没装没接触过CPLD芯片,也不清楚其结构,所以本文将探讨CPLD芯片的内部结构。CP

LD芯片的工艺制作流程

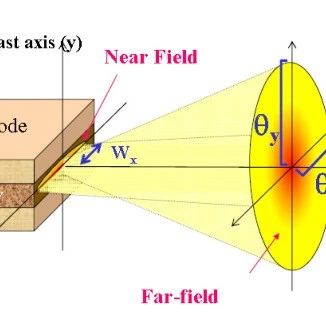

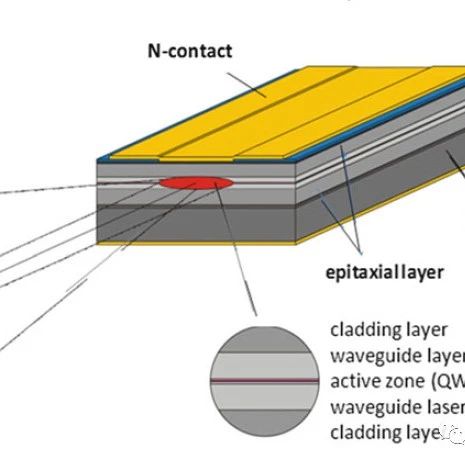

脊型GaAs基LD激光芯片工艺过程:这个流程算是LD最基础的流程,第一步做Mesa台阶,第二步做SiO2阻挡层,第三步做P电极、第四步做减薄、抛光;第五步做N电极。然后就是切片、测试、封装。但是里面也有几个关键的工艺参数需要控制的。同样Etch GaAs也可以用ICP干法刻蚀的工艺,比湿法工艺效果要

激光器芯片的WPE思考

WPE在LD芯片中指电光转换效率。 WPE=出光功率/工作电流/工作电压。因此WPE越大越好,说明电转成光的效率越高。额外的部分电能,大部分以热能的形式释放。WPE高的话,转换的热也会变少。 An AlGaInP/GaAs red LD suffers from low wall pl

高功率二极管LD失效特性

LD具有高转换效率,体积小,可靠性高等特点被广泛应用,但是高功率LD芯片制造工艺复杂,价格贵,外延、芯片、封装等的缺陷影响着器件的成品率。 激光器的失效模式1 主要失效特性LD失效的三个时间段: 早期失效、偶然失效、损耗失效早期失效的原因:芯片制造工艺缺陷、焊接失效、芯片端面绝缘层失效。损耗失

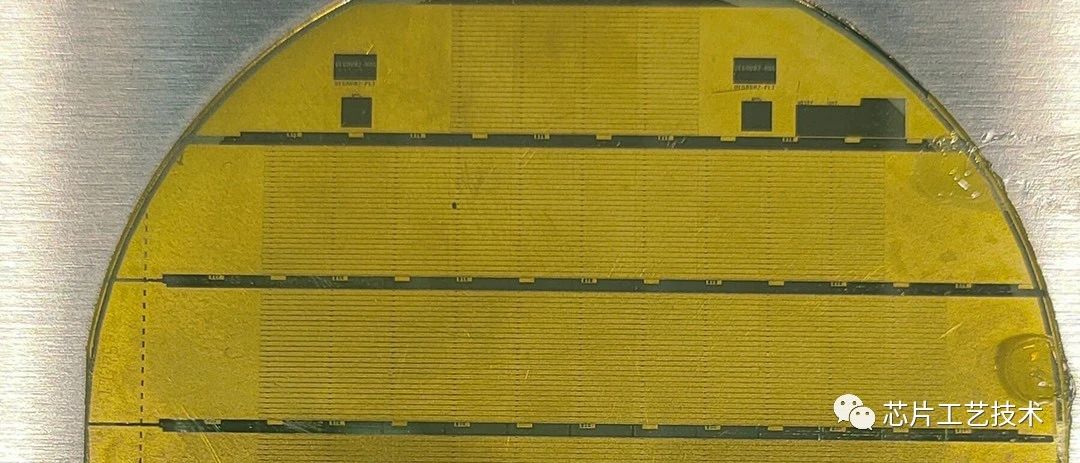

分享几个LD芯片设计的产品图。Laser chip在制造过程中由于要切bar条镀膜,所以要先分成一个一个的bar条,因此在设计上不同于常规wafer。第一幅图是一个3inch LD wafer,看得出wafer在刻图前做了二次晶向校准。图案分两个主部分和三个附部分。bar条的长度预计25mm-30m

扫码关注

扫码关注