- 全部

- 默认排序

ALtium designer(后面简称AD)版本介绍从1985年ALtium公司成立以来经历几个决定性的事件:1991年ALtium公司将公司总部迁至美国并在发布了世界上首款基于Microsoft Windows运行的PCB设计系统;1999年ALtium公司成功完成IPO并在澳大利亚证券交易所(ASX)上市;2013年ALtium公司生产的首个原生3D软硬结合板电子设计系统问世。我主要讲一下ALtium公司的AD产品。这是一款专门为硬件工程师开发设计的一款产品,但后期AD成为了一个包含硬件设

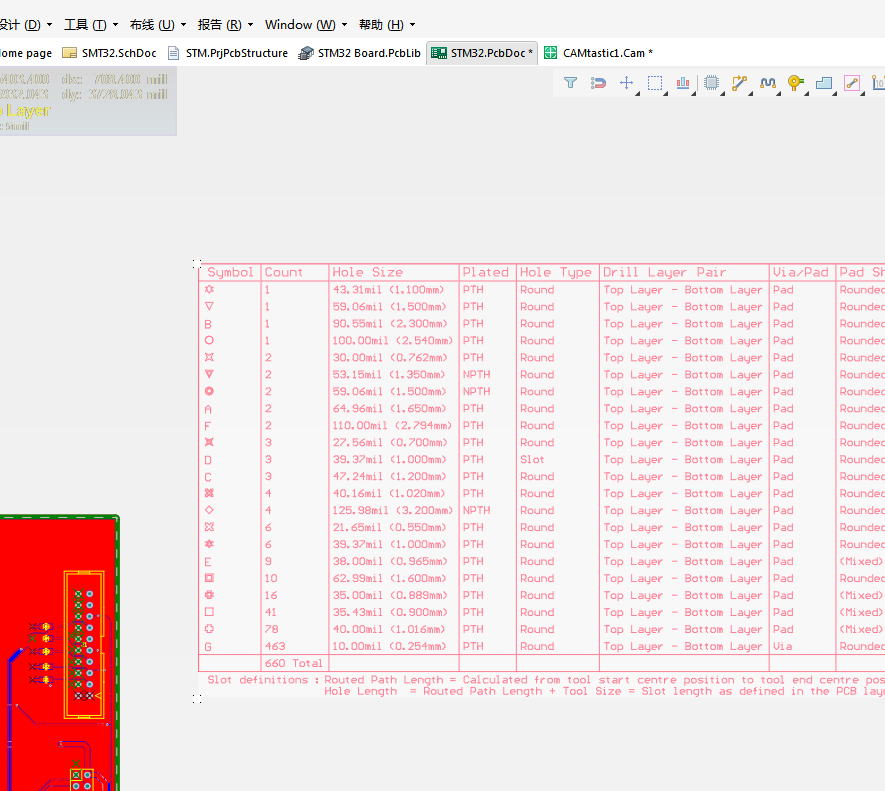

AD20在导出Gerber的时候,DirLL Drawing层的“.Legend”出现Legend is not interpreted untiL output (即使在最终的输出也没有变化)。导致导出Gerber时并没有对应的显示标识。这个问题在高版本中最常见,通常是在放置钻孔表时,对应的选项没有进行设置。

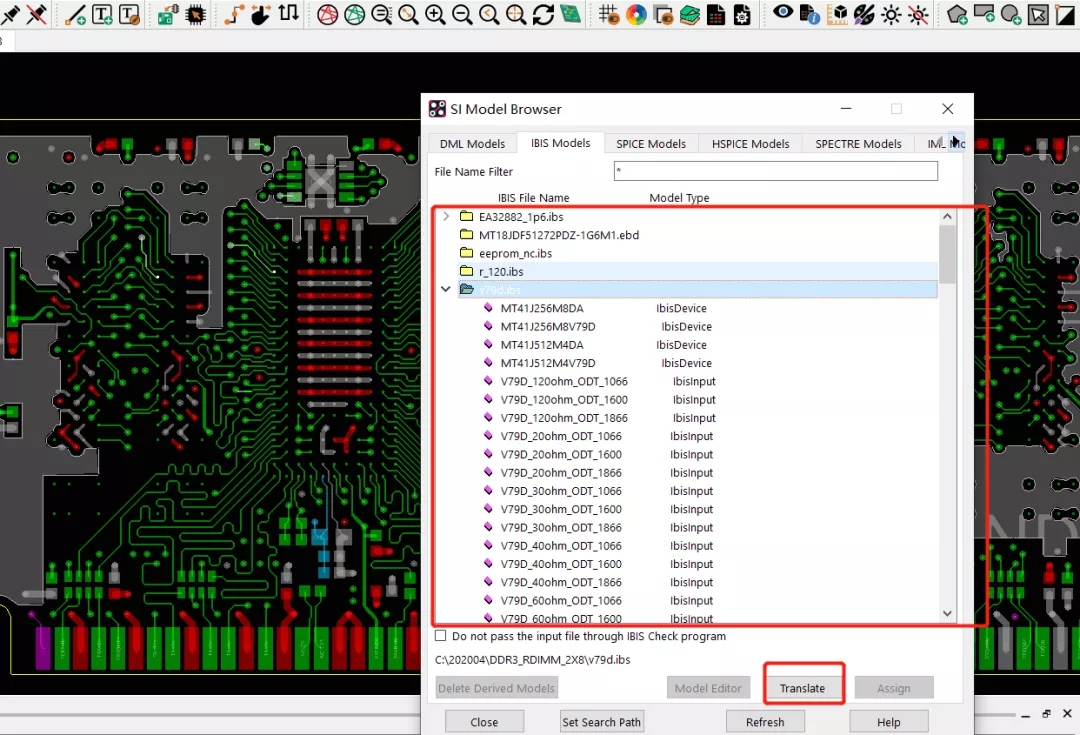

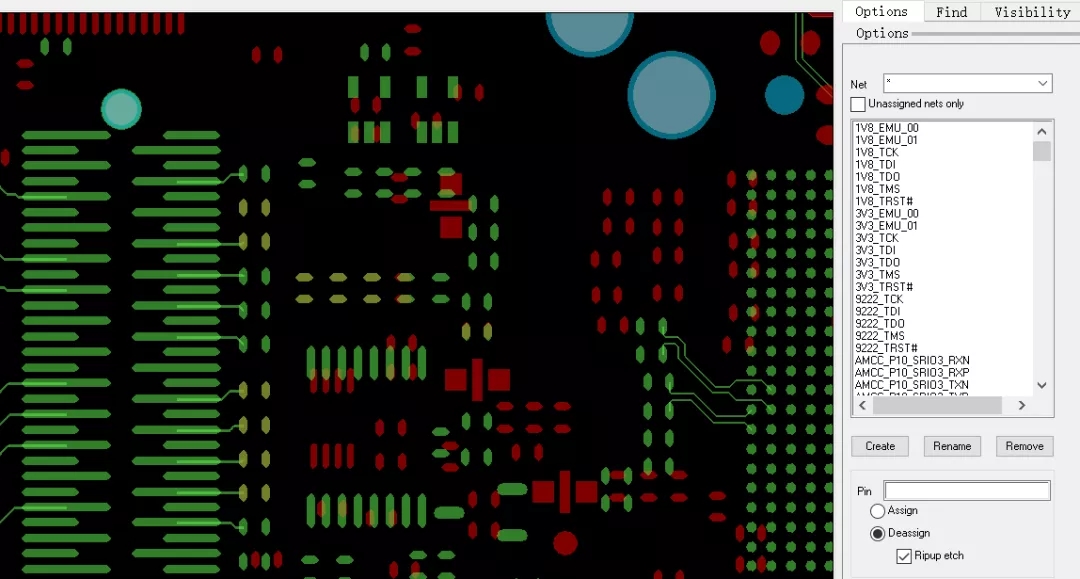

ALLegro的全称是Cadence ALLegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。ALLegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。ALLegro是我们目前高速PCB设计中使用最多的工具。

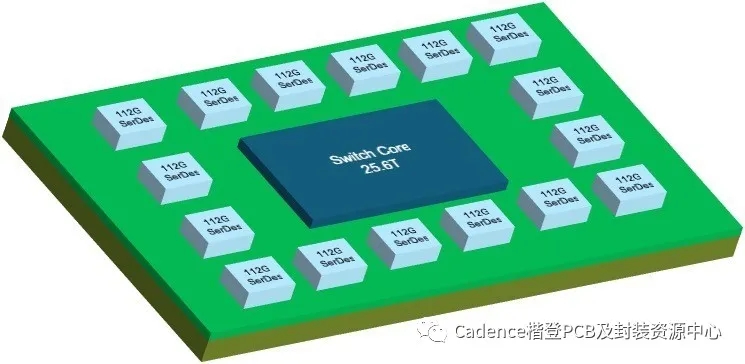

HOT CHIPS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是InteL的LakefieLd芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用InteL的Foveros 3D技术组装。

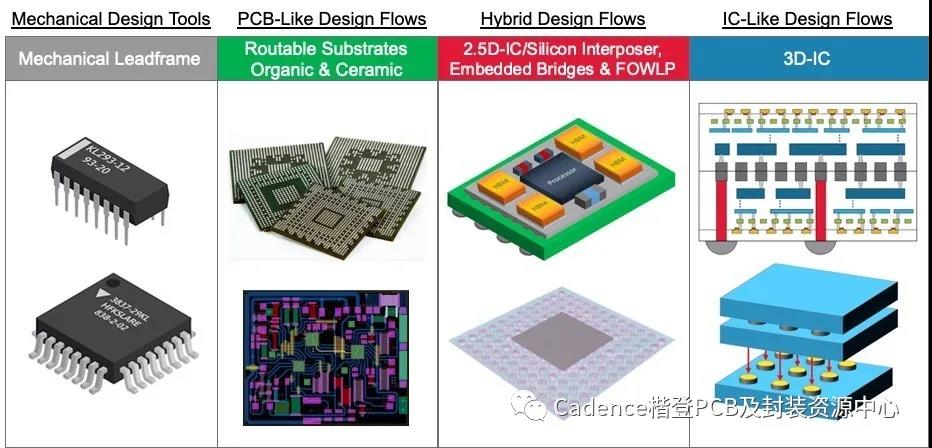

封装设计有许多处理方法: 采用以机械引线框设计封装本身 采用可布线的有机和陶瓷基板设计封装,这是一种PCB风格的设计流程 设计2.5D硅中介层、嵌入式桥和扇出型晶圆级封装(FOWLP)的混合设计流程 采用集成电路类设计流程设计具有硅穿孔(通常)的3D集成电路

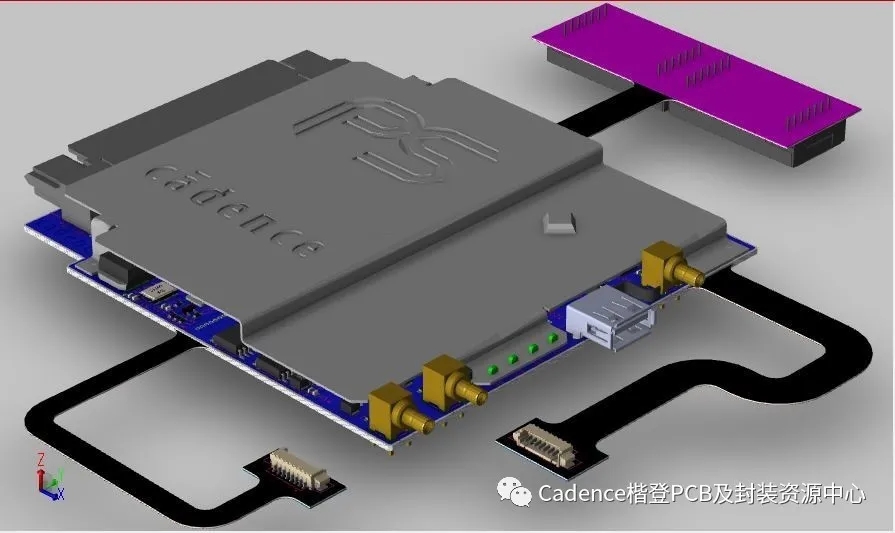

在ALLegro17.4版本中,视图菜单中有两个3D绘制工具——3D Viewer和3D Canvas:

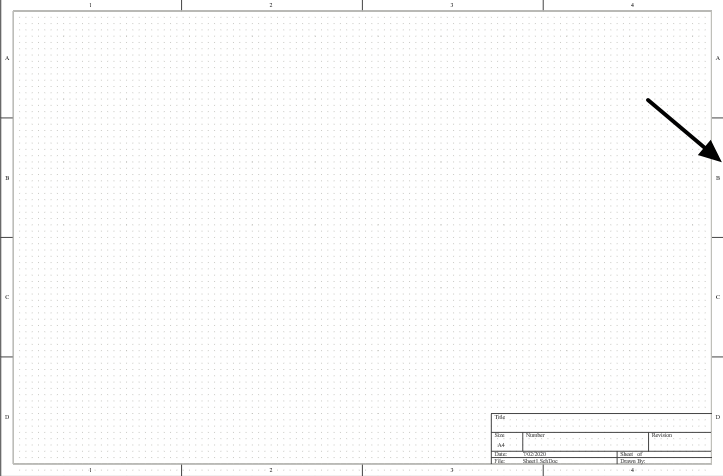

AD原理图默认右下角有TitLe bLock框存在,在里面可以设置项目名称,日期等属性,但是在不需要时为了更加方便绘制原理图如何将其隐藏呢?

ALLegro的全称是Cadence ALLegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。ALLegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是ALLegro)。

ALLegro的全称是Cadence ALLegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。ALLegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是ALLegro)。

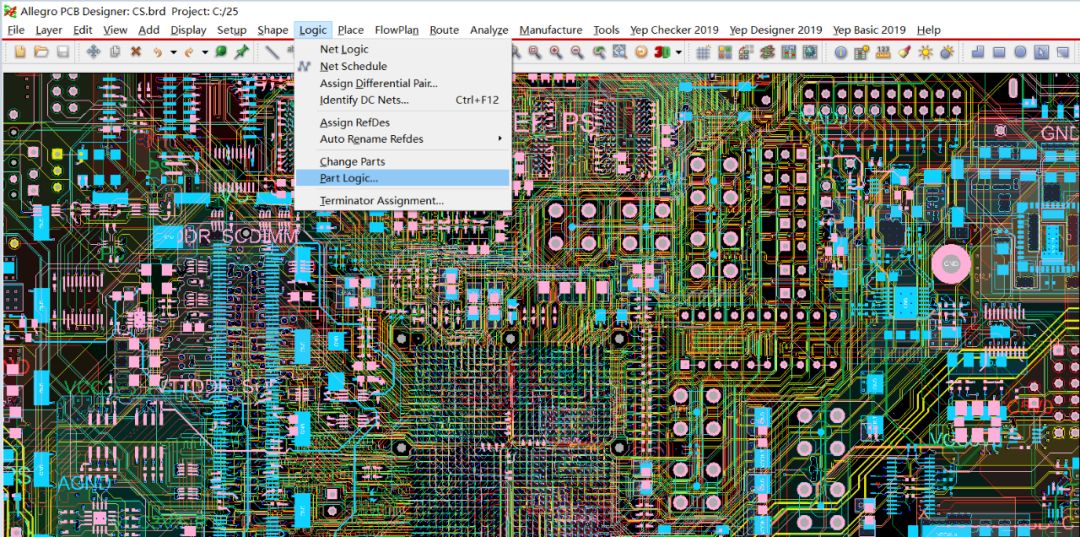

在项目实际的设计中我和小伙伴一样都遇到过很多麻烦的问题,有些时候原理图和PCB设计可能是由不同的工程师负责,由于种种原因可能需要在没有原理图的情况下直接对PCB进行操作。如更新元件封装和增加与删除元件等操作。接下来我们一起学习

扫码关注

扫码关注