- 全部

- 默认排序

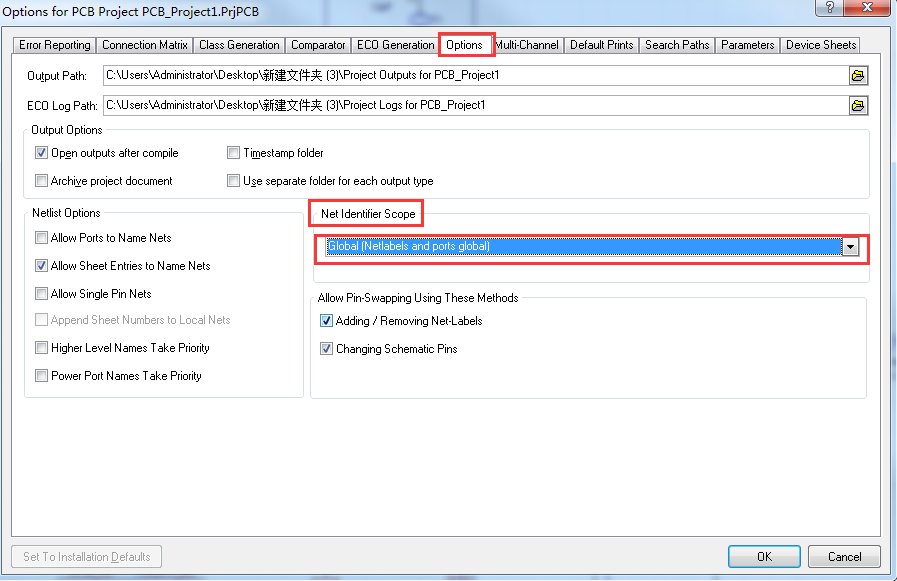

我们在日常画板子的时候,有时会出现一个比较尴尬的问题:同一个工程下不同原理图之间的相同网络标号导入到PCB文件之后,pin没有连接在一起;编译是还会出现报错,error:DuplICate Net Names。可以直接忽略,但存在报错实在让人难受。

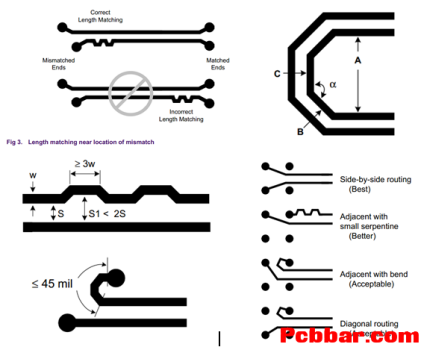

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

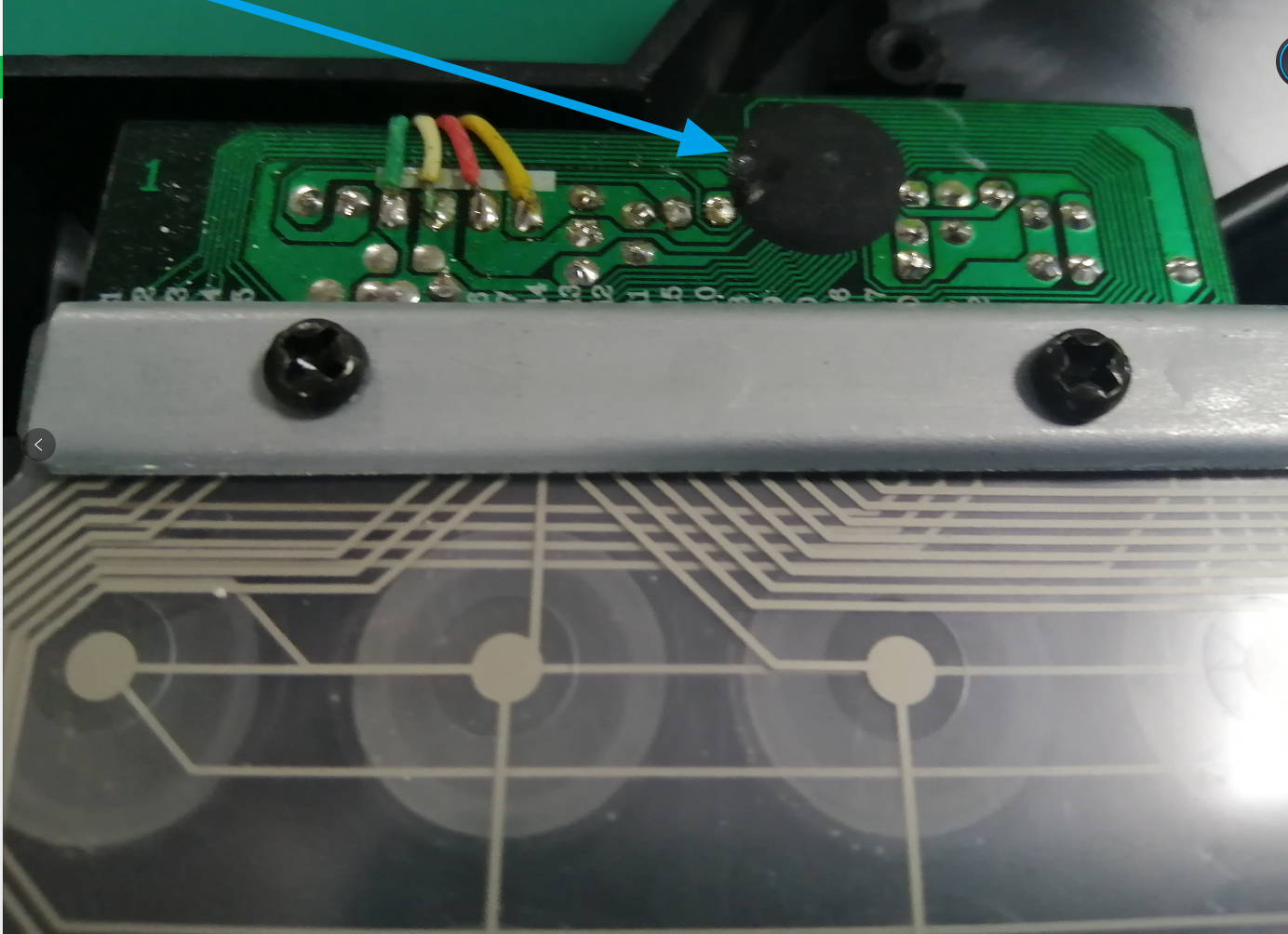

COB封装绑定IC

COB封装即chip On board,就是将裸芯片用导电或非导电胶粘附在互连基板上,然后进行引线键合实现其电气连接。如果裸芯片直接暴露在空气中,易受污染或人为损坏,影响或破坏芯片功能,于是就用胶把芯片和键合引线包封起来。人们也称这种封装形式为软包封。

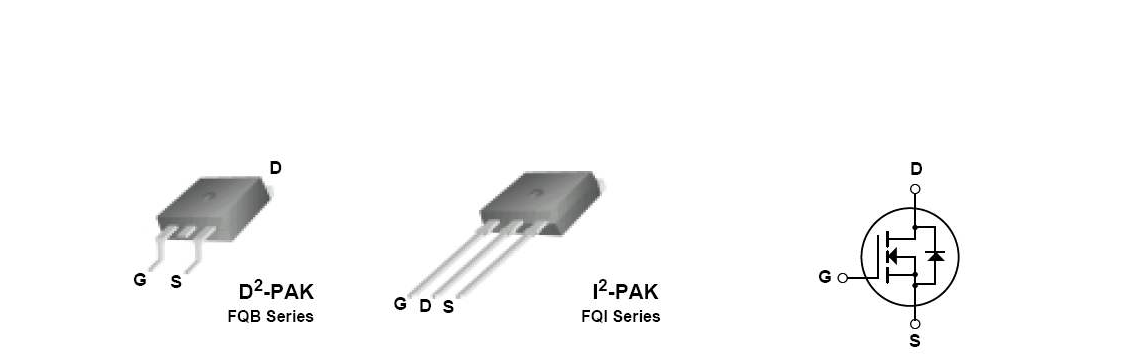

MOS管寄生电容

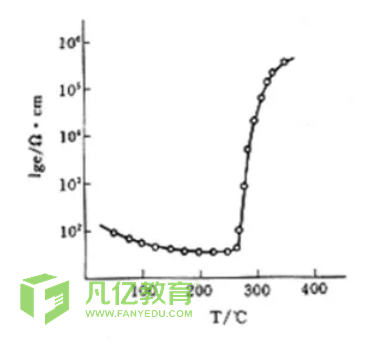

寄生电容是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,一个电阻的串联,低频情况下表现不明显,而高频情况下,等效值会增大。在计算中我们要考虑进去。ESL就是等效电感,ESR就是等效电阻。不管是电阻,电容,电感,还是二极管,三极管,MOS管,还有IC,在高频情况下要考虑到等效电容值,电感值

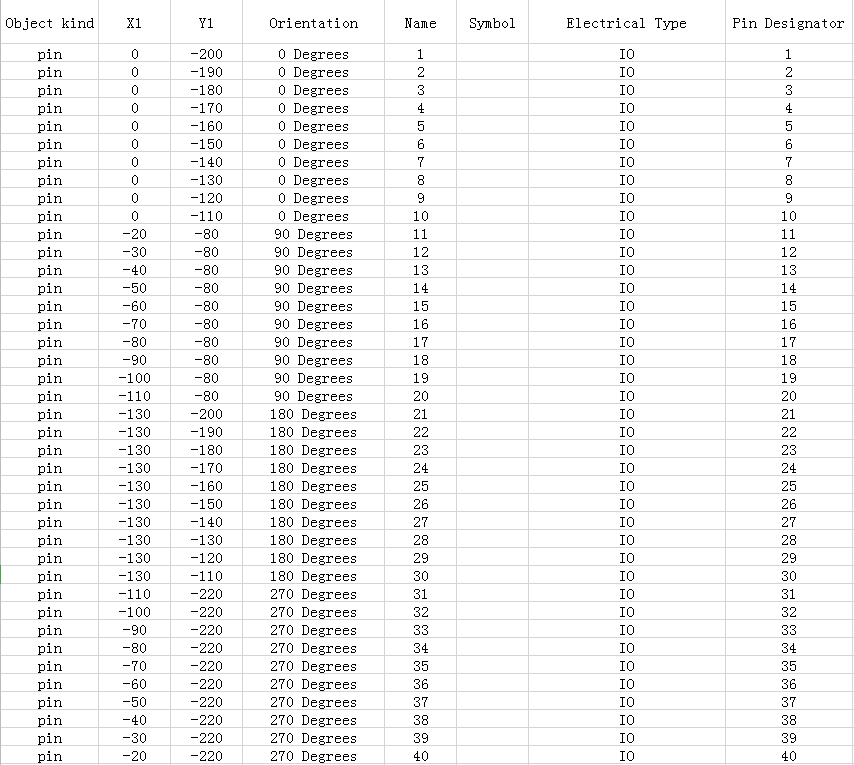

首先我们要在 Excel 中建立一个表格,下图的 Excel 为例子,自建,也可以先查找资料,有这方面的资料下载直接导入。下面8列是新加的包括 X、Y 坐标,方向,名字,电气属性,和管脚号等。 如果自建,上方的名字一定要对应,否则无法识别,会默认处理。

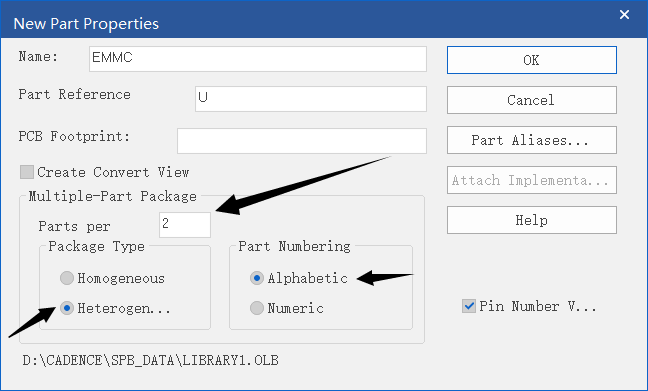

Heterogeneous类型器件由多个Part组成,但是每一个Part的组成部分都完全不一样,多数用于比较复杂的IC类器件,对IC属性进行分块设计,方便后期原理图的设计,在创建的时候,每一个Part都需要单独创建,相比于Homogeneous类型来说,麻烦一些

多家权威的测试和鉴定机构,如美国的保险商实验公司的UL认证、加拿大标准协会的CSA认证、日本国际与贸易工业部的MTTI认证和国际电气技术委员会的ICE认证。

扫码关注

扫码关注