- 全部

- 默认排序

创建 FPGA 设计和维护 Vivado® 设计套件项目时,版本控制系统对于团队合作可能是一项具有挑战性的任务。工程师必须能跟踪设计变更,完整地从 HDL 或 TCL 源代码再现项目并交付特定的项目状态。Vivado 工具非常适用于这类工作

在同步电路中,触发器和亚稳态一直以来是电子小白的学习难点,学完同步电路后很多小白都不理解亚稳态是什么?为什么两级触发器可以防止亚稳态传播,所以今天来回答这些问题,希望对小伙伴们有所帮助。一般来说,亚稳态是指触发器无法在某个规定的时间内达到可

FPGA已成为现阶段潜力最大的高薪首选工作之一,吸引了很多毕业大学生、转职就业的人选择其发展,但很多小白在学习FPGA时没做过太多功夫,导致不怎么了解FPGA,盲目学习,反而多走歪路,甚至被其他人淘汰,所以了解FPGA,确定好自身的发展路线

相比其他工程师,FPGA工程师的面试试题更加多变,涉及多学科,甚至部分面试还会谈到软硬件方面,所以FPGA工程师的面试难度相对比较高,今天我们寻找了四个常见的FPGA工程师面试必定会问到的题目。1、锁存器(latch)和触发器(flip-f

小伙伴们在学习FPGA时,最怕遇到同步时序电路设计,然而作为FPGA主要电路,同步时序电路试验频率居高不下,所以今天讲讲一些技巧,如如何实现同步时序电路的延时?如何实现RAM/ROM/CAM?1、FPGA设计中如何实现同步时序电路的延时?首

在电子行业的历史上,大多数先进技术是海外带来,所以很多名词术语基本上都是英文,但有很多人不太清楚那些名词术语,所以本文将盘点电子工程师必须了解的名词术语,希望对小伙伴们有所帮助。CMOS(Compelmentary Metal Oxide

由于该系列一经发布,反响良好,所以本文将更新电子工程师必须了解的名词术语系列下篇,若是想看上篇可点击右侧链接《电子工程师必须了解的名词术语(上)》。FPGA(Field Programmable Gate Array),即现场可编程门阵列,

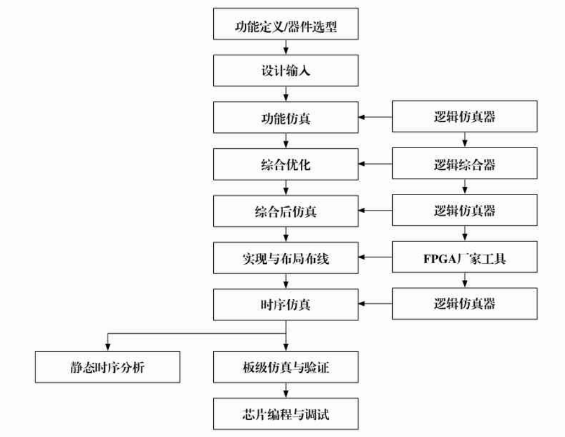

要设计可编程逻辑器件,如FPGA、CPLD等,并非一件易事,尤其是对于刚入FPGA的初级工程师来说,那么为了能够设计出一件优秀的可编程逻辑器件产品,我们该如何进行设计?一般来说,通常可将FPGA/CPLD设计流程归纳总结为以下7个步骤,基本

一、5M1270ZF256I5N IC CPLD 980MC 6.2NS 256FBGA说明:与其他cpld相比,MAX V系列低成本和低功耗cpld提供更大的密度和每占地面积的I/ o。MAX V器件的密度从40到2210个逻辑元件(32

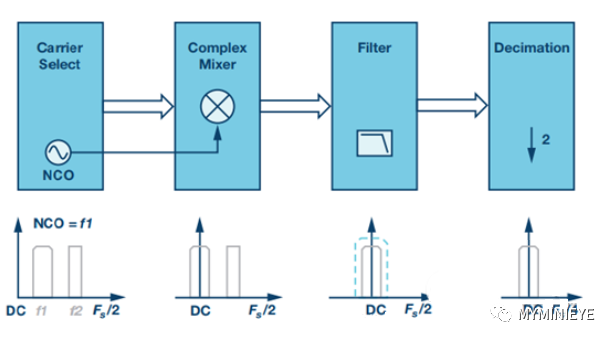

我们谈到的数字下的变“心”,也称数字下变频。数字下变频是一种广泛应用于数字无线电接收机的数字信号处理技术,其主要目的是经过数字混频将A/D转换输出的中频信号搬移至基带,然后通过滤波,抽取完成信道提取的任务,如下图所示:主要的电路模块由四部分组成:数控震荡、数字混频、数字滤波、采样抽取。1.matla

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注