- 全部

- 默认排序

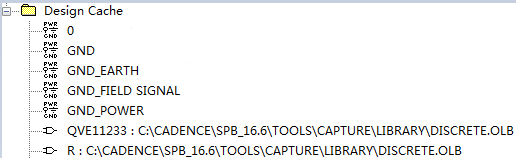

答:我们在使用Orcad软件进行原理图绘制的时候,会在整个工程文件的下方可以看到一个类似于文件夹的东西,下面是“Design Cache”,点开这个文件夹前面的+号,将文件夹进行展开,如图3-230所示,里面全部都是原理图封装库文件,而却是没有办法进行打开编辑的,具体这个Design Cache的功能是什么,我们这里呢给大家做一一的解释说明,具体如下, 图3-230 Design Cache展开示意图首先,这个Design Cache文件夹里面所包含的内容就是当

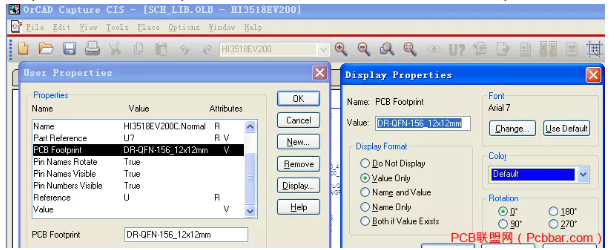

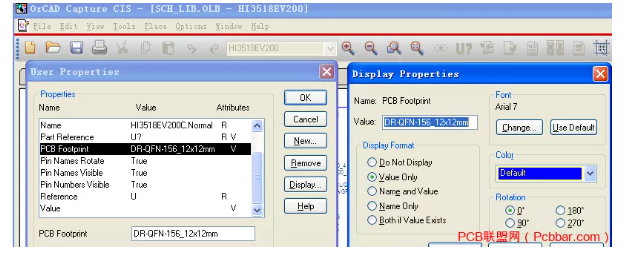

出现的原因:在原理图库中绘制了一个带有多个part的封装(HI3518EV200),但未设置PCB Footprint。在dsn空间的一个原理图内,通过Edit Part修改改器件的PCB Footprint时候,会因为dsn空间内的元器件封装与sch_lib.olb元件库的封装不同,导致会把修改后的封装保存到dsn空间内的Design Cache,并将名字修改为HI3518EV200_x。

出现的原因:在原理图库中绘制了一个带有多个part的封装(HI3518EV200),但未设置PCB Footprint。在dsn空间的一个原理图内,通过Edit Part修改改器件的PCB Footprint时候,会因为dsn空间内的元器件封装与sch_lib.olb元件库的封装不同,导致会把修改后的封装保存到dsn空间内的Design Cache,并将名字修改为HI3518EV200_x。

扫码关注

扫码关注