- 全部

- 默认排序

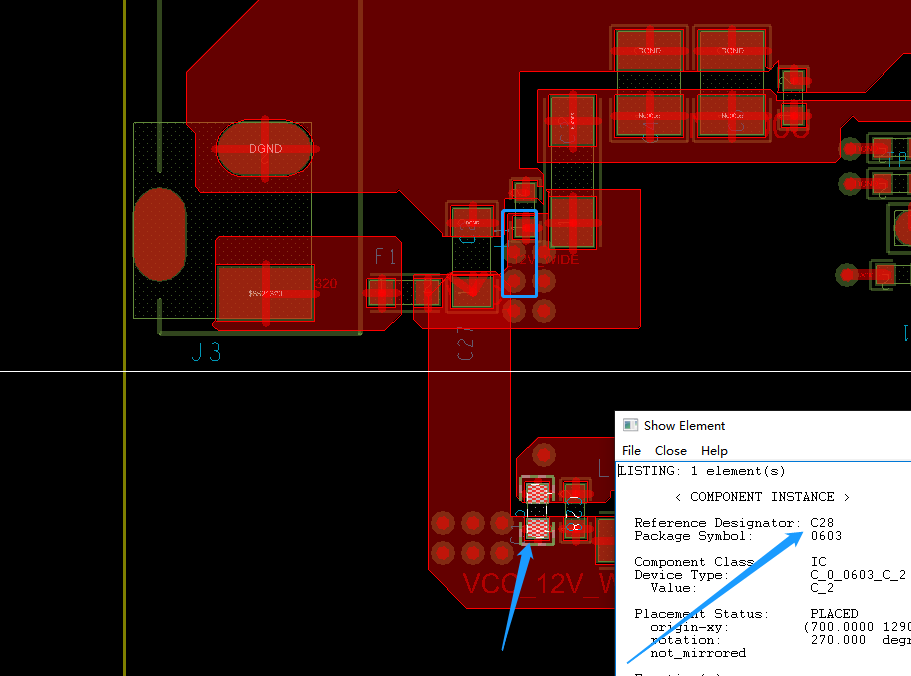

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。比如今天要讲解的DRC报错中的“Isolated copper:Split pllane....”的报错,为了方便大家了解这项报错,我们找到了素材图片如下:

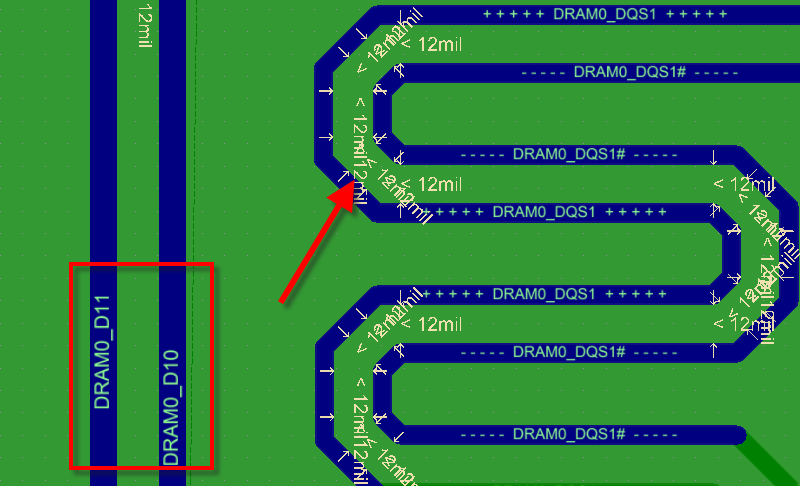

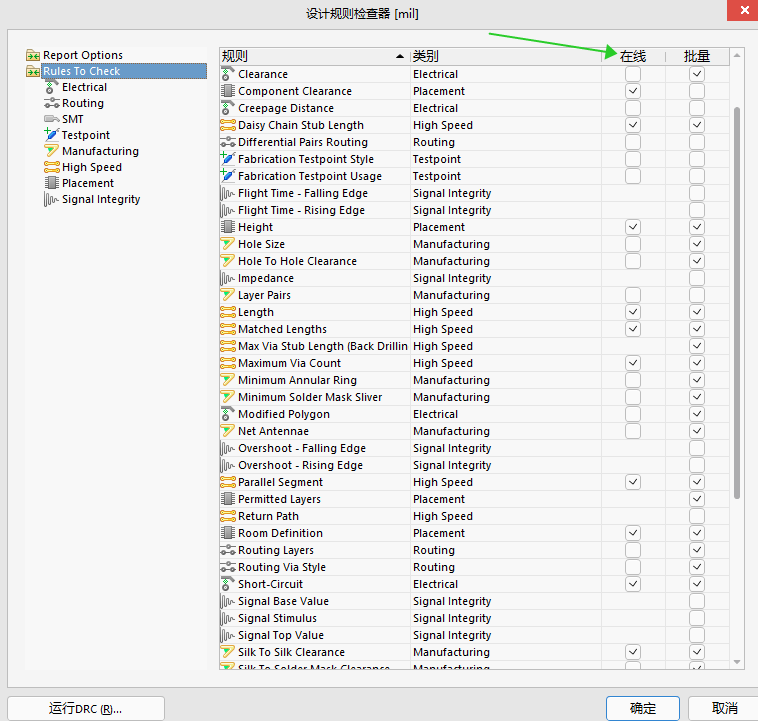

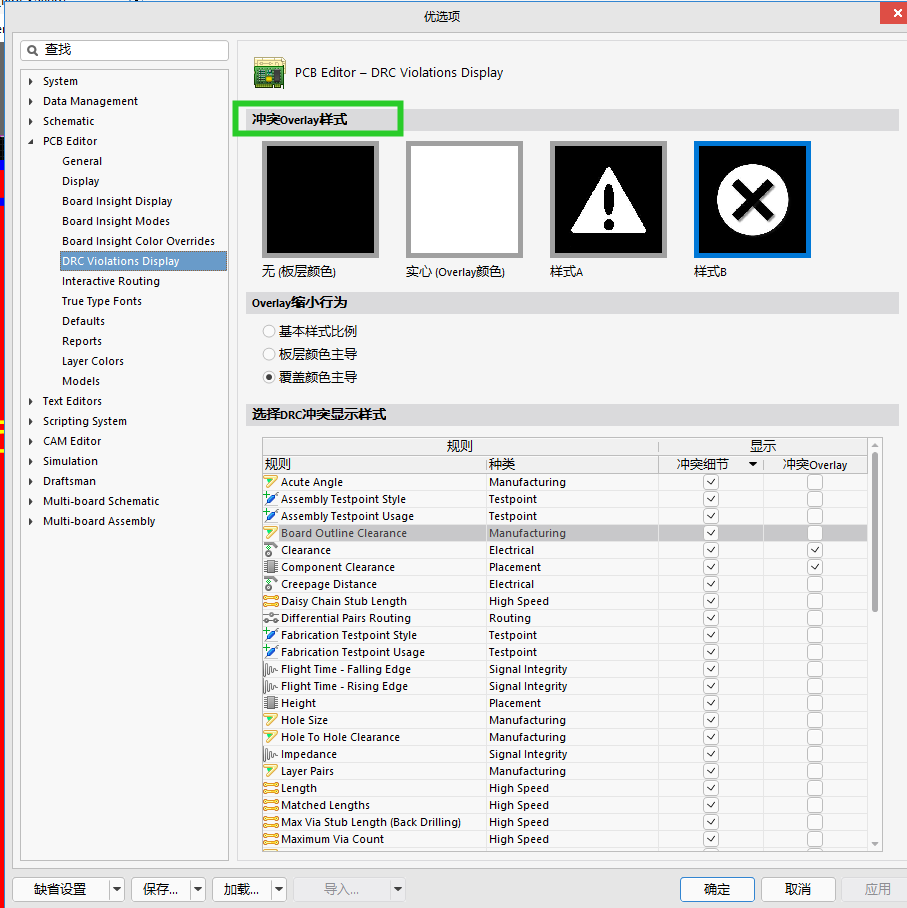

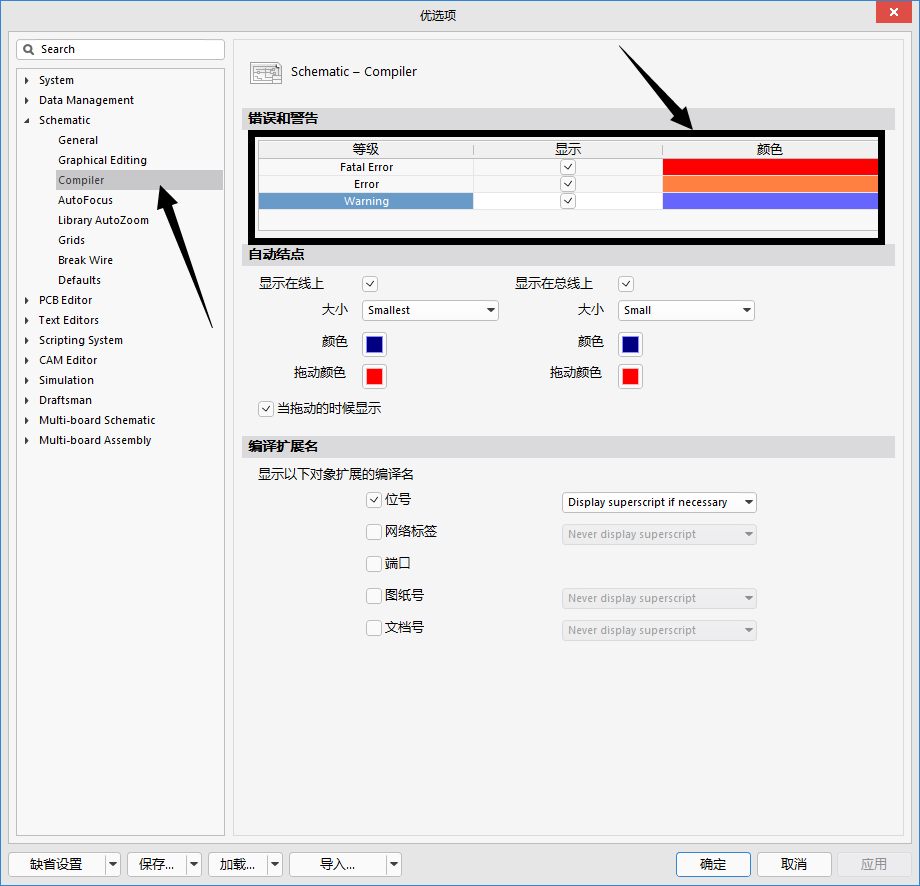

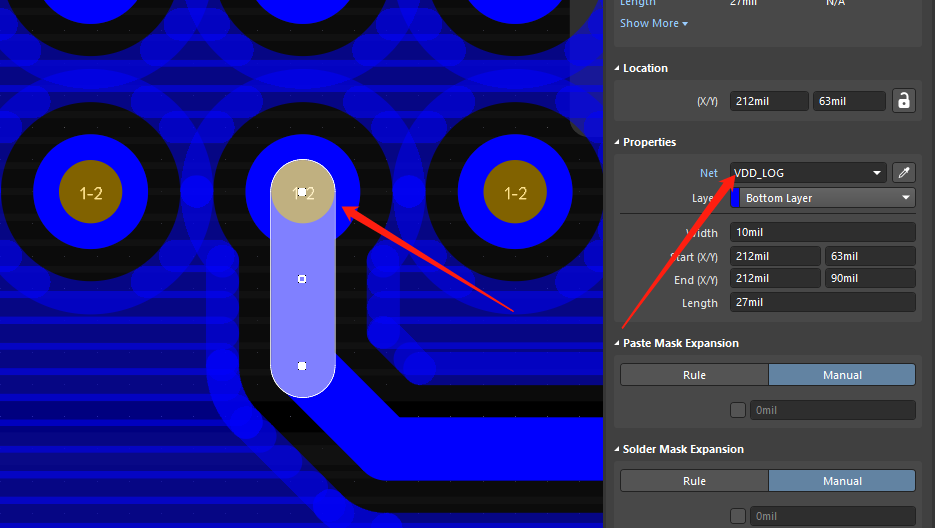

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

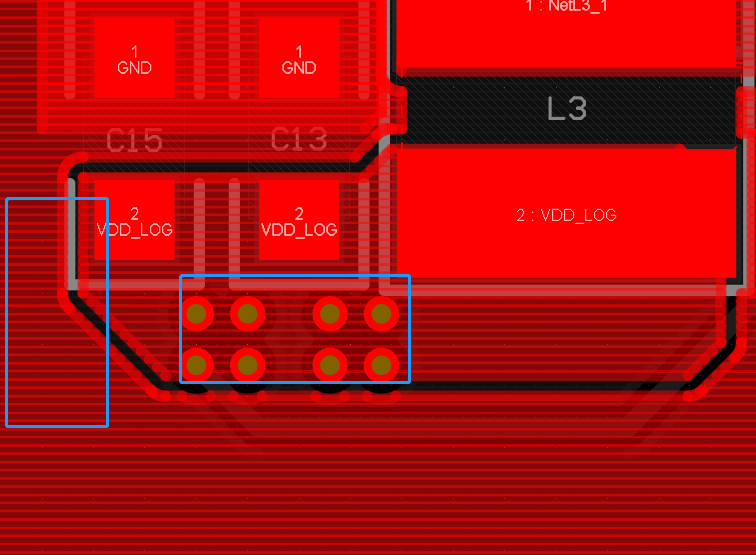

电流尽量从最后一个电容后面输出,自己调整一下铜皮宽度存在DRC报错3.此处铜皮宽度尽量加宽一些4.存在stub线头以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://i

此电容应该靠近座子放置2.单点接地此处不用打孔,直接在散热焊盘上打孔尽量回流3.存在DRC报错,后期自己调整一下走线路劲4.输出主干道需要铺铜,满足载流5.电感所在层的内部需要挖空处理6.器件干涉7.反馈从电容后面走一根10mil的线即可8

输出打孔要打在滤波电容后面2.此处不满足载流,载流是一铜皮最窄出计算的,后期自己加宽一下铜皮3.铺铜是尽量把焊盘包裹起来,这样容易造成开路4.存在多处开路和DRC报错5.电感下面不要走线和放置器件6.注意中间散热焊盘上的过孔需要开窗处理7.

存在无网络过孔,短路了2.输出过孔要打在最后一下滤波电容的后面3.过孔不要上焊盘4.电感下面尽量不要放置器件和走线5.存在多处开路和DRC报错,后期自己处理一下6.注意走线需要连接到焊盘中心,此处需要优化一下7.相同网络的走线和铜皮未进行连

扫码关注

扫码关注