- 全部

- 默认排序

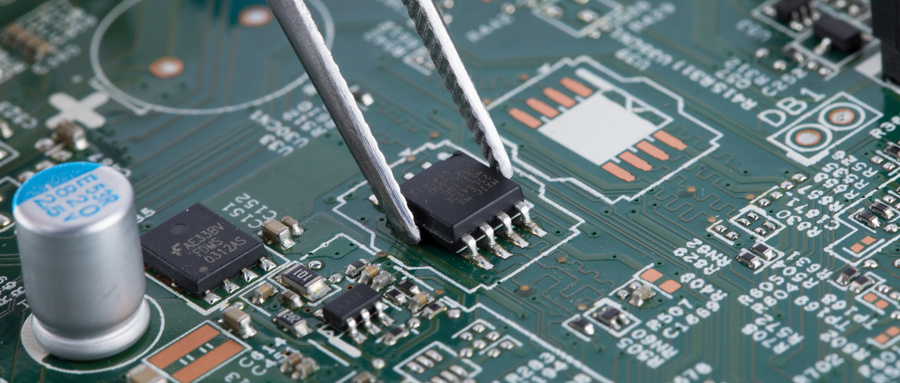

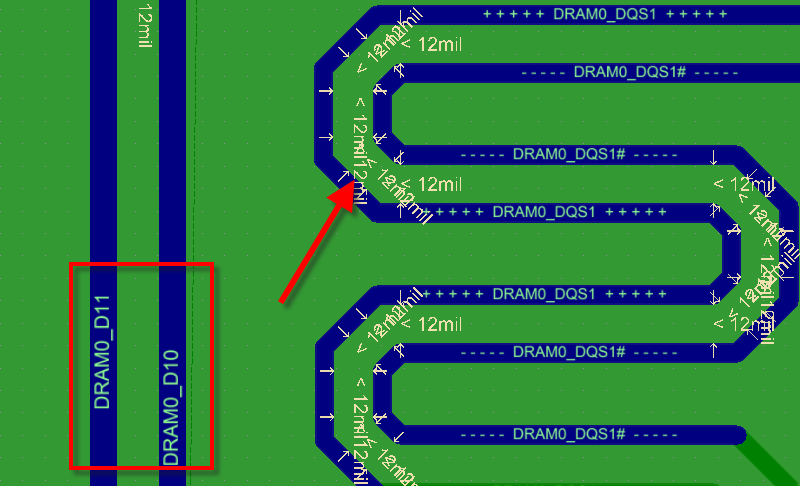

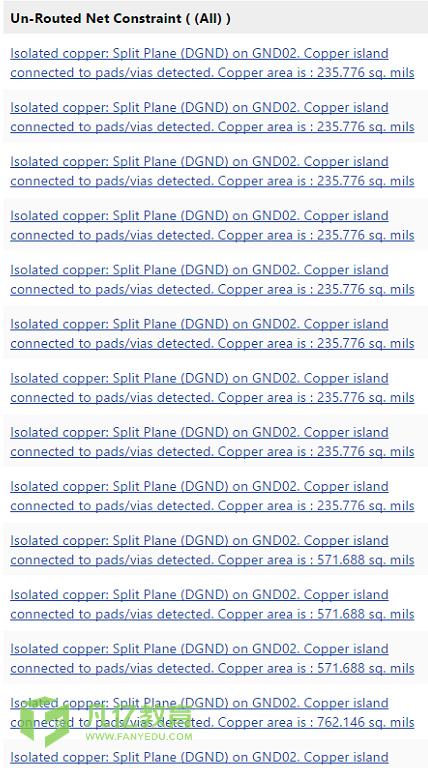

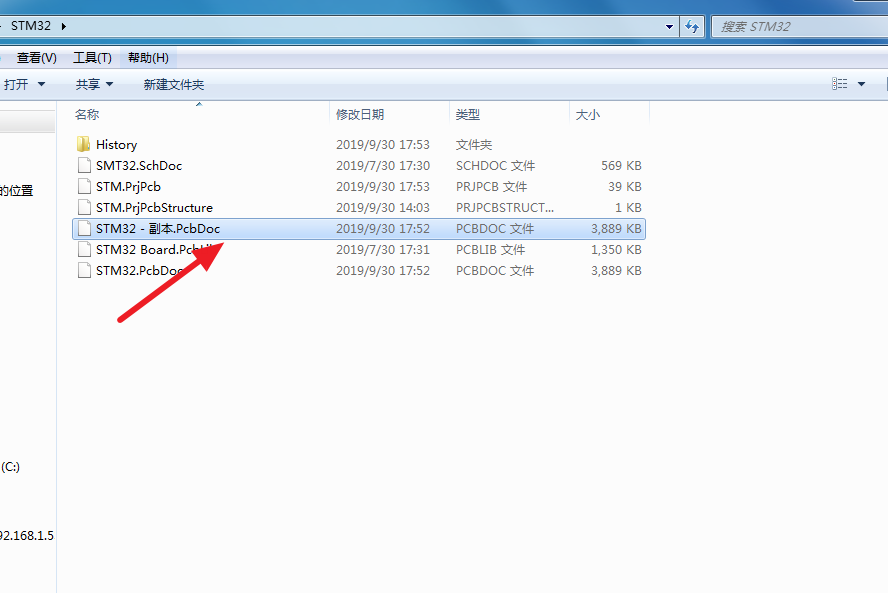

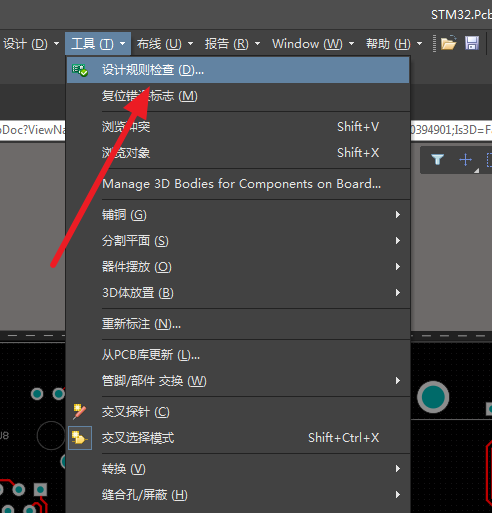

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

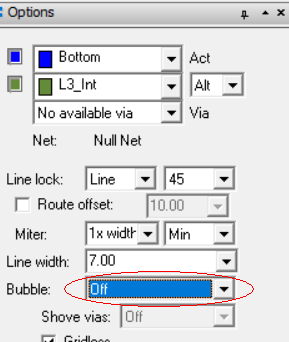

allegro在布线过程中,根据个人习惯有多种避让方式可以选择,不管采用那种方式,都需要经过优化才能使pcb布线更符合设计要求,推荐交叉使用以下方式进行布线。(1)使用off方式进行布线,可能导致很多DRC的产生,把网络连接好后,需要把DRC都消除掉。优化时需要把格点设小,使用微调推挤或重新布线方式,优点是布线可根据个人的意愿进行,布线速度快;缺点是优化时需要花费

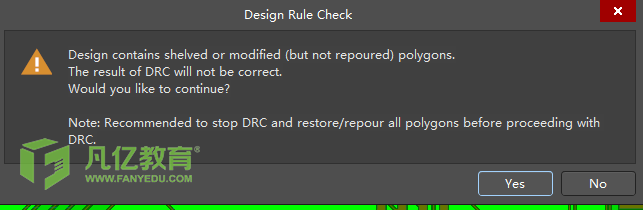

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。

在我们设计完成原理图之后,设计PCB之前可以利用软件自带的ERC功能对于我们原理图去进行常规的一些电气性能的检查,避免出现一些常规的错误。

我们在进行PCB设计时,在连线走线的时候,会经常出现这么两种情况:1.走线连接到焊盘上时,我们以为自己已经连接到了焊盘中心点上,早已连接上了,其实没有。那么,这个对于我们后期会造成虚焊,而且这一项有时DRC也检查不出来。所有为了减少我们不必要的损失,就来讲一下这项常用的方法。2.走线跟走线连接的时候,以为是连接上了,其实也是没有连接上来,会有开路的现象。

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。

扫码关注

扫码关注