- 全部

- 默认排序

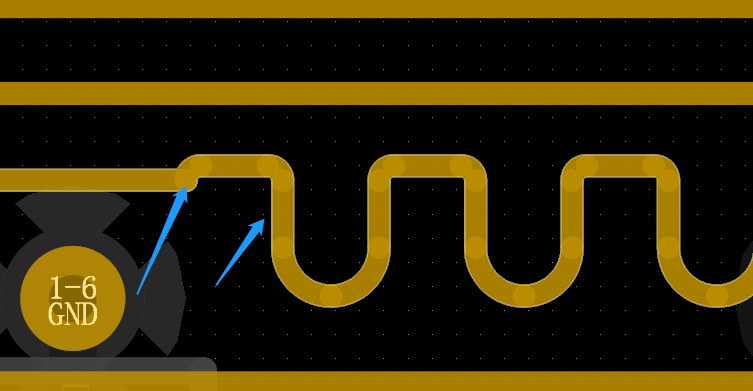

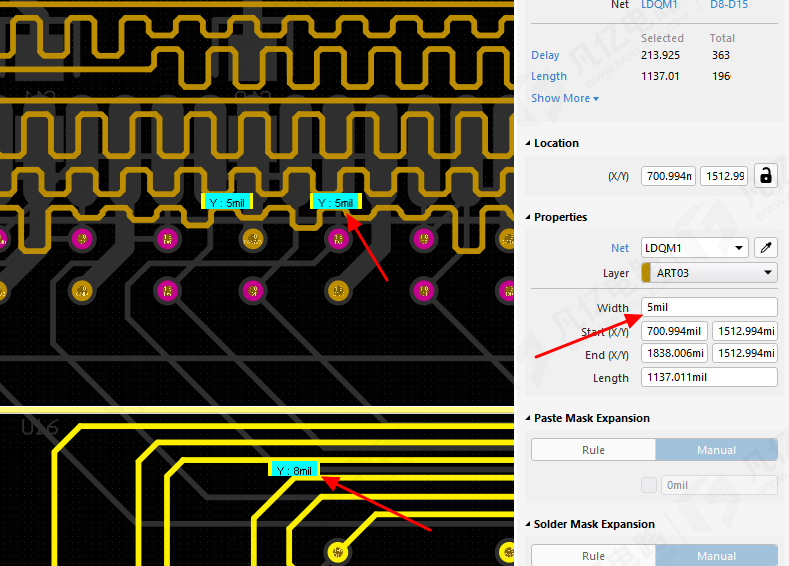

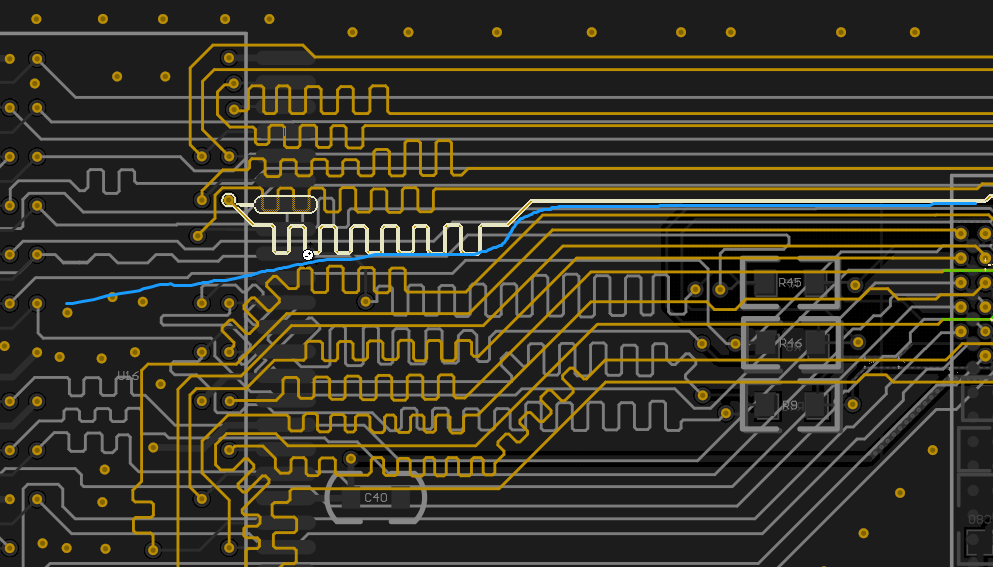

走线需要优化一下尽量钝角绕蛇形,等长可以在优化一下2过孔需要盖油处理,且里面不要有多余的线头3.注意pcb上尽量使用同一种类型的过孔,过孔种类不要超过两个4.器件摆放注意不要干涉5.走线不需要开窗,加后期自己处理一下6.还有电源为处理,存在

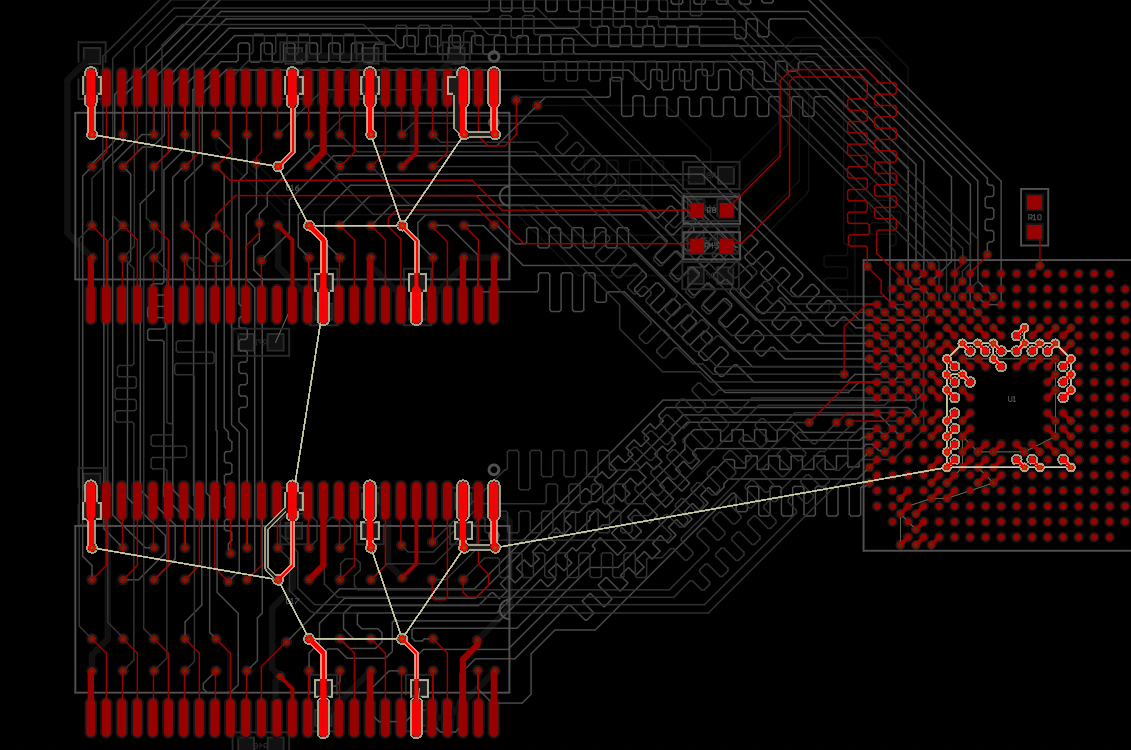

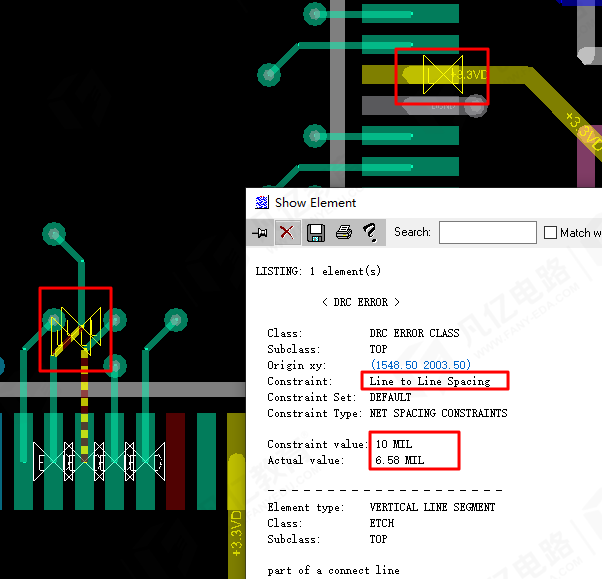

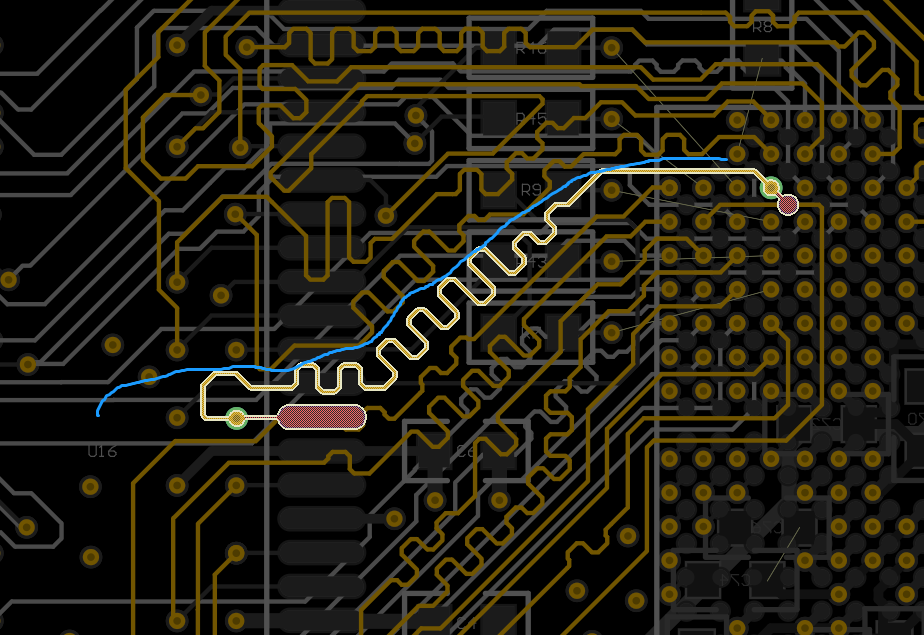

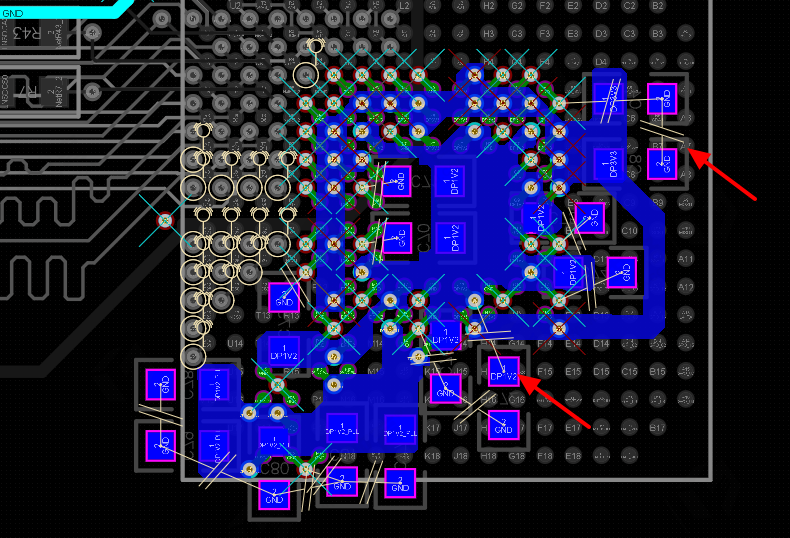

电源网络DP3V3全都是飞线显示,内层存在电源层赋予对应网络即可:电源平面层没有赋予网络,导致存在飞线网络没有连接:焊盘扇孔注意对齐,都没对齐,需要修改:类似这种过孔内存在线头的自己删除:注意走线优化:地址线内还存在误差报错:不需要拉线的地

可以解决的报错处理一下顶层焊盘没有连通,器件没有连接所有等长组都没有达到等长目标以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/it

走线保持3w间距等长绕线尽量咬合电容尽量靠近焊盘,电源走线加粗时钟线等长错误以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item

SMART DDR3(L) SDRAM组件与行业广泛兼容,并提供x8和x16配置。这些1.35v(DDR3L)和1.5V(DDR 3)器件采用标准78和96引脚网格阵列封装,时钟速度为1866 Mbps,密度为1Gb、2Gb和4Gb。KTD

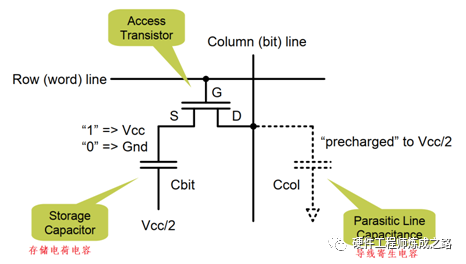

最近想对DDR了解多一点,看标准的时候发现有些概念还是不清楚,比如预充电Precharge是什么?刷新Refresh,又是为什么?要知道这些问题的答案,就需要知道DDR内部存储单元结构,通过查阅资料,总结如下,分享给大家。 DDR SDRAM Bit CellsDDR SDRAM是类似一个网格阵列,

地址线与数据线之间尽量用一根地线进行分开2.注意走线尽量不要有直角,后期自己优化一下3.注意数据线尽量整组走一起4.注意此处等长不满足原理图要求5.一个电源直接连接在一起即可,不用进行分割注意器件摆放尽量不要干涉一脚标识,建议2mm过孔需要

注意地址线与数据线之间尽量加一根地线进行分开2.注意数据线尽量整组走一起,中间不要加入地址选项,后期自己优化一下走线路径数据线等长存在误差报错片选信号也需要加入地址线组里面进行等长注意此处需要满足原理图要求注意需要把电源和地网络在平面层处理

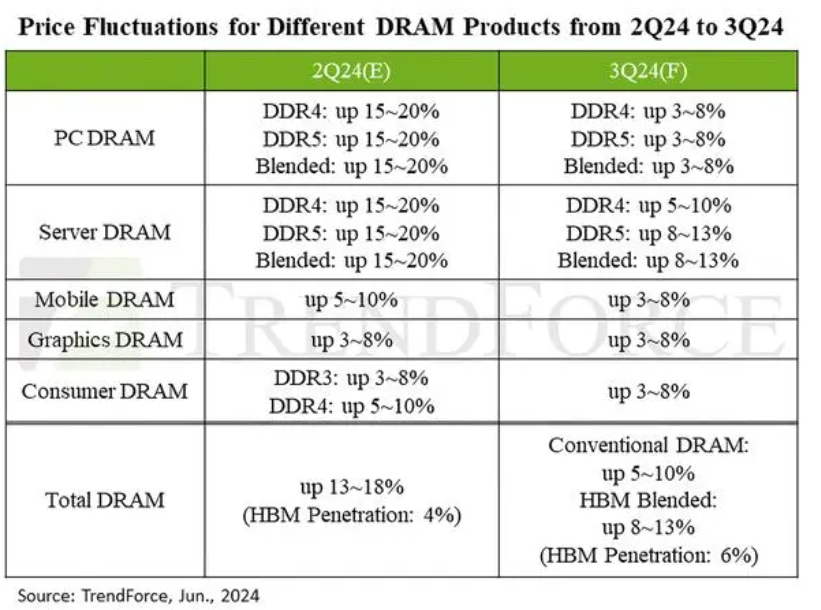

在内存芯片中,DRAM毫无疑问是使用频率极高的,尤其是当下电子技术高速发展,很多厂商必须密切关注这些芯片的发展趋势,以此抢占更多的市场份额。近日,知名市场调研机构TrendForce对2024年第三季度的DRAM和VRAM芯片进行了预测,他

多处器件未连接,造成多处开路报错等长绕线应尽量上下咬合绕线太乱,尽量到保持间距一致绕线整齐地址线等长不达要求,有电容的走线应建立xSignals整条走线进行等长时钟走线等长错误,应按下图示范等长以上评审报告来源于凡亿教育90天高速PCB特训

扫码关注

扫码关注