- 全部

- 默认排序

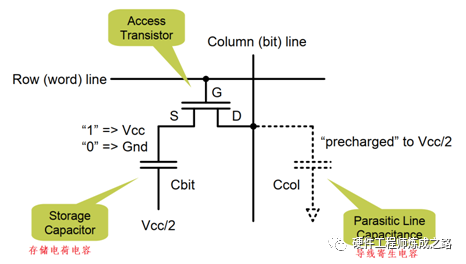

最近想对DDR了解多一点,看标准的时候发现有些概念还是不清楚,比如预充电Precharge是什么?刷新Refresh,又是为什么?要知道这些问题的答案,就需要知道DDR内部存储单元结构,通过查阅资料,总结如下,分享给大家。 DDR SDRAM Bit CellsDDR SDRAM是类似一个网格阵列,

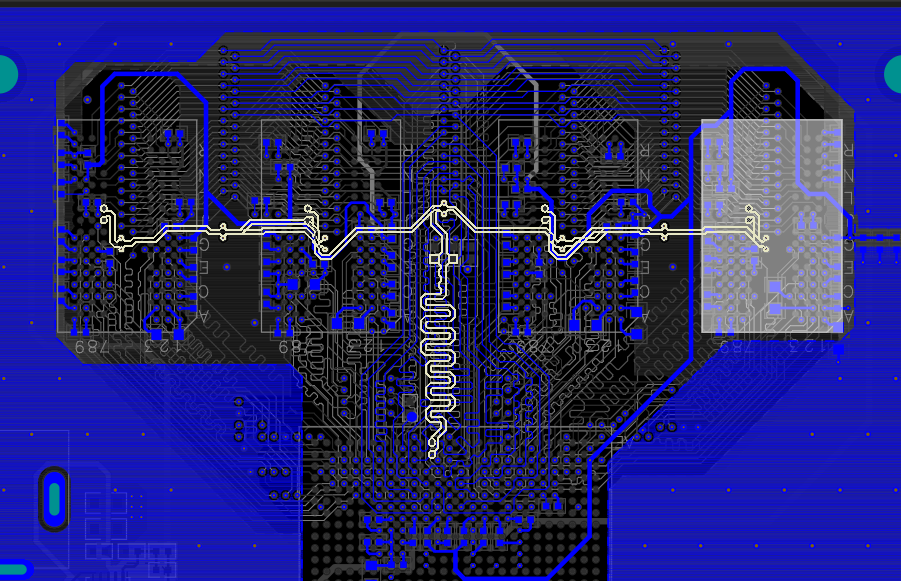

DDR3尽量采用菊花链形式,效果更加2.注意数据线之间等长需要满足3W间距规则3.注意VREF电源走线需要加粗到15mil以上,尽量不要有锐角以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码

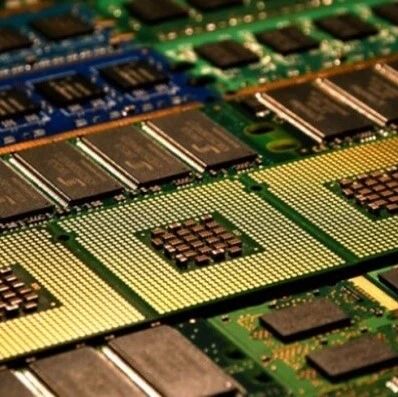

今年9月合肥长鑫宣布开始量产 8Gb 颗粒的国产 DDR4 内存,随着总投资 1500 亿元的合肥长鑫内存芯片自主制造项目投产,我们可自主生产国产第一代 10nm 级 8Gb DDR4 内存。不过国产内存的产能占全球的比例依然非常小,长鑫今年内的产能只有 2 万片晶圆 / 月,2020 年的时候国内

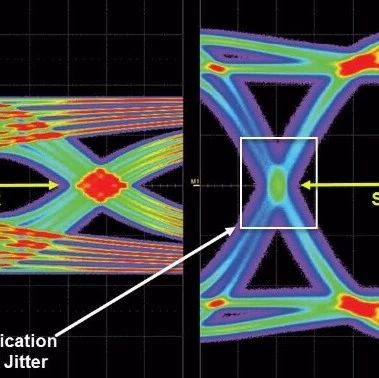

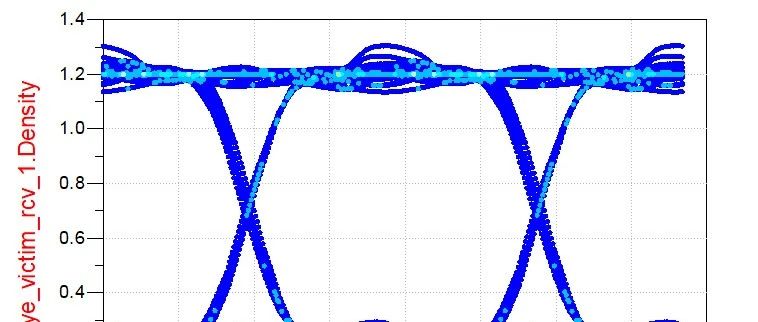

随着数据传输速率越来越高,现在计算机系统中的数据传输接口基本上都串行化了,像USB、PCIe、SATA、DP等等外部总线将并行总线挤压到只剩下内存总线这个最后的堡垒。当然,就算是并行传输总线最后的倔强DDR也在不断吸收SERDES上的技术来提升自己,尤其是均衡器(Equalization,EQ)技术

信号包地反而更差?

信号包地目的有两种,一是包地线负责回流,二是负责隔离,也就是防止串扰。但是有时候包地线处理不好,反而会使信号变得更差。对于如下结构,DDR4的DQ信号之间为了防止彼此串扰,用了包地线;下面我们来看一下,不考虑邻近的信号线和包地线,单根信号线上的信号: 信号为点对点结构,接收端内部ODT端接,信号质量

DDR布线技术的重要性在如今的印刷电路板设计中,双数据速率(DDR)存储器非常普遍。许多设计都会用到DDR存储器配置的不同版本,这需要在布局中使用特定的布线模式。DDR的名称来源于其能够在每个时钟周期内发送和接收两次信号,是原先的单数据速率(SDR)存储器速率的两倍。由于速率增加了一倍,必须在布设D

电子工程师刚开始接触DDR4存储器时,线路板密密麻麻的,动辄DDR2/3/4的,专业术语层出不穷的,很容易看晕。而且随着DDR产品的迭代更新,存储器项目的设计复杂度翻倍增长。同时,DDR产品的设计难度很高,因为它涉及到高速数字电路和复杂的时

信号包地反而更差?

信号包地目的有两种,一是包地线负责回流,二是负责隔离,也就是防止串扰。 但是有时候包地线处理不好,反而会使信号变得更差。 对于如下结构,DDR4的DQ信号之间为了防止彼此串扰,用了包地线; 1、下面我们来看一下,不考虑邻近的信号线和包地线,单根信号线上的信号: 信号为点对点结构,接收

随着电子技术高速发展,内存也开始向DDR5迭代,不少工程师已经更换成了DDR5内存,相比其他DDR产品。DDR5主频更高、能频升级,还增添了规范的标签。那么如何通过标签来分辨DDR5产品、一般来说,市场上的DDR5产品标签共有两种,一是旧版

DDR是当前最常用的存储器设计技术之一,其高速、低功耗的特性满足了众多消费者的需求。但随着传输速度的加快,DDR的设计验证难度呈指数上升。对仿真工程师来说,DDR的高速率很容易引起一系列信号完整性问题,引发包括时序冲突、协议背离、时钟抖动及

扫码关注

扫码关注