- 全部

- 默认排序

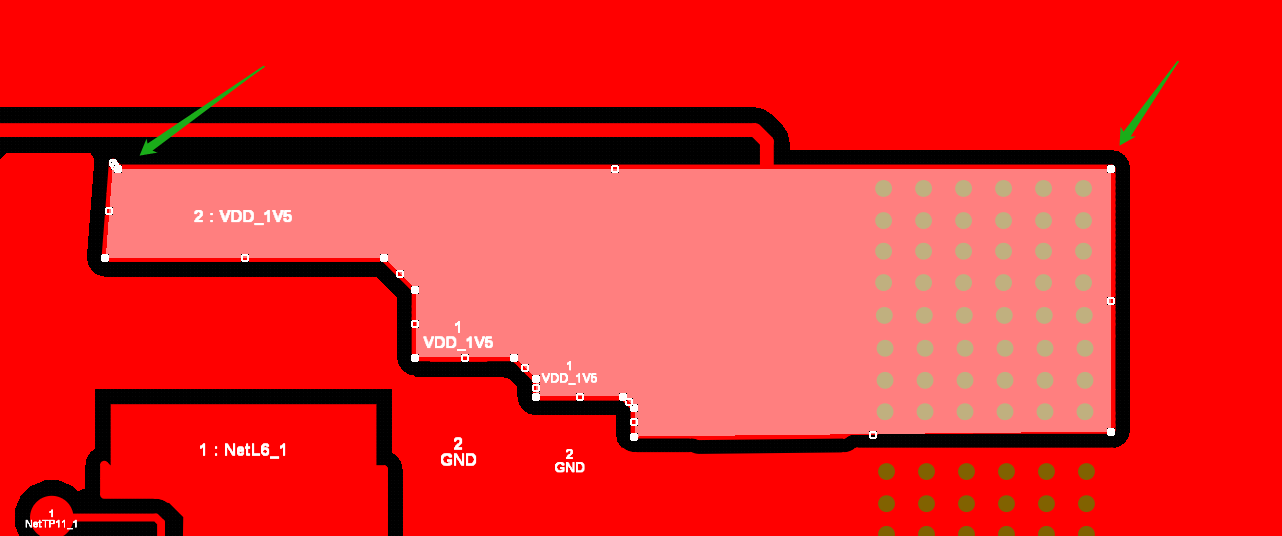

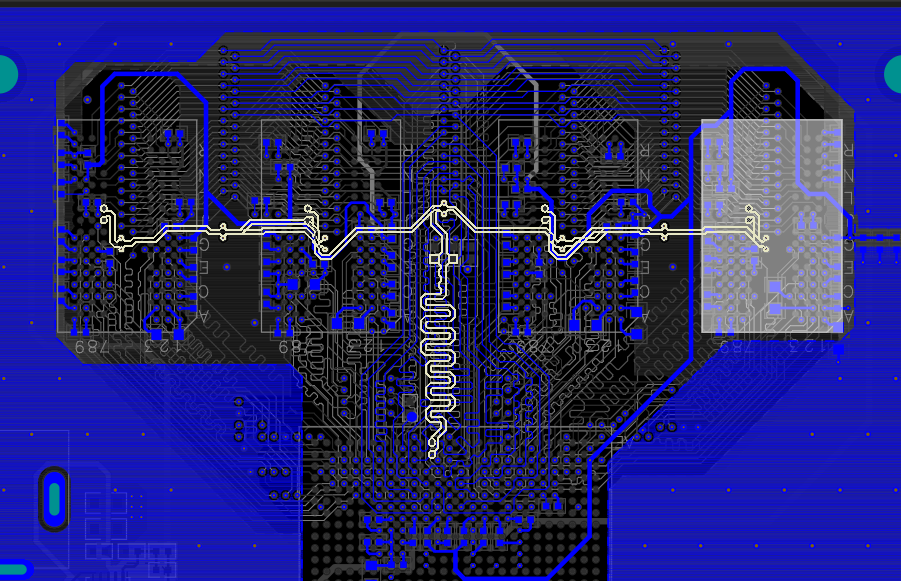

DDR3 2片:电感内部挖空处理。注意电源铺铜不要出现这种瓶颈处:等长线注意要保证3W间距,去调整出来:数据线需要满足等长误差,还存在报错:数据线也要满足3W间距自己注意走线跟过孔的间距规则:分割带尽量大于20MIL:以上评审报告来源于凡亿

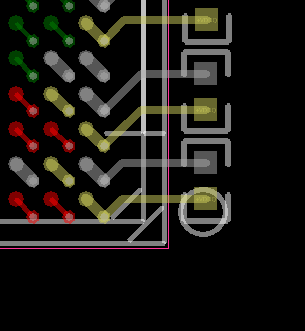

DD3 四片:注意不要出现这种锐角走线:负片层并未赋予网络:注意设计完了之后检查下走线的连接性:并未保证3W间距原则:差分对内等长注意规范:差分对内等长误差为5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特

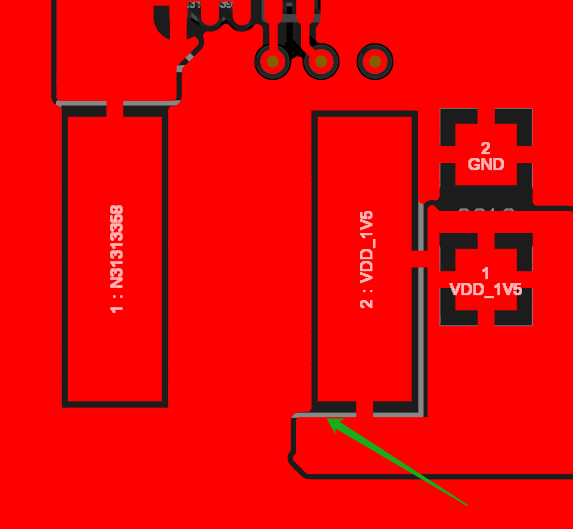

电源反馈信号要从最后一个器件连线,过孔要打到最后一个器件后方焊盘出线避免从长边出线布线保持3w间距规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.ta

注意一脚标识不要跟器件重叠了,注意调整下:注意电源信号的线宽是否满足载流:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.

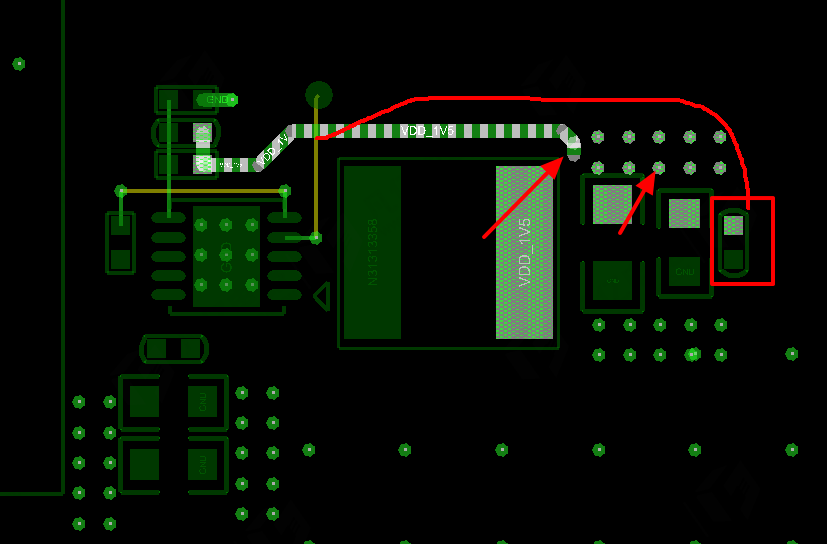

注意铜皮形状尽量钝角,不要直角以及尖角,类似情况自检修改下:走线也不能出现直角:电感内部的铜皮挖空处理:过孔按照对应的电流大小计算数量加2 或者4个裕量就行了:差分进过孔也是需要耦合连接的,优化下:注意下等长线之间需要满足3W间距:避免高速

SMART DDR3(L) SDRAM组件与行业广泛兼容,并提供x8和x16配置。这些1.35v(DDR3L)和1.5V(DDR 3)器件采用标准78和96引脚网格阵列封装,时钟速度为1866 Mbps,密度为1Gb、2Gb和4Gb。KTD

DDR3尽量采用菊花链形式,效果更加2.注意数据线之间等长需要满足3W间距规则3.注意VREF电源走线需要加粗到15mil以上,尽量不要有锐角以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码

购买的4片DDR3 T点拓扑高速pcb设计速成实战视频中没有支路的等长视频,视频中只是说书有讲,但是书上讲的不是很详细,支路的等长我还是不太会吖,能否录个支路的等长视频给我,能否录个from to的用法视频

购买的4片DDR3 T点拓扑高速pcb设计速成实战视频中没有支路的等长视频,视频中只是说书有讲,但是书上讲的不是很详细,支路的等长我还是不太会吖,能否录个支路的等长视频给我,能否录个from to的用法视频

扫码关注

扫码关注