- 全部

- 默认排序

阻焊层:solder mask,是指板子上要上绿油的部分;因为它是负片输出,所以实际上有solder mask的部分实际效果并不上绿油,而是镀锡,呈银白色!助焊层:paste mask,是机器贴片时要用的,是对应所有贴片元件的焊盘的,大小与toplayer/BOTTOMlayer层一样,是用来开钢网

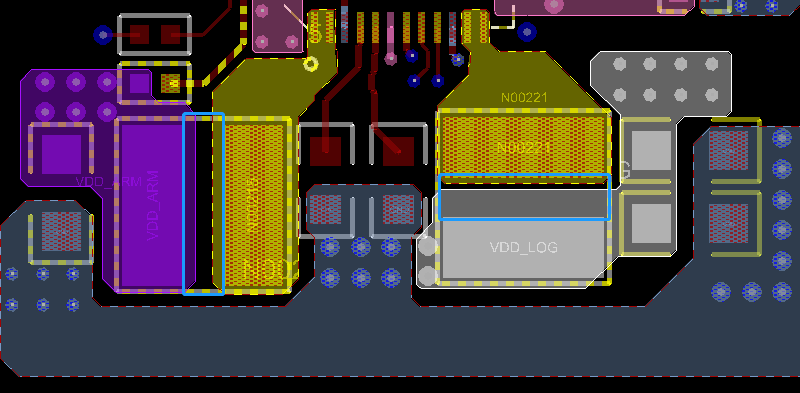

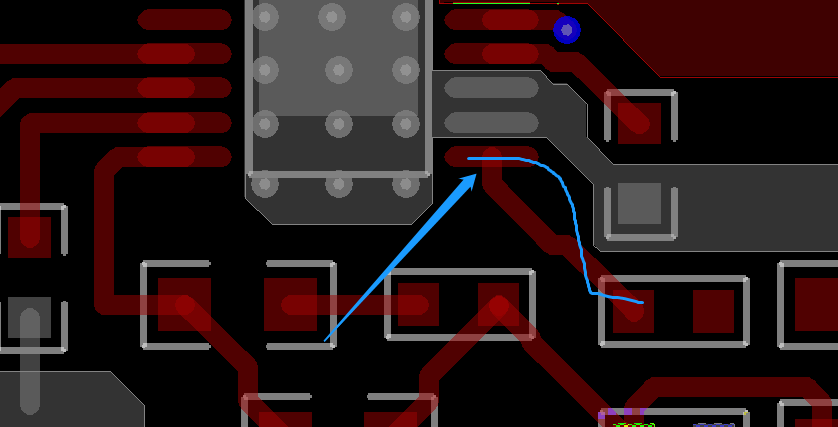

电感所在层的内部需要挖空处理2.反馈器件靠近管脚放置,从输出滤波电容后面取样,走一根10mil的线即可,不用进行铺铜3.此处电源不满足载流,滤波电容尽量靠近管脚摆放,可以放BOTTOM层4.电源需要再底层铺铜进行连接,走线太细,不满足载流5

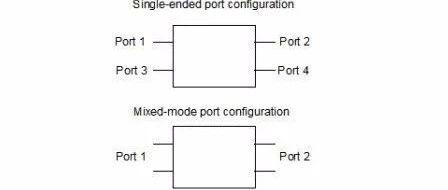

单端S参数转差分S参数

在射频领域,一般都是单端器件,走单端线;在数字硬件,走速率高的线,一般都是差分线。而且那些高速串口信号传输速率越来越高,10GSPS已经变得很寻常。而当你布线的时候,可能不得不打个过孔,从TOP面穿到BOTTOM面;可能还需要差分线尺寸,以能进入FPGA区域;又或者你需要把线走成弯弯曲曲的,以满足等

存在多处开路地网络后期自己在BOTTOM层铺铜进行连接2.采用单点接地,此处可以不用打孔,只需要在芯片中心打孔进行回流即可3.输入打孔要打在滤波电容的前面4.输出打孔要打在滤波电容后面5.以上评审报告来源于凡亿教育90天高速PCB特训班作业

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.走线尽量不要走直角,建议45度3.铺铜注意层的问题,器件在top层,铜皮在BOTTOM层4.模块复用后铜皮变静态铜皮,需要自己调整成动态铜皮,后期自己处理一下5.采用单点接

PCB 进行design rule check 时报错,提示Un-Routed Net Constraint: Net V_VS Between Track (33.223mm,-13.425mm)(34.781mm,-13.425mm) on BOTTOM Layer And Pad R85-2(

PCB 进行design rule check 时报错,提示Un-Routed Net Constraint: Net V_VS Between Track (33.223mm,-13.425mm)(34.781mm,-13.425mm) on BOTTOM Layer And Pad R85-2(

为什么我在用AD17.1覆铜时,点BOTTOM layer时还是显示top layer 有照片

调整器件正反层(top层和BOTTOM层)的快捷键是什么呀?两个月没布PCB忘记了[CQ:face,id=211]感谢那个是翻转的,我是想把器件的正反面换一下

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注