- 全部

- 默认排序

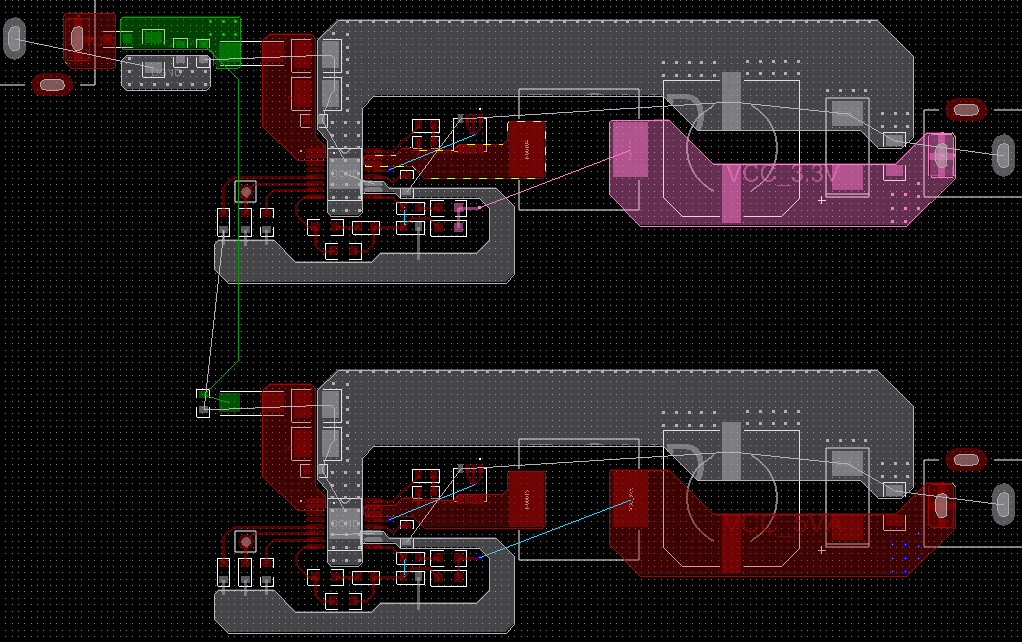

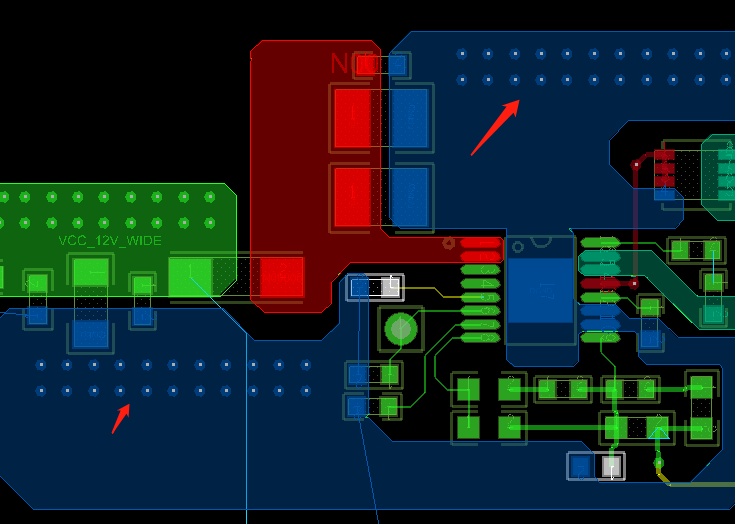

器件布局的时候尽量注意下对齐:上述一致原因,尽量整体中心对齐:差分信号打孔换层两侧都要打上地过孔:还存在飞线:建议每组差分信号包地处理:注意过孔的间距保持,避免把内层平面割裂:注意差分对内等长的GAP长度规范:差分对内等长误差为5MIL:以

最近电子工程师的就业市场显然有些低迷,越来越多大厂宣布开始裁员,甚至缩减了招聘岗位降低薪资,那个被无数问到的问题再次被提及“电子工程师的未来是不是会大量失业?”首先表明下我的观点:会,但原因并不是来自最近火爆的“AIGC”,而是这个行业发展

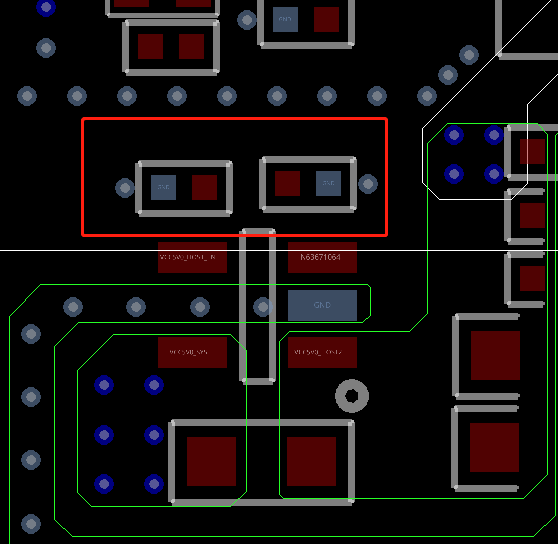

1.多处飞线没有连接2.要求单点接地,地网络只在芯片下方打孔连接,其他地方地网络不要打孔3.相邻电路的电感应朝不同方向摆放4.底层应整版铺地铜处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

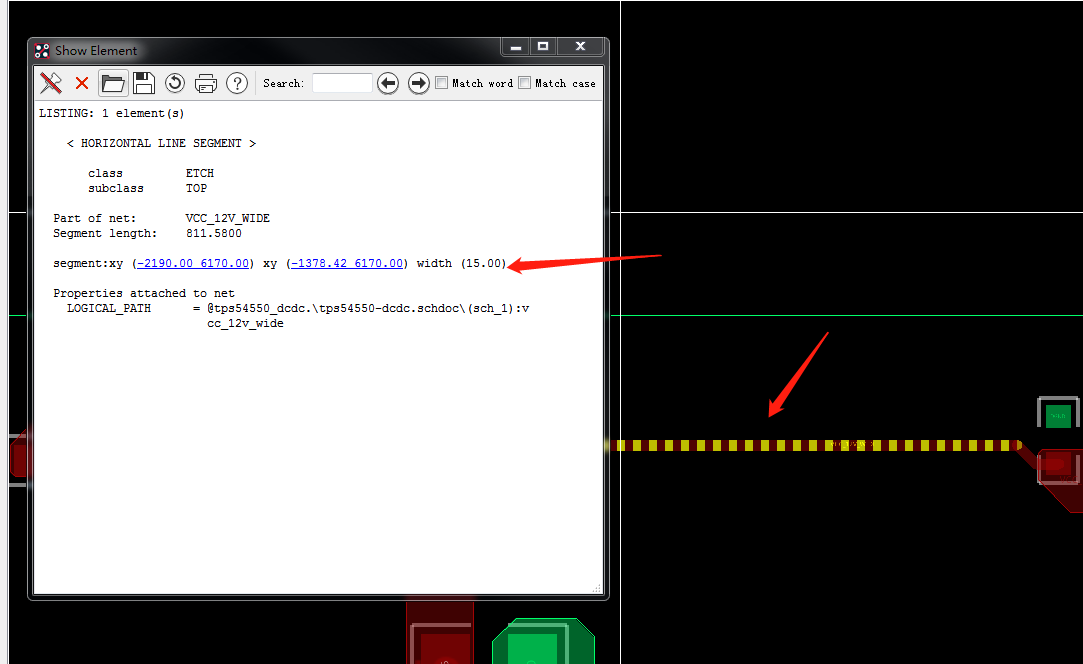

此处电源信号连接15MIL满足不了载流大小,可以直接铺铜连接:输出主干道的器件注意整体中心对齐,都没有调整:配置电阻电容根本没有 注意器件整体对齐性:并且调整下布局,DCDC电源布局要么是一字型,要么L型,不然布线都不方便:电源主干道的铜皮

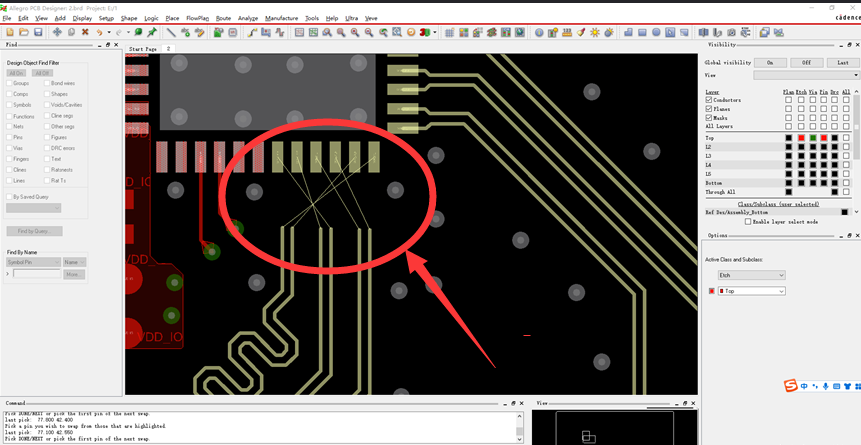

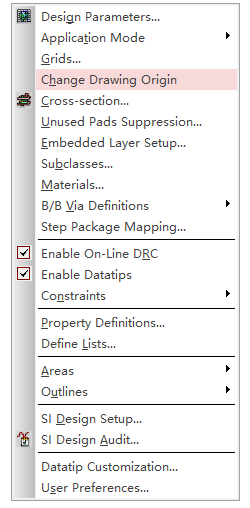

很多电子初学者在使用Cadence ALLEGRO进行Layout设计时,会有一些mipi或lvds等差分走线,在走线时可能为了匹配线序,导致信号网络的走线是交叉,这样做不仅费时费力,还会影响信号质量,那么如何将这些器件的引脚交换过来?如图

差分建议包地 已经打了地过孔直接拉线包上就行了:回流地过孔打在差分打孔换层的两侧:注意此处的扇孔,不要吧内层平面割裂了:差分等长GAP需要大于等于3W:注意差分等长误差:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB

现在,想要学习一门技术,无非就是两种方式,一种自学,另一种是选择一个靠谱的培训机构系统地学习。当然培训机构市场比较鱼目混杂,因此很多人都很好奇:培训班里出来的工程师,能找到一份收入不错的工作吗?这样的人多吗?后续的发展又如何呢?企业招聘工程

在PCB设计完成后,很多电子工程师不仅要将Gerber文件给制造厂商,也要提供坐标文件,保证PCB制造顺利,那么ALLEGRO如何生成坐标文件?其中有哪些文件?下面一起来看看吧!1、要提供那些文件?①Gerber文件中的Pastemask层

电感底部不能放置器件以及走线:把电容都可以塞到IC底部,自己布局处理下。底层器件注意对齐:电感内部挖空处理:IC焊盘扇孔注意下对齐:板上多余没网络过孔或者走线删除掉:GND铺了铜就不用走线连接了:以上评审报告来源于凡亿教育90天高速PCB特

dcdc要求单点接地,如果背面铺铜就不是单点接地了。不要从焊盘侧面出线还有未完成的连接焊盘中心散热地过孔没打以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item

扫码关注

扫码关注