- 全部

- 默认排序

今天,中芯国际透露,14nm工艺已经进入量产阶段,良率正在稳步爬升中,此前还宣布2020年资本支出从43亿美元增至67亿美元,首次公开发行股票(IPO)超额募集资金也达到了256.6亿元。

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

当特斯拉“秘密电池”再度爽约,国产电池厂商将迎来机遇和更大压力-拖了半年后,特斯拉的“电池大会”终于在日前召开。虽然在此次大会上,马斯克介绍了特斯拉诸多亮眼的技术,但令人遗憾的是,此前马斯克预热很久的续航100万英里的电池并没有亮相,转身开始讲述“每千瓦电池生产成本降低56%,让更多人开得起特斯拉”的宏大愿景,这也使得大会结束后,特斯拉股价下跌了5%。

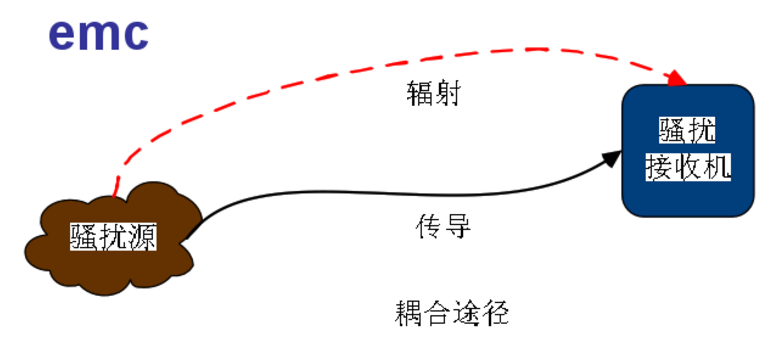

答:EMC,是Electro Magnetic Compatibility的缩写,翻译过来就是电磁兼容性,是指设备或系统在其电磁环境中能正常工作且不对该环境中任何事物构成不能承受电磁骚扰的能力。传感器电磁兼容性是指传感器在电磁环境中的适应性,保持其固有性能、完成规定功能的能力。它包含两个方面要求:一方面要求传感器在正常运行过程中对所在环境产生电磁干扰不能超过一定限值;另一方面要求传感器对所在环境中存在电磁干扰具有一定程度抗扰度。EMC电磁干扰是电子产品困扰电子工程师的一大难题,为了解决电子产品设

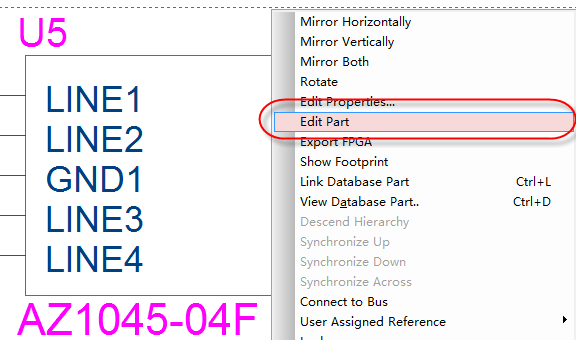

答:第一种方法:直接在原理图中编辑库文件,再更新到原理中,操作如下:第一步,选中你所要更改的元器件,单击鼠标右键,选择Edit Part选项,如图2-55所示; 图2-55 原理图编辑器件示意图第二步,在弹出的该元器件的库的界面中,进行相对应的库文件的修改,如图2-56所示; 图2-56 库文件编辑示意图第三步,按照要求编辑好库文件以后,在页面属性上点击鼠标右键,点击Close选项,关闭掉编辑库文件的页面,如图2-57所示; 图2-57

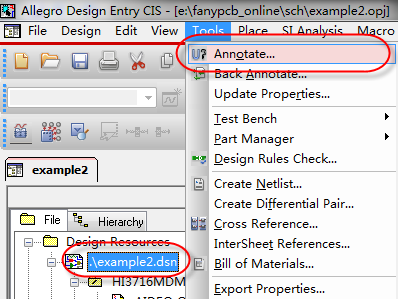

答:第一步,选中整个原理图的根目录,然后执行菜单Tools-Annotate,如图3-56所示,进行原理图选项的编辑;图3-56 原理图进行编译示意图第二步,然后对器件的位号进行复位的操作。在弹出的原理图编译界面中,如图3-57所示,在Action选项中,现将原理图本身已经存在的位号全部复位,点击Reset Part References to “?”,则全部的位号则变成的问号,可参照图3-57所示。 图3-57 原理图编位号复位设置示意图第三步,把所有的位号进

答:在设计原理图时,工程师们都喜欢在原理图中加上自己的独有标志或者是公司的logo,来表示这份原理图是该工程师绘制的或者是该公司的产品,这里我们就教一下大家,如何将公司的logo加入的原理图的Title Block中,具体的操作如下:第一步,Title block是一个全局的变量,存在于每一页的原理图中,我们需要在库里面的Title block加入图片,然后更新到原理图中;第二步,在当前设计的库Design Cathe路径下找到Title block的库,复制到本地的库路径下,才可以对其进行更改

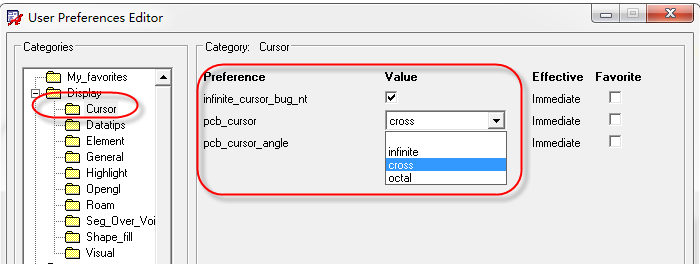

答:我们在设计过程中,使用全屏的大十字光标,有助于我们进行对齐操作,查看也非常方便,这里讲述一下在Allegro软件中如何去使用全屏的十字大光标,具体操作如下:第一步,进入用户设置参数界面,setup-user preferences,在Display选项下找到Cusstor,进入光标设置界面,选择infinite,就是全屏十字大光标,如图5-175所示;

答:在Allegro软件中,所铺的铜皮全部都是动态铜皮,在进行Etch显示的时候,包括走线、铜皮都会显示,在前面的问答中我们讲解了如何将铜皮全隐藏不显示,但是,这样不方便走线设计,走线时不清楚哪一块有铜皮,这里我们讲解一下,如何设置铜皮不显示,但是在PCB中还是显示铜皮的边框,具体操作如下所示:

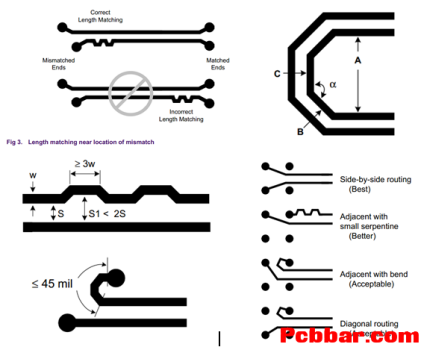

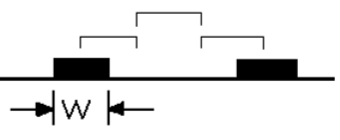

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。

扫码关注

扫码关注