阻抗匹配和阻抗计算是高速PCB设计中的一个常见问题,也是小白初入高速PCB设计中最大的学习难点,今天我们将针对小白的学习难点,归纳总结,整理重点,为小白解惑。

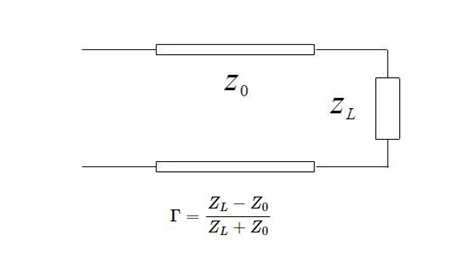

在高速PCB设计中阻抗匹配与否关系将联系到信号的质量优劣,而阻抗匹配是指在能量传输时,电子电路要求负载阻抗和传输线的特征阻抗相等,此时的传输不会有反射现象,这表示所有能量已被负载均吸收,反之在传输中将有能量损失。

PCB走线为什么要看阻抗匹配?

PCB走线关键不再与频率二是看信号的边沿陡峭程度,即信号的上升/下降时间。当信号的上升/下降时间小于6倍导线延时,将被划为高速信号,这种信号必须注意阻抗匹配的问题,导线延时一般取值为150ps/inch。

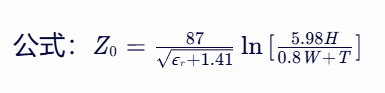

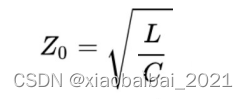

通常来说,信号沿传输线传播过程中,若传输线上各处具有抑制的信号传播速度,且单位长度上的电容也一样,那么信号在传播过程中必然看到完全一致的瞬间阻抗,由于在整个传输线上阻抗维持恒定不变,那么这种特性是叫做该传输线的特征阻抗。特征阻抗是指信号沿传输线传播时,信号看到的瞬间阻抗数值,特征阻抗与PCB导线所在的板层、介电常数、走线宽度、导线与平面的距离等因素有关,与走线长度无关。需要注意的是,特征阻抗可以通过软件来得出。

在高速PCB布局布线中常把数字信号的走线阻抗设计为50欧姆,同轴电缆基带50欧姆,频带75欧姆,对绞线(差分)为100欧姆。

常见的阻抗匹配方式:

1、串联终端匹配

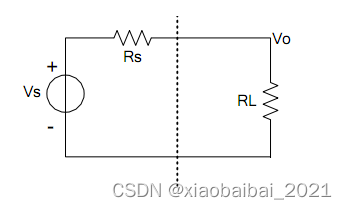

在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

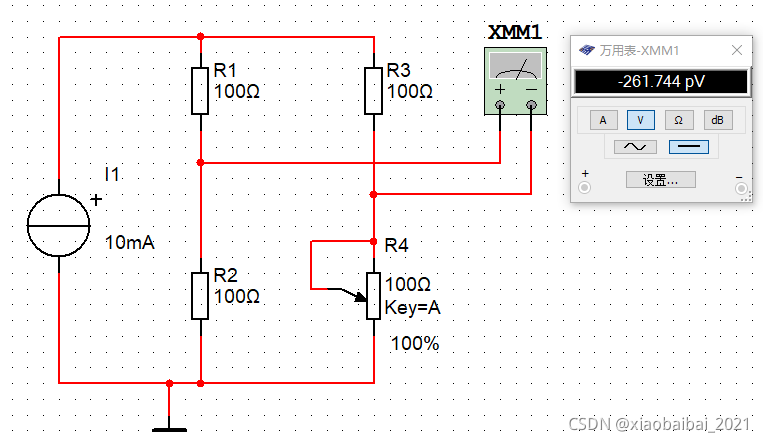

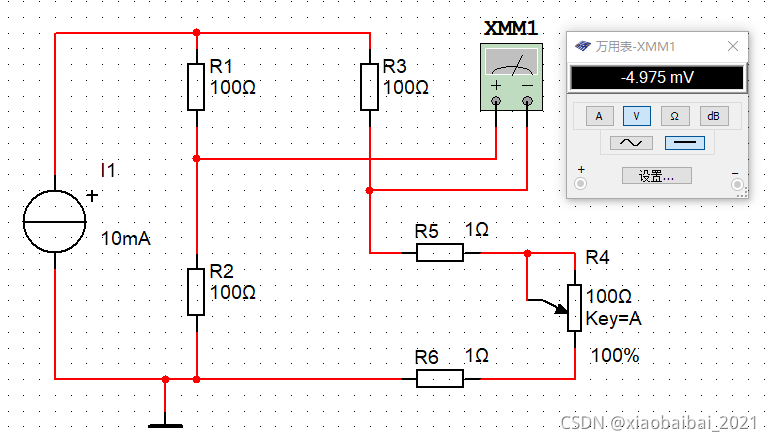

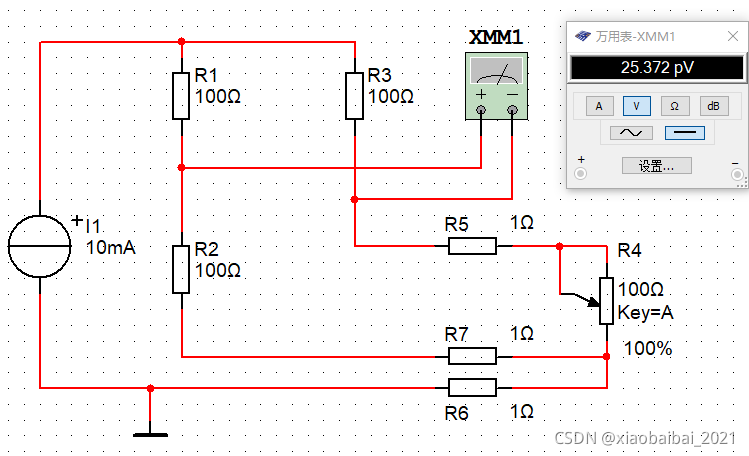

2、并联终端匹配

在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。实现形式分为单电阻和双电阻两种形式。

扫码关注

扫码关注