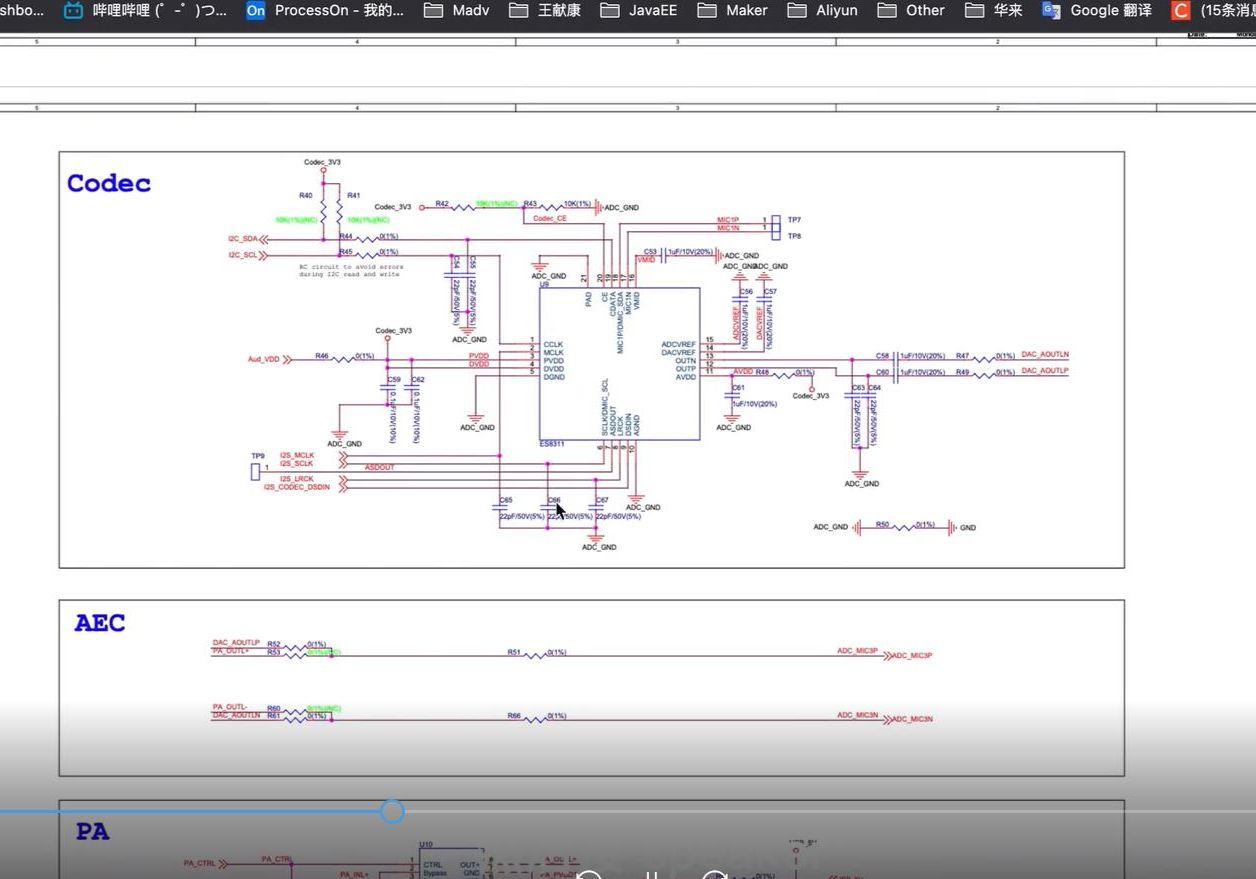

FPGA的硬件设计有别于DSP和ARM系统,较为灵便和随意。只要设计好专用管脚的电路,通用I/O的连接能够自身定义。因而,FPGA的电路设计中也有一些特殊的技巧能够参考。

1.FPGA管脚兼容模式设计

FPGA在芯片选择项时要尽可能挑选兼容模式好的封裝。那么,在硬件配置电路设计时,就需要考虑到怎样适配多种多样芯片的难题。比如,EP2C8Q208C8和EP2C5Q208这两个型号规格的FPGA。其芯片仅有十几个I/O管脚定义是不一样的。在EP2C5Q208芯片上,这好多个I/O是通用I/O管脚,而在EP2C8Q208C8芯片上,他们是开关电源和地信号。以便能确保2个芯片在同样的电路板上都能工作中,大家就务必依照EP2C5Q208的规定来把相匹配管脚连接到开关电源和地平面图。由于,通用的I/O能够连接到开关电源或是地信号,可是开关电源或地信号却不可以做为通用I/O。在同样封裝、适配好几个型号规格FPGA的设计中,一般标准就依照通用I/O总数少的芯片设计制作电路。

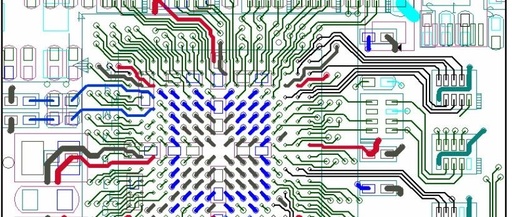

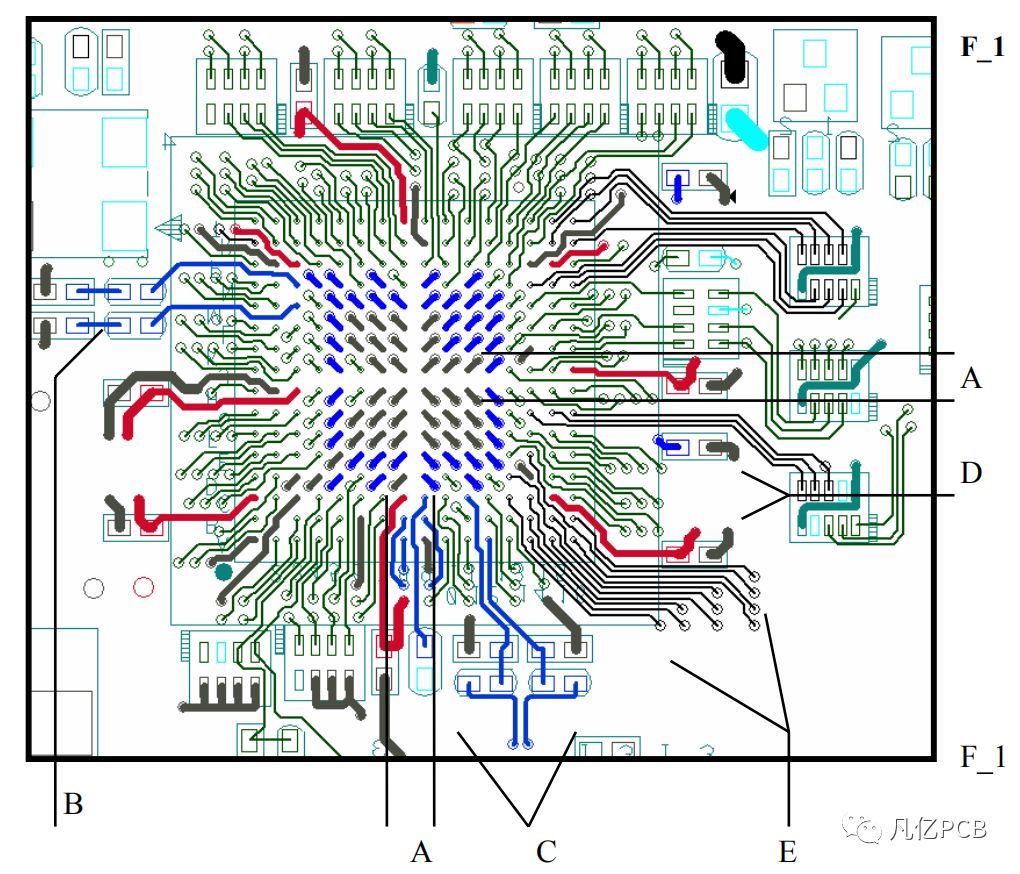

2.依据电路合理布局来分派管脚作用

FPGA的通用I/O作用定义能够依据必须来特定。在电路图设计的步骤中,假如可以依据PCB的合理布局来相匹配的调节电路原理图中FPGA的管脚定义,就可以使中后期的走线工作中更圆满。SDRAM芯片在FPGA的左边。在FPGA的管脚分派时,应当把与SDRAM有关的信号分配在FPGA的左边管脚上。那样,能够确保SDRAM信号的走线间距最短,完成最好的信号一致性。

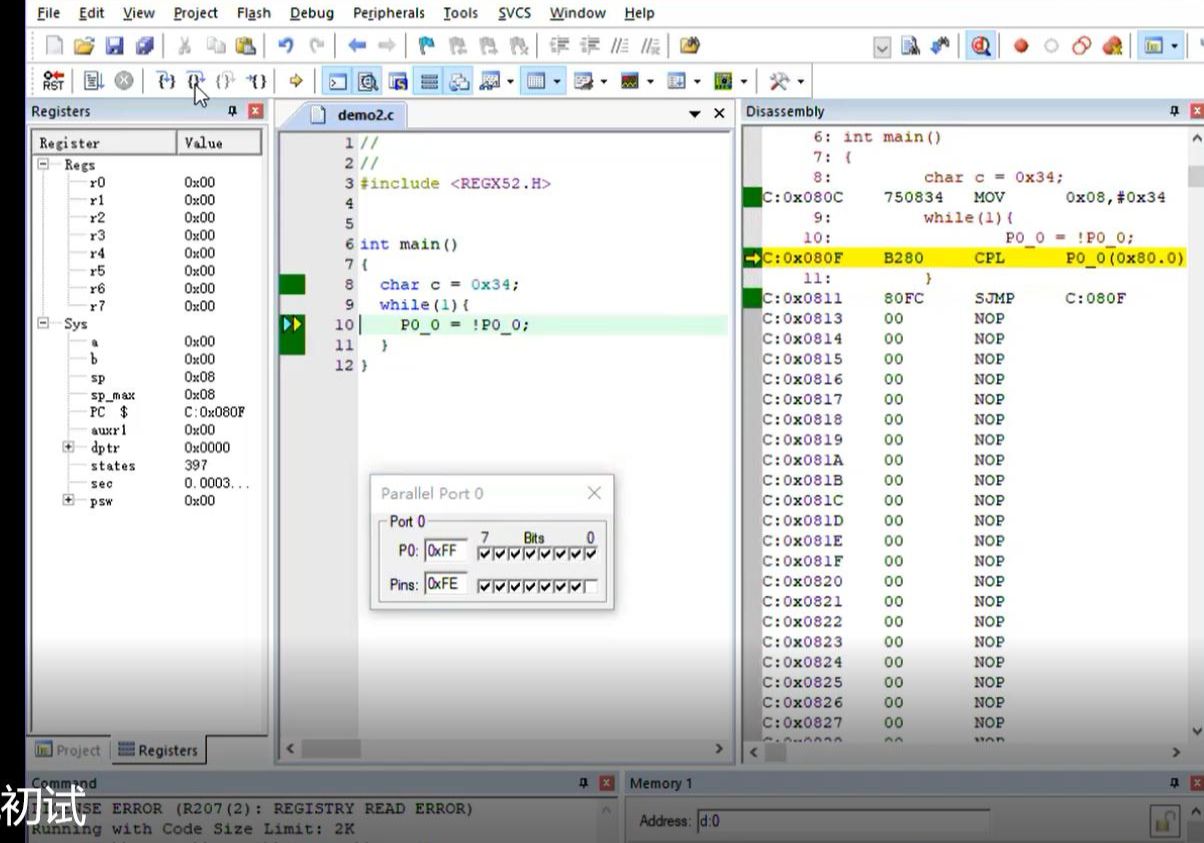

3.FPGA预置测试点

现阶段FPGA出示的I/O总数愈来愈多,除开可以考虑设计必须的I/O外,也有一些剩下I/O沒有定义。这种I/O能够做为预埋的测试点来应用。比如,在检测与FPGA相接的SDRAM工作中时序情况时,立即用数字示波器精确测量SDRAM有关管脚会很艰难。并且SDRAM输出功率较高,立即精确测量会导入附加的特性阻抗,危害SDRAM的一切正常工作中。假如FPGA有预埋的测试点,能够即将检测的信号从FPGA內部特定到这种预埋的测试点上。那样既能检测到这种信号的波型,又不容易危害SDRAM的工作中。假如电路检测全过程中发觉必须飞线才可以解决困难,那么这种预埋的测试点还能够做为飞线的衔接点。

扫码关注

扫码关注