pn结击穿现象

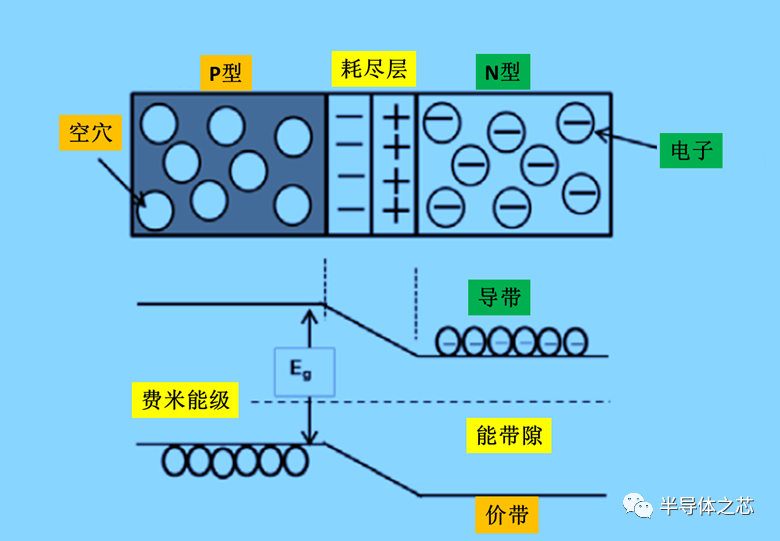

半导体器件的pn结如图1所示。pn结反向偏置时,通过pn结的电流非常小。随着反向偏置电压的增加,一个非常大的电流开始流过一定的电压极限。这种现象被称为反向偏置击穿,发生pn结击穿的电压称为反向击穿电压。形成反偏pn结击穿的物理机制有两种:雪崩击穿和齐纳击穿。

图1 半导体pn结示意图

雪崩击穿

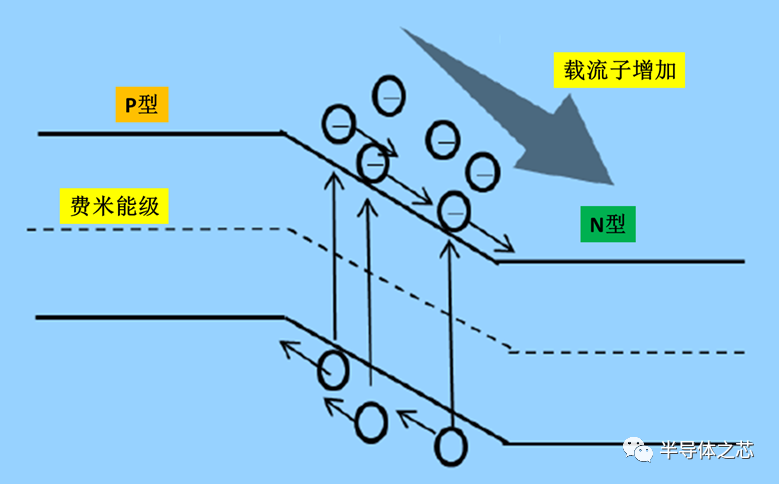

随着反向偏置电压的增加,pn结电场强度增加。当电场足够强时,通过耗尽层的移动电子被加速并获得高动能。当这些移动电子与构成晶格的原子碰撞时,它们的动能激发它们的价电子,产生更多的电子-空穴对。被撞击的自由电子也被加速到足够高的速度,撞击其他原子中束缚的电子,从而产生更多的自由电子,于是就发生了雪崩效应。电子雪崩击穿的物理机制如图2所示。

图2 电子雪崩击穿的物理机制

齐纳击穿

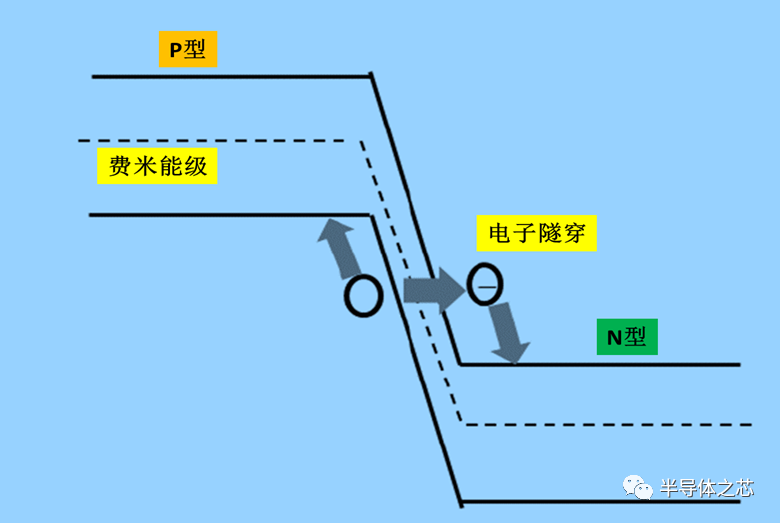

在反向偏压产生的高电场下,耗尽层p区和n区的价带和导带边缘之间的距离减小。足够强的电场可以使电子从p区的价带到n区的导带进行量子隧穿。隧道效应引起的反向电流突然增加称为齐纳击穿。齐纳击穿的物理机制如图3所示。

图3 齐纳击穿的物理机制

雪崩击穿 vs 齐纳击穿

雪崩击穿和齐纳击穿发生在不同的电压下,具体取决于半导体掺杂剂的浓度和温度。齐纳击穿往往发生在产生窄耗尽区的重掺杂结中。相比之下,齐纳击穿不太可能发生在轻掺杂结中。相反,雪崩击穿往往发生在产生更宽耗尽区的轻掺杂结中。温度的升高会减小禁带Eg的宽度或价带和导带之间的带隙,增加电子隧穿的可能性。自由电子的随机运动随着温度的升高而增加。然而,在高温下,自由电子的流动受到与原子碰撞的限制。因此,在较高温度下发生雪崩破坏的可能性较小。

MOSFET雪崩击穿

当向MOSFET施加高于绝对最大额定值BVDSS的电压时,就会发生击穿。当施加高于BVDSS的高电场时,自由电子被加速并带有很大的能量。这会导致碰撞电离,从而产生电子-空穴对。这种电子-空穴对呈雪崩式增加的现象称为“雪崩击穿”。

MOSFET雪崩击穿图解

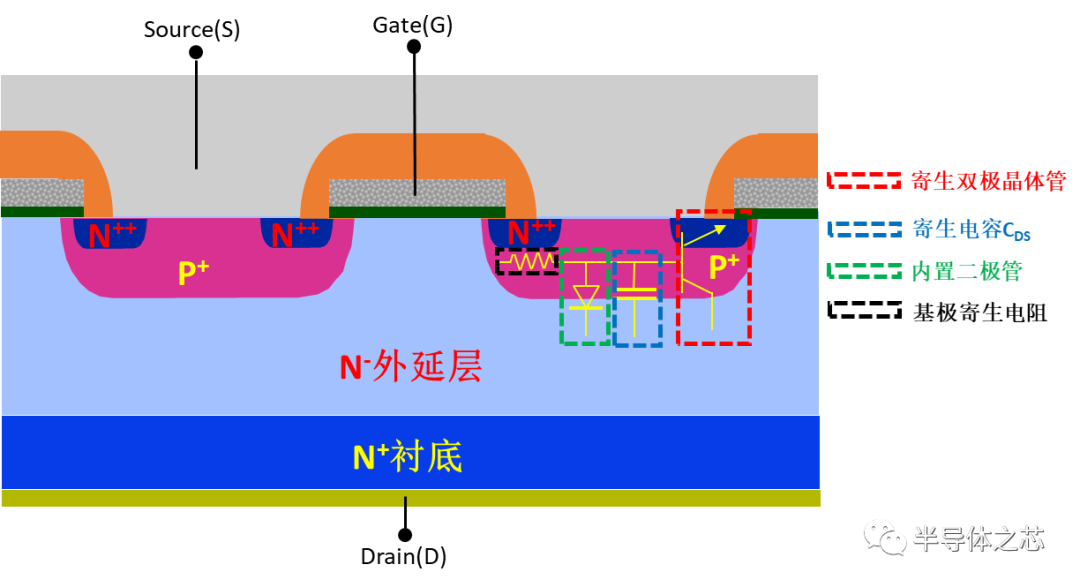

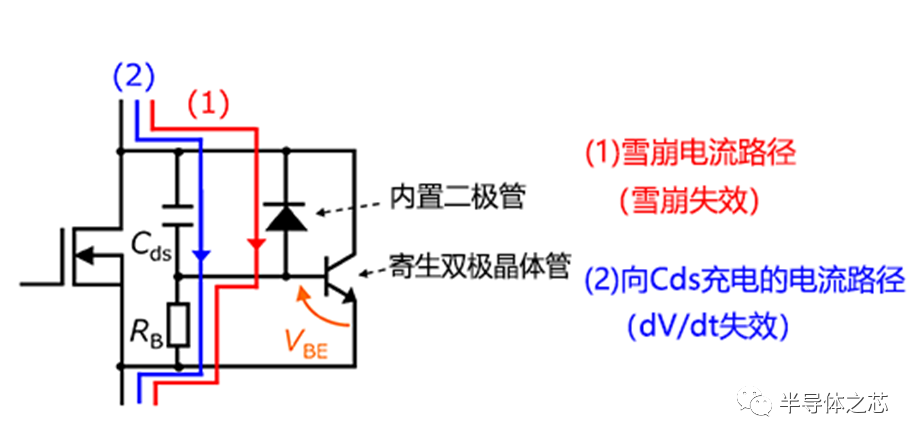

Power MOSFET四层结构的横截面如图4所示,通过MOSFET横截面结构图可以发现MOSFET体内存在基极寄生电阻、寄生电容、寄生双极晶体管和内置二极管。

图4 Power MOSFET四层结构横截面

图4 Power MOSFET四层结构横截面

MOSFET雪崩击穿的等效电路如图5所示,当在MOSFET中的漏极和源极之间施加高于击穿电压的电压时,内置二极管(相当于pn结)进入雪崩击穿并通过雪崩电流。在这种雪崩击穿期间,与 MOSFET内部二极管电流呈反方向流动的电流称为“雪崩电流IAS”,参见下图(1)中雪崩电流路径。

图5 MOSFET雪崩失效电流路径示意图(红色部分)

雪崩失效:短路造成的失效

如上图5所示,IAS会流经MOSFET的基极寄生电阻RB。此时,寄生双极型晶体管的基极和发射极之间会产生电位差VBE,如果该电位差较大,则寄生双极晶体管可能会变为导通状态。一旦这个寄生双极晶体管导通,就会流过大电流,MOSFET可能会因短路而失效。

雪崩失效:热量造成的失效

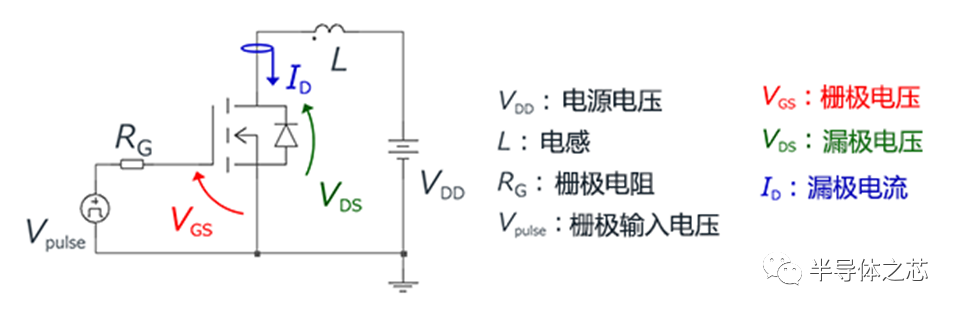

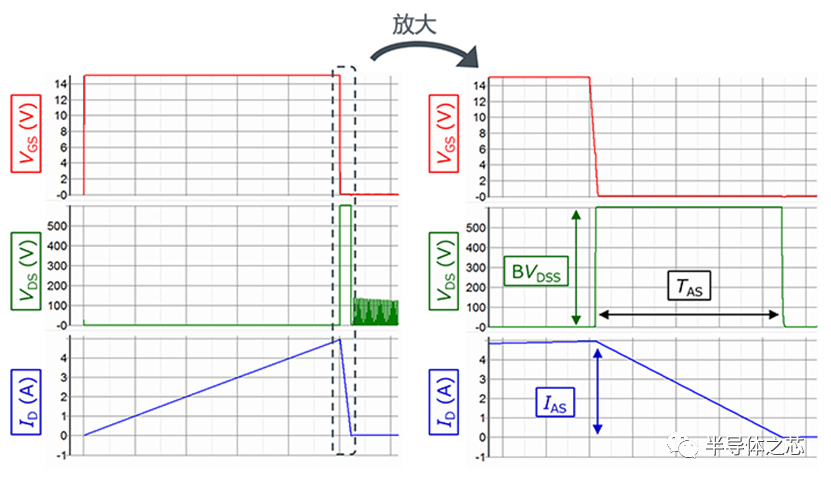

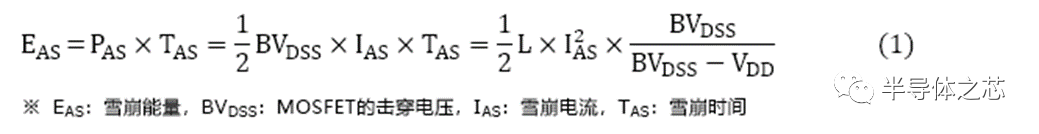

在雪崩击穿期间,不仅会发生由雪崩电流导致寄生双极晶体管误导通而造成的短路和损坏,还会发生由传导损耗带来的热量造成的损坏。如前所述,当MOSFET处于击穿状态时会流过雪崩电流。在这种状态下,BVDSS被施加到MOSFET并且流过雪崩电流,它们的乘积成为功率损耗。这种功率损耗称为“雪崩能量EAS”。雪崩测试电路及其测试结果的波形如下图所示。此外,雪崩能量可以通过公式(1)来表示。

图6 MOSFET的雪崩电路测试示意图

图7 MOSFET的雪崩测试波形及雪崩能量公式

MOSFET避免雪崩失效的方法

一般情况下,有抗雪崩保证的MOSFET,在其规格书中会规定IAS和EAS的绝对最大额定值,因此可以通过规格书来了解详细的值。在有雪崩电流流动的工作环境中,需要把握IAS和EAS的实际值,并在绝对最大额定值范围内使用。

引发雪崩击穿的例子包括反激式转换器中的MOSFET关断时的反激电压和寄生电感引起的浪涌电压等。针对反激电压引起的雪崩击穿,对策包括在设计电路时采用降低反激电压的设计或使用具有更高耐压性能的MOSFET。而针对寄生电感引起的雪崩击穿,改用引脚更短的封装的MOSFET或改善电路板布局以降低寄生电感等都是比较有效的措施。

扫码关注

扫码关注