相信每一个硬件工程师都或多或少的接触过ESD,不同于其它电路,这个玩意儿本身就有点虚,有点让人摸不着头脑,不知道兄弟们感觉如何? 我曾经很长一段时间里面都觉得它有点虚无缥缈,电路设计只会照着相关规则设计,但其实自己了解多少,为什么这么设计,总有一种云里雾里的感觉。网上的资料大多数也都是结论性质的,原因讲得少,看多了就好像自己懂了似的。

先来说几个以前疑惑的点吧,不知兄弟们以前有没有同感

① 静电动辄几千伏,上万伏,直接怼到电路上面芯片为什么不会打坏?即使加了防护器件,是不是有那么一瞬间,芯片还是有被加上几千伏,这不会坏吗?

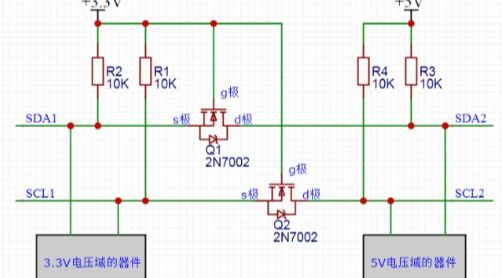

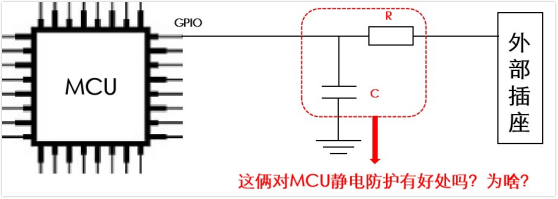

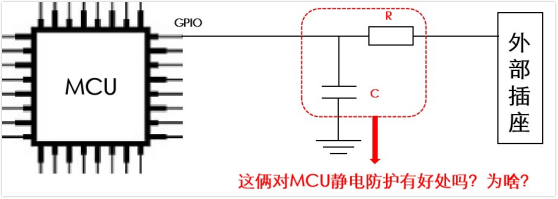

② 为什么MCU/SOC管脚的信号线上串联电阻或电容会对ESD有改善呢?

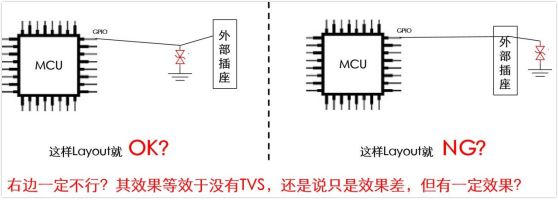

③ 都说接口处的信号要先过ESD/TVS管,然后拉到被保护器件,为什么不这样做效果就不好?那如果受板子实际情况限制,必须这样layout,是一定不行吗?

虽然我们有时候记住一些结论,也能应付下工作,大不了整改,但有时,同样的措施,在这种场景没问题,换个场景又不行,那这些结论到底是OK还是不OK?

下面来说下我的理解吧,不一定对,兄弟们要有自己的判断力,脑子是个好东西。

1、为什么我说ESD比较虚无缥缈?

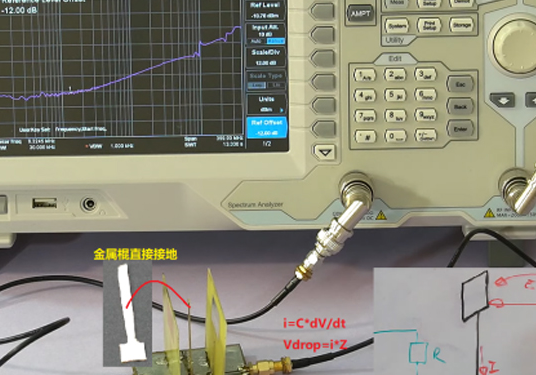

ESD不好处理,我觉得其原因主要在于无法用示波器进行信号测量,因为其放电速度太快,空间干扰严重,示波器测量的结果一般也会受到干扰,无法得到有价值的信息。这一点,导致我们只能通过使用静电设备给我们的产品/板子打静电,打完看其有没有坏,如果坏了,我们才能知道当前扛不住这一结果。至于静电具体是走什么路径泄放的,被保护器件那边的电压波形是什么样的,应该采取什么措施整改,没有一定经验的话,一般难以判断。

另外一点是,很多公司没有专门的ESD静电枪,也就是没有测量产品ESD的能力,只有外出约实验室进行测量,这样搞起来就更为麻烦了。

基于上面的原因,静电防护就不那么好处理,特别是在一些公司,硬件工程师还要肩负起EMC工程师的责任,这些并非我们的专长,所有经常整改起来非常头疼。

所以,我们会背一堆ESD设计规则,然后照着规则去设计,这诚然是有用的,不过,如果我们能有一套理论分析方法,那就更好了,这样不至于遇到问题时完全懵逼。

2、那如任何理论分析ESD呢? 我觉得在脑子里面简单建个ESD电路发生器的模,代入到我们的电路中去分析应该是有效的。

那如何建立ESD电路发生器的模呢?

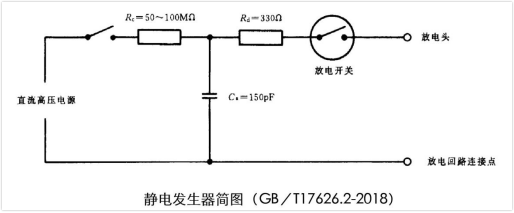

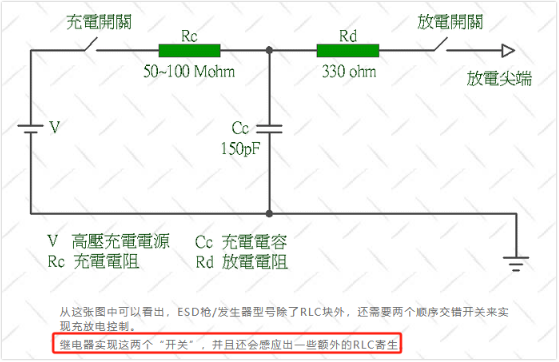

我查了下相关标准文件,国标文件《GB/T17626.2-2018电磁兼容试验和测量技术静电放电抗扰度试验.pdf》——对标IEC61000-4-2,其静电发生器简图如下图所示:

我们回想下我们去测试静电的过程,是不是一下一下打的?比如我们打接触8KV,是将设备调到8KV挡,然后取接触我们的产品或者单板进行放电。用这个图来解释,就是每次打之前,设备用直流高压电源8kV给电容Cs=150pF充好电,然后打开放电开关,这样就进行了一次放电测试。

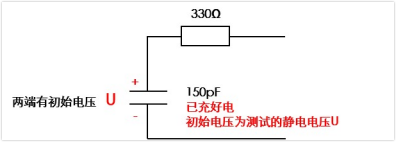

所以呢,我们可以简单构建下面这样的电路,接入到我们自己的电路,然后评估它的破坏性就好了。

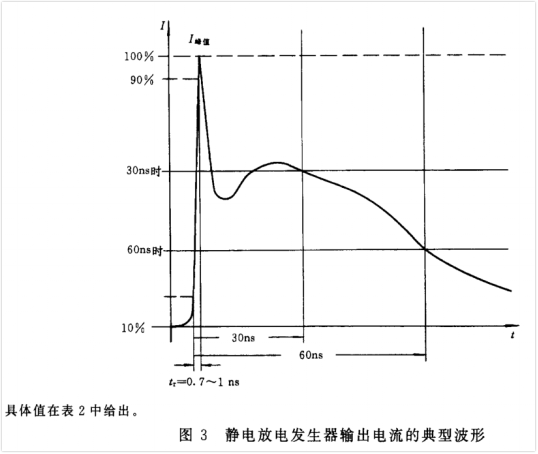

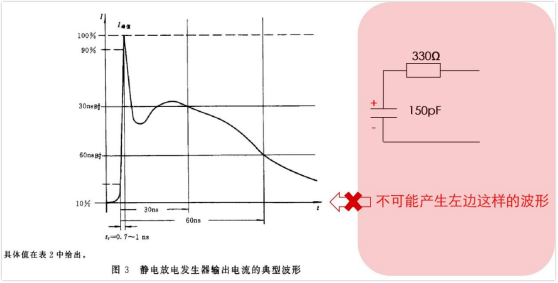

但是这样建模对吗?貌似也不对,因为我记得静电放电波不是很规律的,看下标准文件,典型电流波形如下图:

上面说的电路模型说白了就是个RC电路,是不可能产生这样的电流波形的。

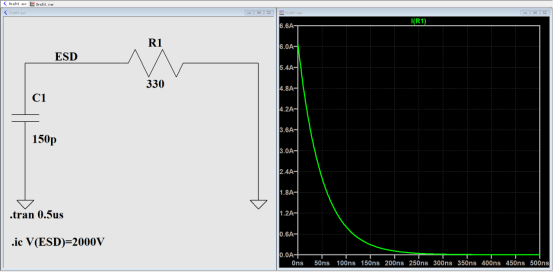

不行的话,我们仿真看下,电容初始电压为2000V,输出端直接短路,我们看电流波形如下图所示,与ESD放电的典型波形差异较大(没有出现上面静电发生器电流波形的两个峰)。

那为什么这样呢?标准文件给出的电路模型还有错?

网上找到一个文章(文末会附出链接),我觉得还是比较靠谱的,放电模型中的两个开关是用继电器来控制的,我前面直接将其当作了理想开关来用了,所以不太对。

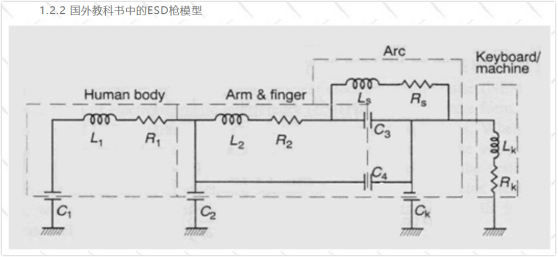

既然模型不对,那我们重新找个模型,我查了些资料,确实也找到了些模型,不过看着都很复杂,比如下面这个。

先不说这个电路准不准确,也太复杂了,如果我们分析的时候,把这个电路模型代入到我们的电路,那分析起来也太困难了,那有没有简单的方式呢?3、简单的模型

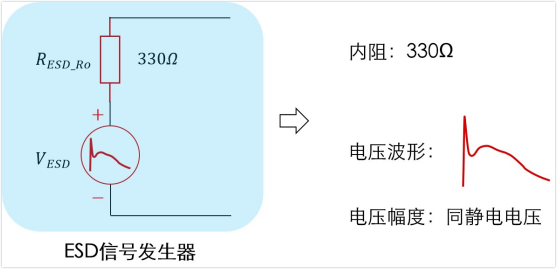

好,我要继续扯淡了,我是这么看的:脑子里面把这个ESD发生器看作是一个信号发生器,其电压波形和电流波形长一样,内阻是330Ω。

这里有个问题没有解释,标准里面,说的是电流波形长成上面这样,而不是电压,为什么我现在这里直接把它当电压?

这里就要看这个ESD放电的典型电流波形是什么条件下测出来的?我估摸应该是短路的时候,但我没有证据。不过我们就以我们正常的电路为例子,如果我们对一个ESD管放电,输出电压会被钳位到一个比较低的电压,比如5V,相对于ESD电压动辄几千V来说,这个5V时可以忽略的,也就是说输出端相当于是短路的。

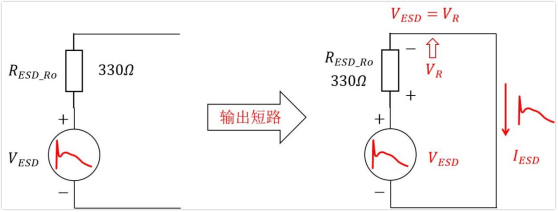

我们把输出端短路,知道其电流波形,因为是串联的关系,这个电流也是流过内阻330Ω的电流波形,电阻的两端的电流乘以电阻就等于电阻两端的电压,因为电阻是常数,所以电阻两端的电压波形也就跟电流波形形状一样。

另一方面,输出短路之后,Vesd直接加到了电阻两端,也就是说,Vesd的电压波形和电阻两端电压一样,所以Vesd的波形就和原来的电流波形形状一样。

以上描述有点绕,看下图应该很容易明白。

现在我们有了模型,不过我们也不太好分析,因为这个波形太不规则了,那怎么办呢?

下面就要用到信号的频谱了,那这是什么原理呢?其实以前专门写过一篇文章,不明白的可以去瞅瞅,就是这两个:《信号在脑子里面应该是什么样的(一)》;《信号在脑子里面应该是什么样的(二)》4、ESD信号的频谱

一般认为,ESD的频谱是宽带的(指的是各种频率分量都有),频率范围大概是几十Mhz到500Mhz,总之,其算是高频信号。

从标准文件中知道,ESD波形具有0.7~1ns的上升沿,通过上升沿跟最大带宽的计算公式0.35/tr,可得最大带宽约为:0.35/0.7ns=0.5Ghz=500MHz。

现在我们有了模型,以及信号的频谱,下面我们拿着这两个东西去分析我们的具体的电路。

5、直接用这个模型回答开篇的第2个问题:为什么串电阻和并联电容能够改善ESD?

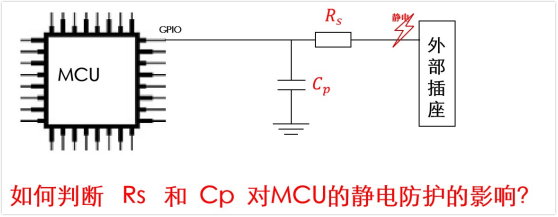

如上图,我们有一个电路,MCU的GPIO管脚接到了外部插座上,一般来说,这种插座就是静电的薄弱点,我们现在串联了Rs和Cp,那么这个Rs和Cp是否对静电有影响呢?

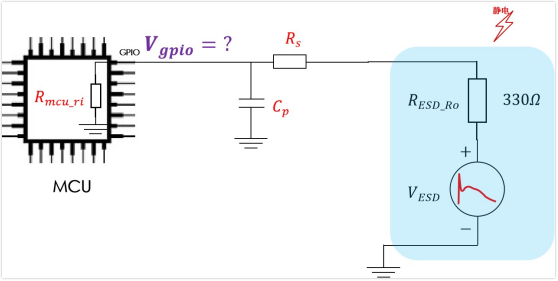

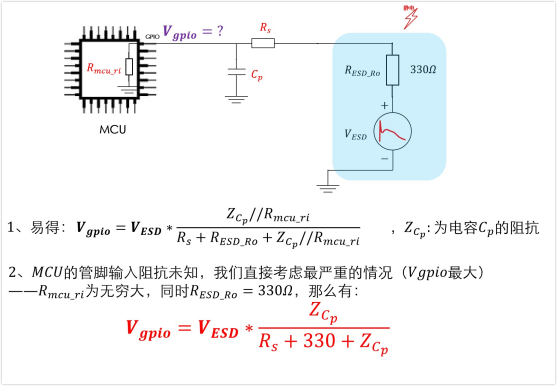

我们按照前面说的,把静电发生器的等效电路接进来分析,假设MCU的输入阻抗为Rmcu_Ri,最终电路等效如下图:

Rs,Cp对静电是否有作用,我们只需要看GPIO这个管脚的电压Vgpio就好,电压越低,说明效果越好。

有了上面的模型,其实我们就可以很轻松得到Vgpio的电压,可以列出下面的公式:

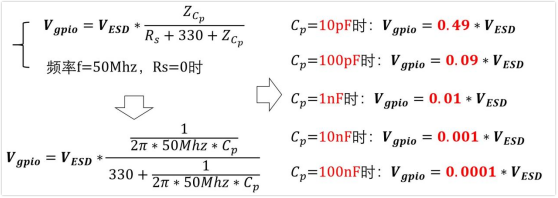

公式有了,但是,这里需要再次强调下,Vesd是不规则的波形,我们要将其进行傅里叶分解为正弦波,也就是得到其频谱,因为只有这样电容的阻抗才有意义,才能用公式Zcp=1/(j*2π*f*Cp)得到电容的阻抗,我们上述的公式计算才能得到结果。前面知道,Vesd带宽频谱为几十Mhz到500Mhz。a、我们先来看滤波电容Cp的值对静电防护的影响

从上面公式可以看出,Cp阻抗越小时,其容抗就越大,Vgpio的值越大,也就是说静电效果越恶劣。与此同时,频率越低,电容阻抗越大。因此,恶劣的情况为信号是频率低的时候,而Vesd的带宽是几十Mhz到500Mhz,我们分析恶劣的情况,那么取最低频率几十Mhz。

问题来了,这个几十Mhz是多少呢?我没有找到官方的说法,其实也不重要,我们反正是定性分析,取个50Mhz吧。

固定了频率,我们也将Rs固定下来吧,也取最恶劣的情况,Rs=0;

有了上面的条件:f=50Mhz,Rs=0。我们看不同容值Cp情况下 Vgpio的值:

可以看到,电容越大,对静电越友好。

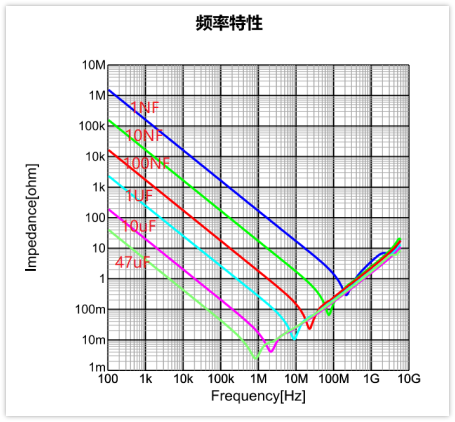

一般来说,加个nF级别的就对静电有好的抑制作用。再往上收益可能也不明显,因为上面的计算是基于理想公式的,我们知道实际上电容是非理想的,高于一定频率后呈感性,阻抗不降反增,这些我在讲电容的时候也是有提到的,想详细了解可以去翻翻我笔记里面陶瓷电容相关的文章,现在兄弟们简单看下下面这个图就明白了。

另外一方面,这个滤波电容在电路中可能会影响我们有用信号的传输,因此具体能加多大的电容肯定是要结合具体电路综合考虑的。

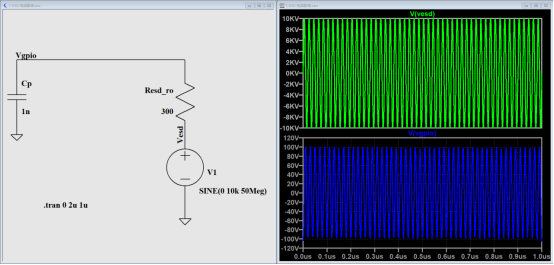

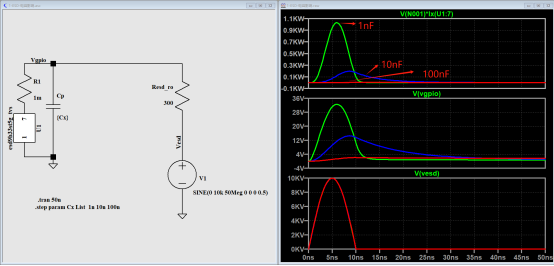

简单仿真验证下,确认下计算是否正确,仿真Cp=1nf的情况如下图(Vesd=10kV@50Mhz,Rs=0,Cp=1nF时):

可以看到,Vesd=10kV时,Vgpio=100V,满足公式Vgpio=0.01*Vesd,验证了上面公式的准确性。

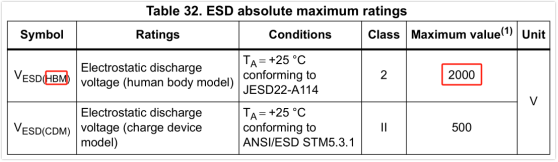

虽然我们通过电压的高低能够得出ESD的能力,不过呢,还有个问题,如果芯片管脚那里的电压真的是100V的话,那不用说,芯片早就挂了。考虑实际情况,芯片内部一般也会有ESD防护,以最常见的MCU芯片stm32f103为例子,其ESD能力为2000V,如下图所示。

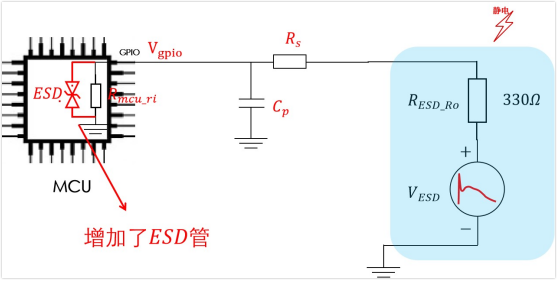

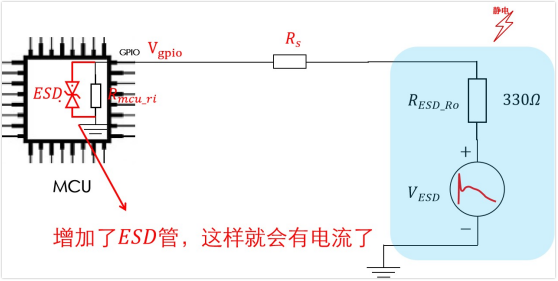

这个芯片供电电压为3.3V,我们就假设其内部是接了一个3.3V的ESD管来做到的2000V的芯片能力的。根据这个,我们修改下模型如下图,放入一个3.3V的ESD管。

放了ESD管之后了,可以想象,Vgpio会被这个ESD钳位到一个比较低的电压,肯定没法通过Vgpio电压值来判断ESD能力,那现在如何衡量ESD性能呢?

也容易想到,可以通过ESD管吸收的能量,或者说是功率来判断,如果说ESD管承受的功率越大,那么其承受的压力也就越大,也就是说ESD性能差。

放了ESD管之后,就不好计算了,我们直接仿真看结果吧(注:下图中R 1是用于软件测试电流用的,1mΩ不影响结果;ESD管使用的是型号安森美的3.3V ESD器件esd9b33st5g,模型可以在其官网下载,LTspice如何导入第三方模型可以看我的笔记文档的第9.1.4章节,这里不再描述详细过程)。

从功率上看,1nF时ESD管承受的瞬间功率是1kW左右,10nF时是200W左右,100nF时就太小了,说明电容越大,ESD管压力越小,芯片更不容易坏,也就是防护能力越好。

b、串联电阻Rs的影响

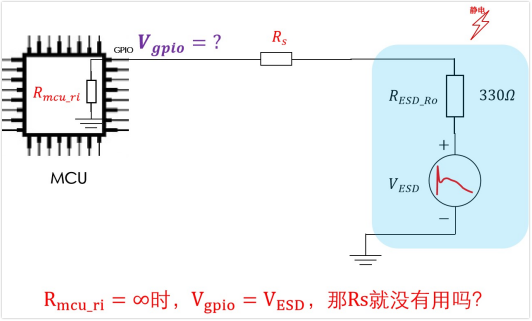

说完了电容,下面来看下串联电阻Rs的影响。用下面的模型,可以看出,如果假设MCU的管脚输出阻抗为无穷大,那么电路都是开路的,Vgpio=Vesd,不管有没有串联电阻Rs。

那Rs是不是没有用呢?当然不是,因为如果我们令Rmcu_ri=∞时,整个模型是开路的,根本就不会发生放电的事件,而事实上我们去打静电,肯定会有放电发生,也就是会有回路。

所以我们要结合更真实的情况,在MCU那里放个ESD管,看这个管子承受的功率大小就行。

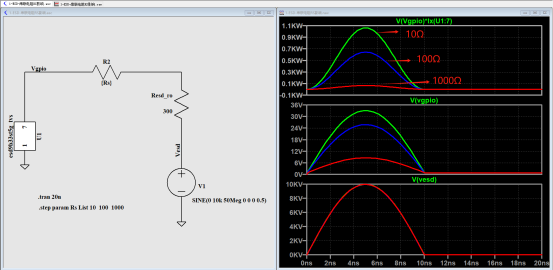

我们还是仿真下看结果

可以看到,串联电阻越大,那么ESD管承受的功率——压力越小。说明串阻越大,对于MCU的防护是更好的。

为什么会这样呢?也很容易看出来,整个链路是串联的关系,如果Rs越大,那么回路的整体阻抗也越大,电流就越小,ESD管的压降也会越小,进而功率越小,芯片里面ESD管受到的压力也越小,进而防护能力越强。

小结

文章开头的三个问题,第1个问题通篇看完的话应该就明白了,就不专门说明了,第2个问题也作出了解释,至于第3个问题,限于篇幅,就留待下次了。

再声明下,文章的主要观点并不是很严谨,有些条件也是假设(比如ESD的典型波形我猜测可能是直接输出短路的时候测的),我只是估摸是这样,并没有求证,兄弟们可以结合自己的经验去印证是不是这样,总之不要尽信。

扫码关注

扫码关注