简介

在高性能计算 (HPC) 和生成式人工智能 (AI) 应用的巨大需求推动下,预计到 2026 年,数据中心的耗电量将翻一番,以支持互联网活动的爆炸式增长和人工智能的蓬勃发展。与此同时,移动设备以及自动驾驶汽车、智能工厂和沉浸式通信服务等新兴技术正在产生前所未有的海量数据,需要对其进行处理和分析。

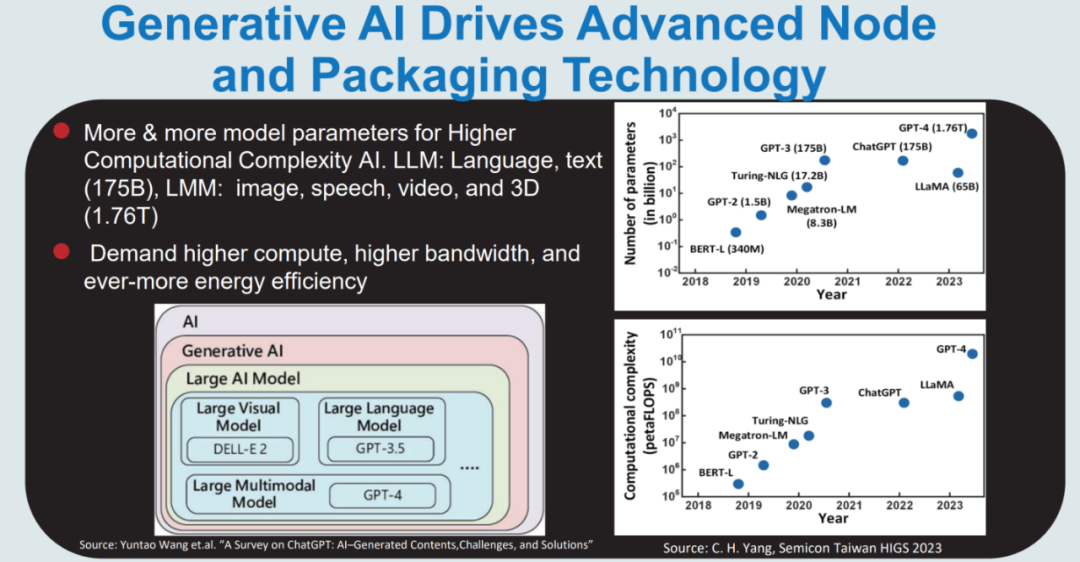

这场数据革命的核心是人工智能模型的突破,如大型语言模型(LLM)和多模态模型,可以生成类似人类的文本、图像、语音、视频和 3D 内容。训练这些模型需要大规模的计算能力,只有通过不断创新的半导体技术才能实现。从 Deep Blue 到 AlphaGo 再到 ChatGPT,人工智能的每一次飞跃都得益于处理器、内存和系统集成的进步。

克服计算、内存和功耗障碍

然而,要实现高性能计算和生成式人工智能的全部潜力,还面临着被称为 "计算墙"、"内存墙 "和 "电源墙 "的重大挑战。随着内核数量和晶体管密度的增加,内存带宽、功耗和并行扩展方面的限制成为瓶颈。

对更高计算性能和能效的不懈追求已成为半导体行业未来十年的主要关注点。要克服这些障碍,需要在多个层面进行创新:

1.通过采用新型架构和材料的设计技术协同优化 (DTCO) 实现晶体管扩展

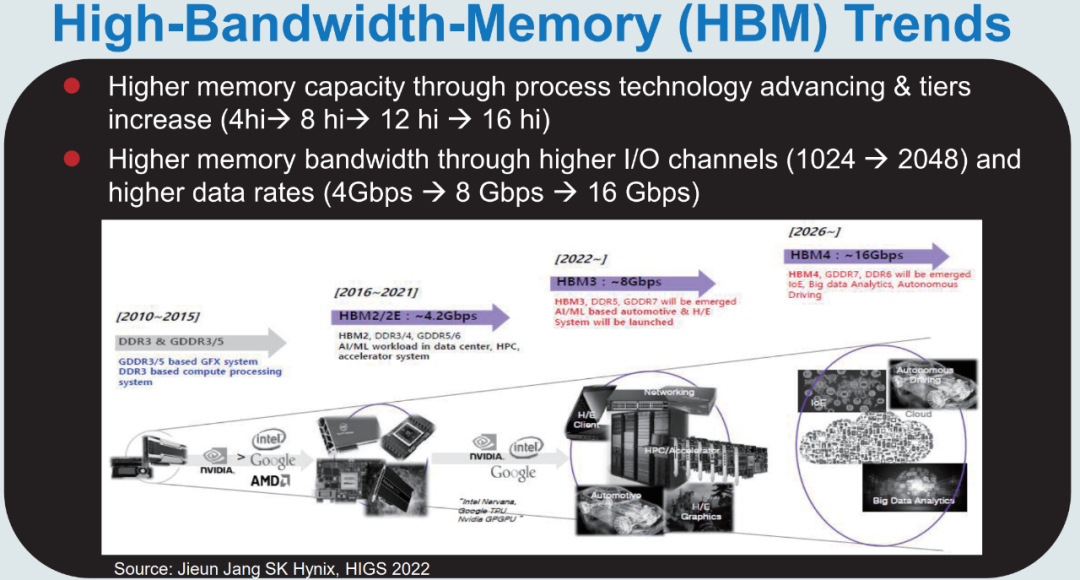

2.高带宽内存(HBM)等先进内存技术 3.

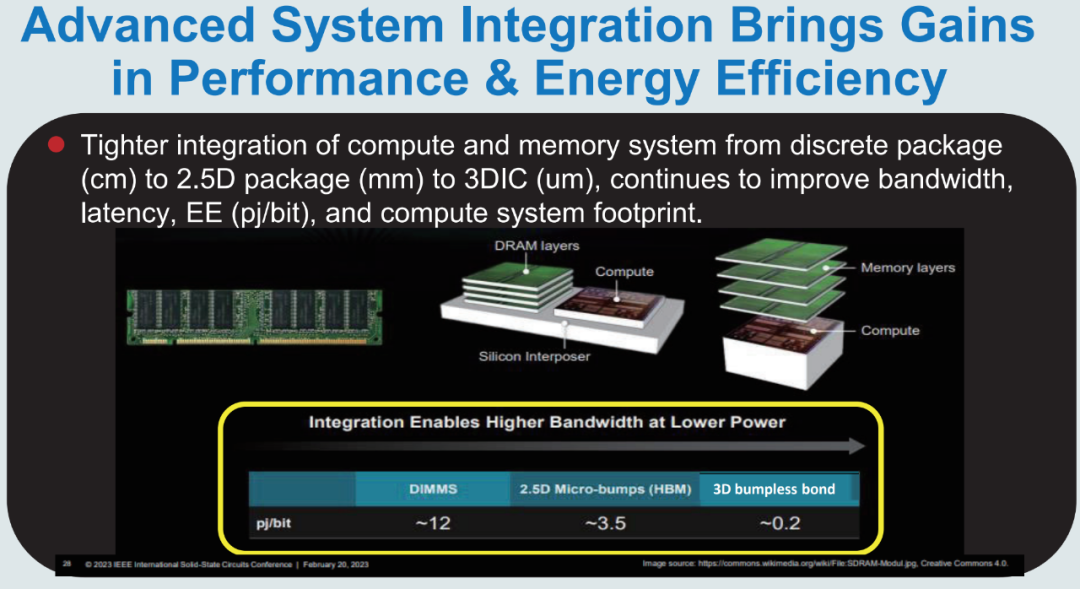

3.采用 2.5D 和 3D 集成电路 (3DIC) 封装的先进系统集成

4.新的互连技术(电气和光学)

5.颠覆性的热管理材料和解决方案

将计算、内存和互连紧密结合起来的整体系统集成方法是实现性能、带宽、能效和外形尺寸大幅提升的关键。

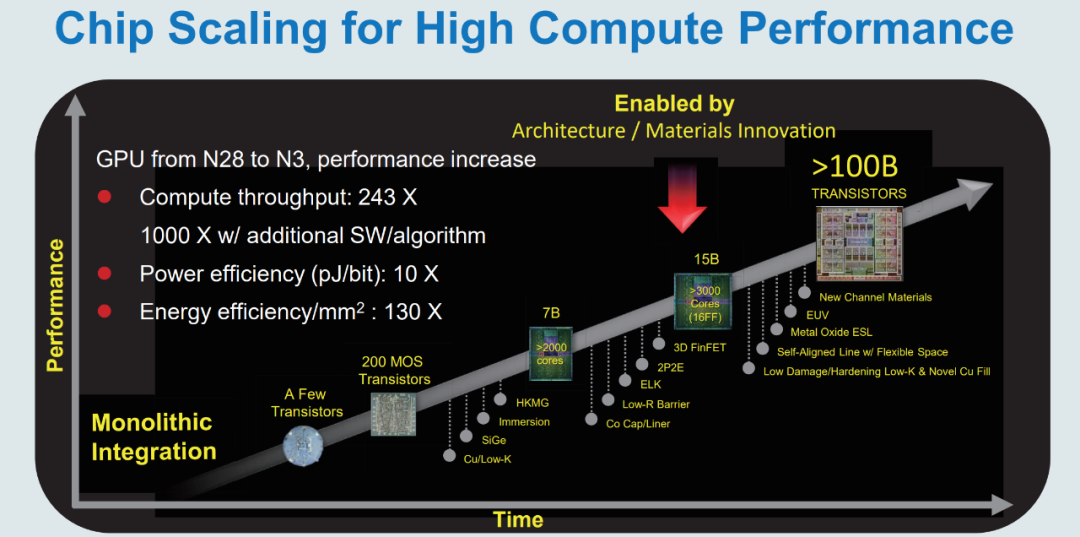

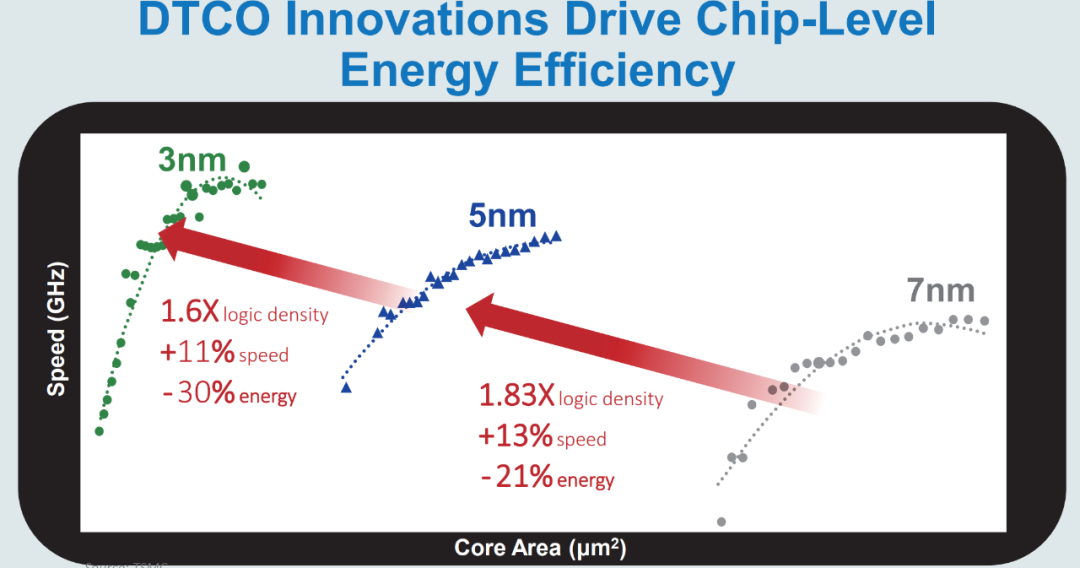

用于高能效 SoC 的 DTCO

在晶体管层面,3 纳米、5 纳米和 7 纳米工艺节点的 DTCO 创新技术使逻辑密度提高了 1.6-1.8 倍,性能提升了 11-13% ,能耗比前几代产品降低了 21-30% 。如下图所示,从 28 纳米到 3 纳米节点,芯片级能效有了显著提高。

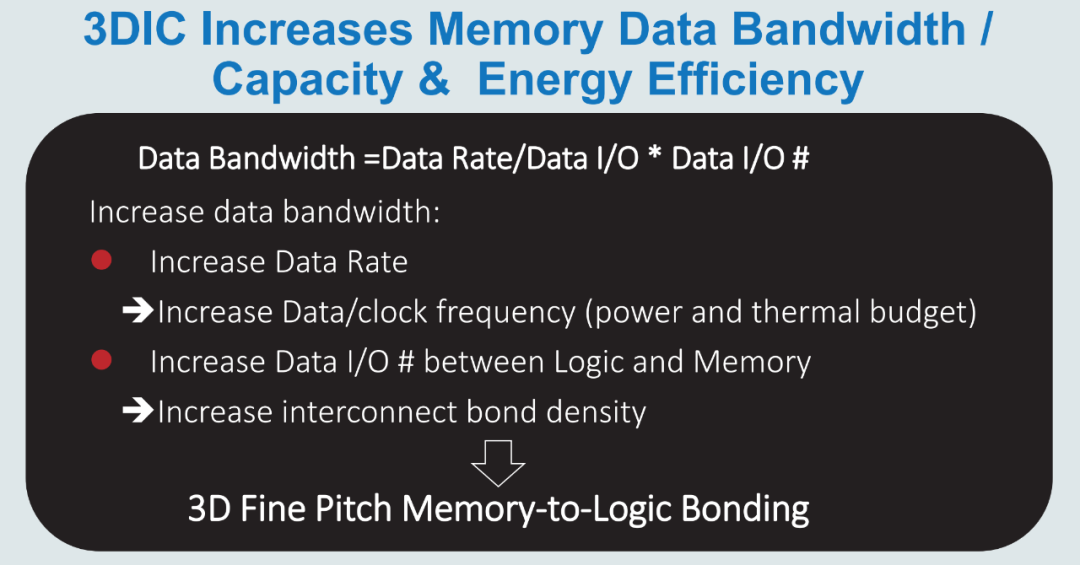

HBM 等内存技术也在快速发展,通过增加内存层级(4-hi 到 16-hi)提高了容量,通过增加 I/O 通道(1024 到 2048)和更快的数据传输速率(4Gbps 到 16Gbps)提高了带宽。下图显示了先进 DRAM 与传统内存类型相比的能效提升。

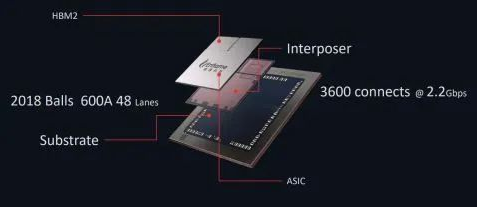

面向高性能计算的 2.5D 系统集成

为解决内存带宽瓶颈问题,2.5D 系统集成封装已成为强大的解决方案。这些基于interposer的封装可以利用三种主流技术并排集成多个芯片(CPU、GPU、AI 加速器)和 HBM 堆栈:

1.带有硅通孔(TSV)和线路后端(BEOL)再分布层(RDL)的硅插片

2.带有嵌入式本地互连芯片的基片interposer

3.聚合物 RDL interposer,可选择带本地互连芯片

如图所示,2.5D 封装的主要优势包括通过集成更多芯片来提高计算密度,通过集成更多 HBM 堆栈来提高内存带宽,以及通过设计分区来优化产量和成本。

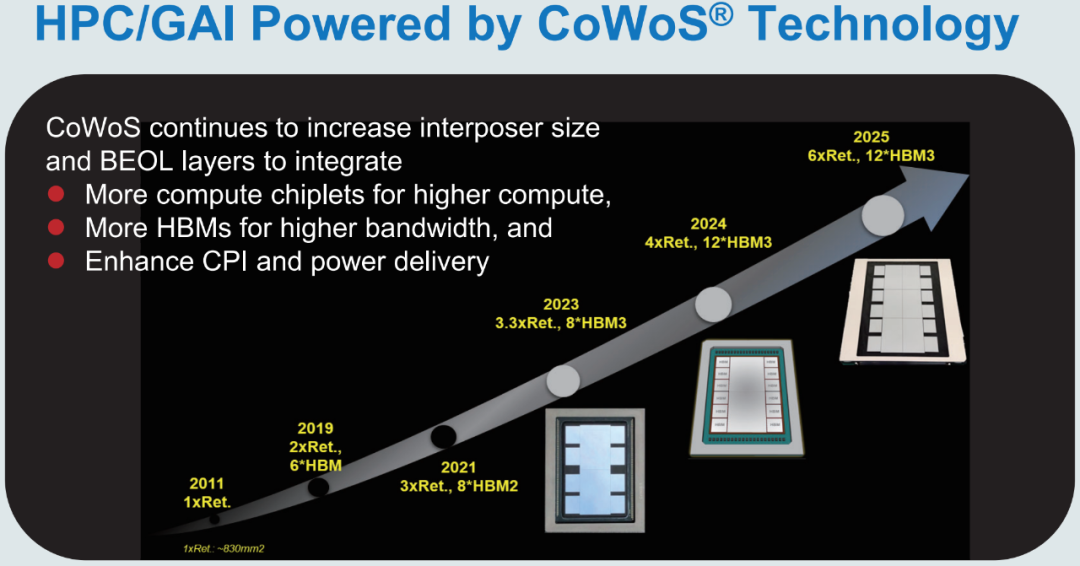

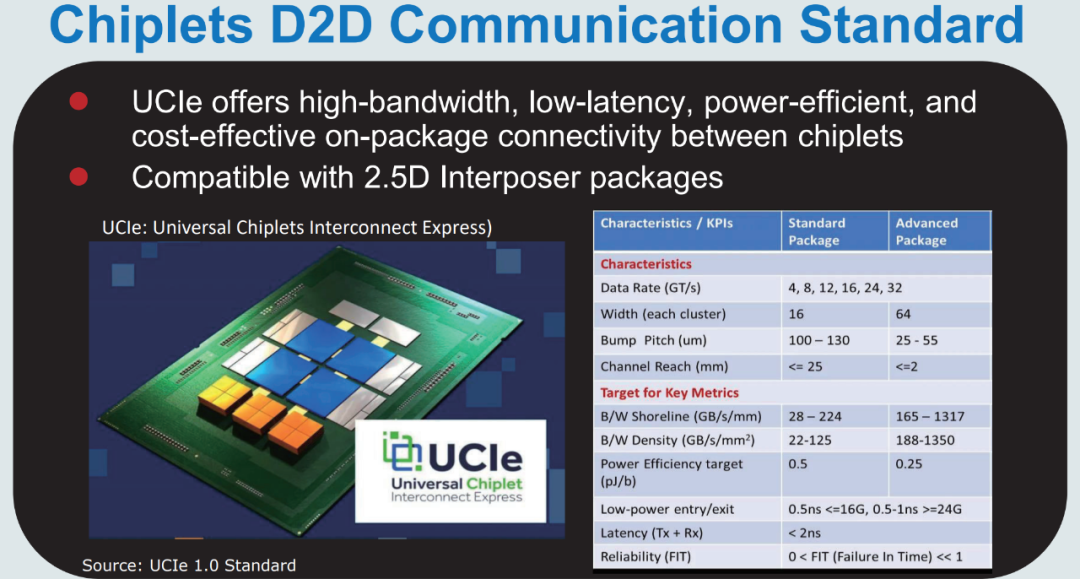

晶圆基板上芯片(CoWoS)技术在扩大中间件尺寸和 BEOL 层以容纳更多芯片和 HBM 方面发挥了重要作用。通用芯片互连 Express (UCIe) 等标准的出现,使这些 2.5D 封装内的芯片到芯片通信具有高带宽、低延迟和高能效的特点。

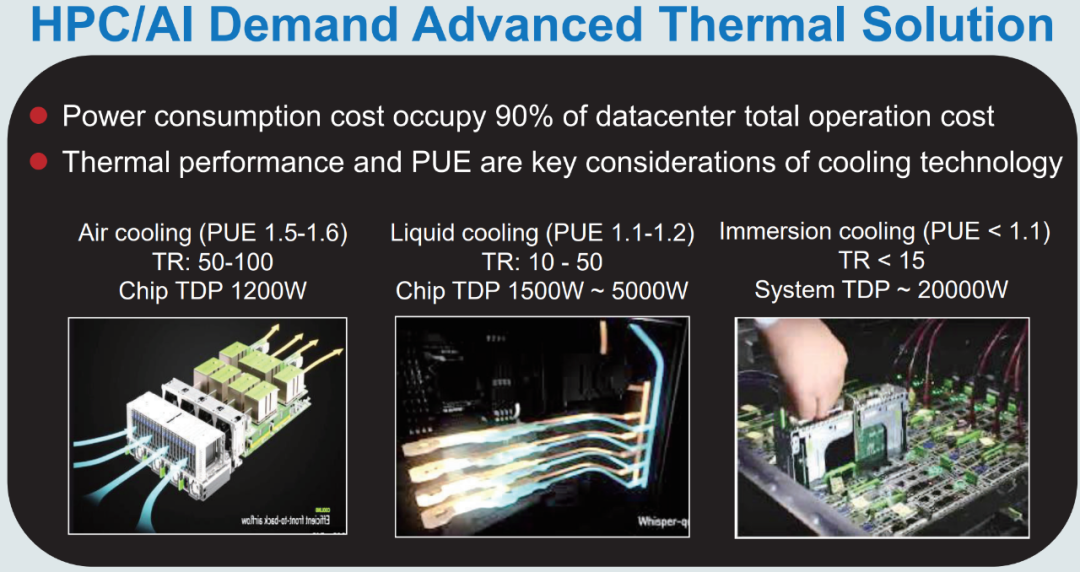

然而,随着高性能计算应用中芯片热设计功率(TDP)超过 1500W,需要液冷和浸入式冷却系统等先进的散热解决方案,以保持低于 1.2 的合理功率使用效率(PUE)值。

3DIC 实现极高的内存带宽和能效

虽然 2.5D 集成提供了实质性的改进,但消除内存瓶颈的最终解决方案是 3D 集成电路 (3DIC) 技术。通过使用细间距微凸块或无凸块键合技术垂直堆叠逻辑和存储器芯片,3DIC 可以实现前所未有的互连密度,每平方毫米超过 100 万个凸块。

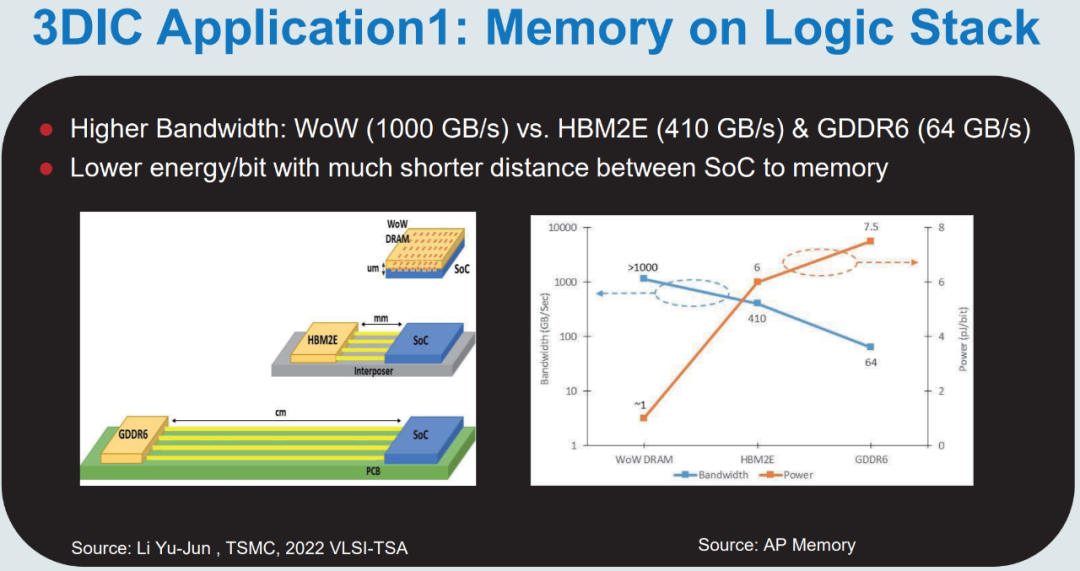

如图所示,3DIC 集成实现了以下功能:

1.内存带宽呈指数级增长,晶圆上堆叠(WoW)可达 1000 GB/s,而 HBM2E 为 410 GB/s。

2.由于互连长度缩短,每比特传输能耗大幅降低

3.灵活的堆叠配置,如面对面 (F2F)、背对背 (F2B)、晶圆芯片 (CoW)、晶圆芯片 (WoW)、逻辑芯片 (LoL) 和逻辑内存 (LoM)

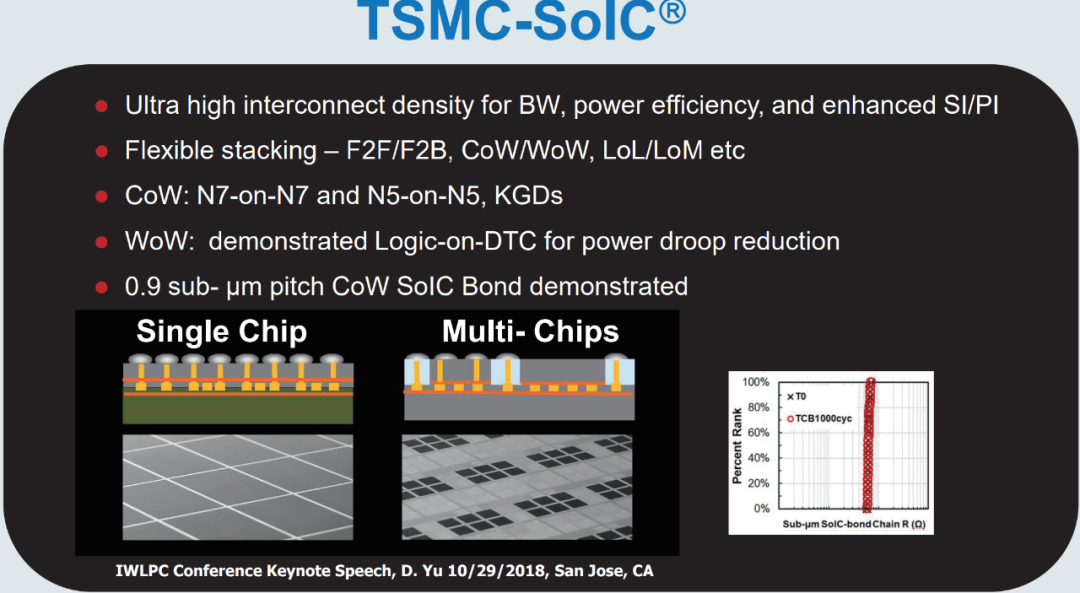

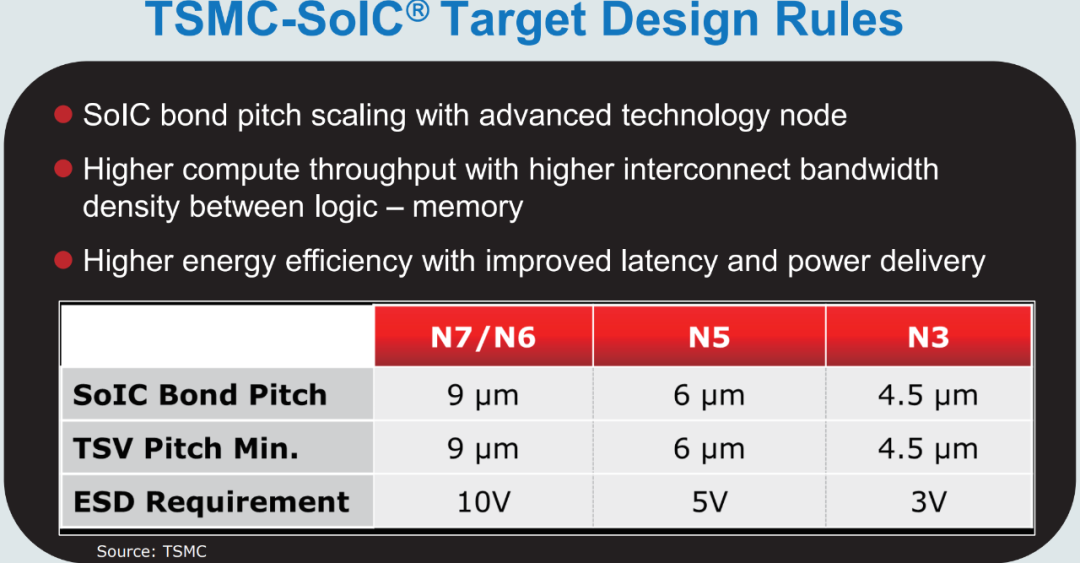

台积电已证明其专有的片上晶圆系统集成芯片(SoIC)技术的键合间距低于 0.9 μm,实现了从成本敏感型移动设备到极端高性能计算应用的 3DIC 解决方案。

3DIC 集成带来的计算吞吐量和效率提升非常显著。下图显示了系统从分立封装过渡到 2.5D interposer,最后过渡到采用亚微米间距无缓冲键合技术的 3DIC 配置时,带宽、延迟、能效和外形尺寸的改善情况。

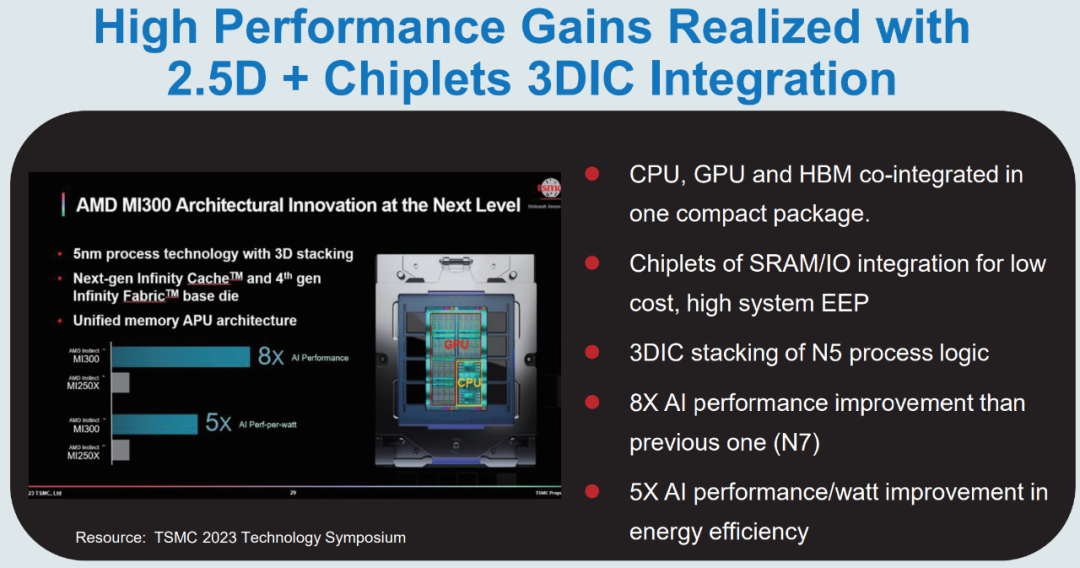

一些实际例子展示了巨大的潜力: 与 HBM2E 的 410 GB/s 和 GDDR6 的 64 GB/s 相比,逻辑内存 3DIC 堆栈可提供超过 1000 GB/s 的带宽。台积电最新推出的基于芯片的处理器采用了 2.5D 和 3DIC 集成技术,其人工智能性能比上一代产品提高了 8 倍,每瓦性能提高了 5 倍。

利用 SoIC 和 CoWoS 协同集成扩展三维空间

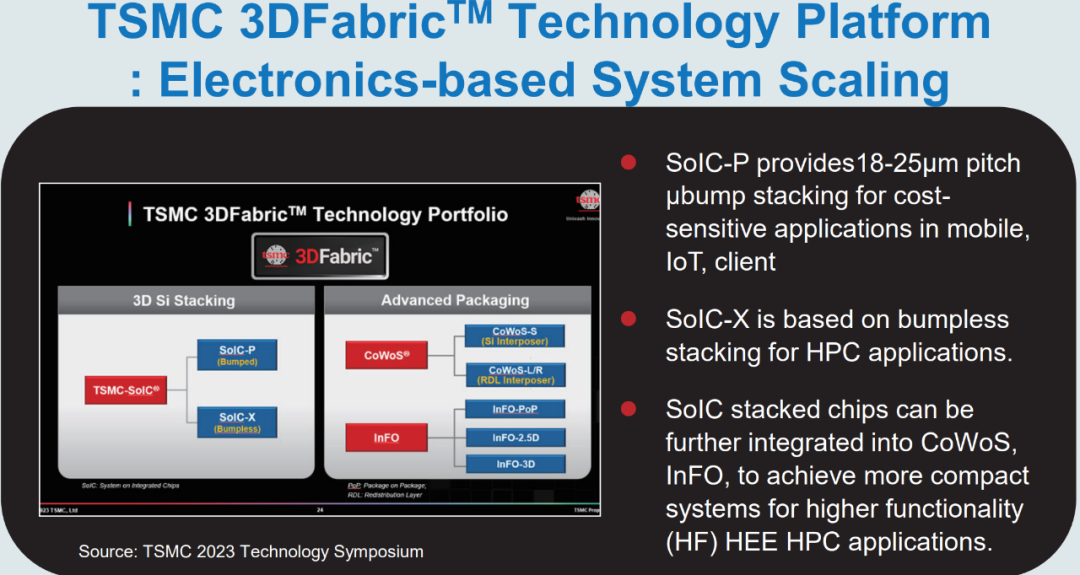

虽然 3DIC 带来了革命性的进步,但在三维空间扩展和集成越来越多芯片的能力却受到面积限制。这正是台积电公司创新的 3DFabric 技术平台发挥作用的地方,结合了 2.5D (CoWoS) 和 3DIC (SoIC) 集成方案的优点。

3DFabric 包含 CoWoS(Chip-on-Wafer-on-Substrate)、InFO(Integrated Fan-Out)、SoIC(System-on-Integrated-Chips)、CoW(Chip-on-Wafer)和 WoW(Wafer-on-Wafer)等晶圆级系统集成技术。通过利用现有基础设施并结合 2.5D 和 3DIC 功能,3DFabric 为 HPC/AI 工作负载实现了前所未有的计算密度、带宽密度和节能性能 (EEP)。

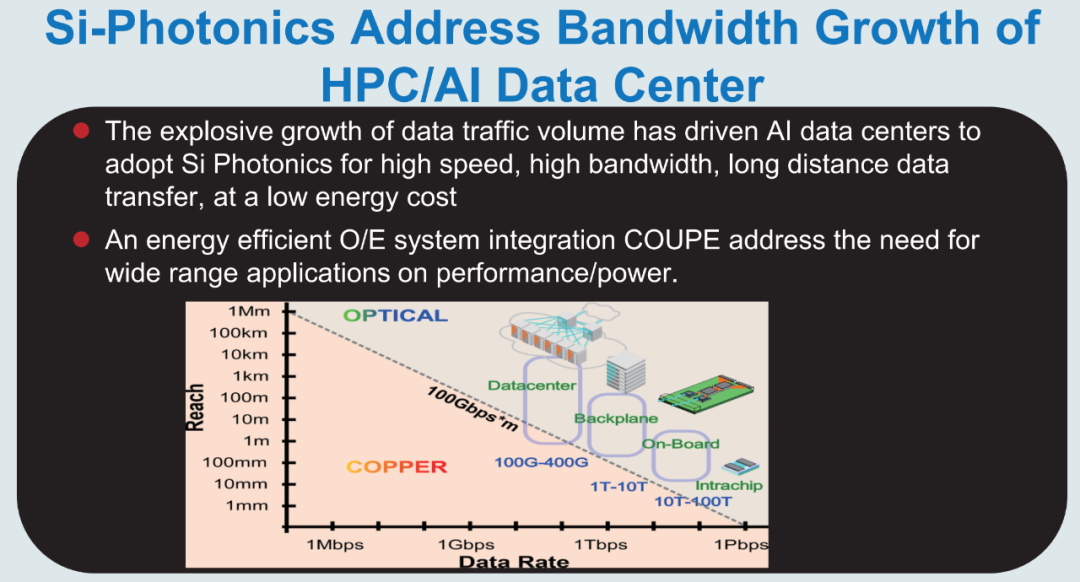

光电共封装(CPO)技术,促进数据中心带宽增长

虽然电气 I/O 扩展仍将继续,但人工智能数据中心数据流量的爆炸式增长正在推动硅光子技术的应用,以实现高速、高带宽、低能耗的长距离数据传输。如图所示,创新的芯片到芯片/芯片组和芯片到封装光/电 (OE) 集成平台(如 COUPE)正在兴起,以满足各种应用的带宽需求和性能/功耗要求。

生成式人工智能推动先进的节点和封装创新

最终,推动半导体创新的市场力量是生成式人工智能应用的无情需求,如大型语言模型和多模态模型。文本生成的模型参数超过 1750 亿个,多模态任务的模型参数超过 1.7 万亿个,计算复杂性和数据移动要求急剧上升。

这就需要采取多管齐下的方法,利用先进的逻辑节点扩展到 3 纳米及更高水平、先进的封装技术(如 2.5D 和 3DIC)、颠覆性的互连解决方案(电气和光学)以及革命性的热管理技术。只有通过这种横跨晶体管、存储器、互连、架构和系统集成的整体创新,半导体行业才有希望满足生成式人工智能时代对性能和效率的指数级需求。

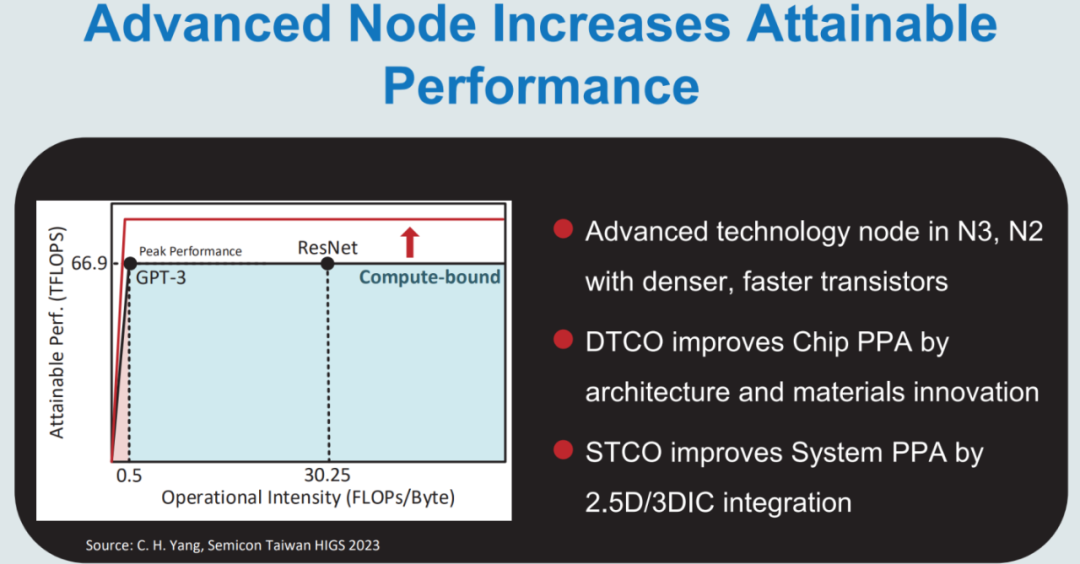

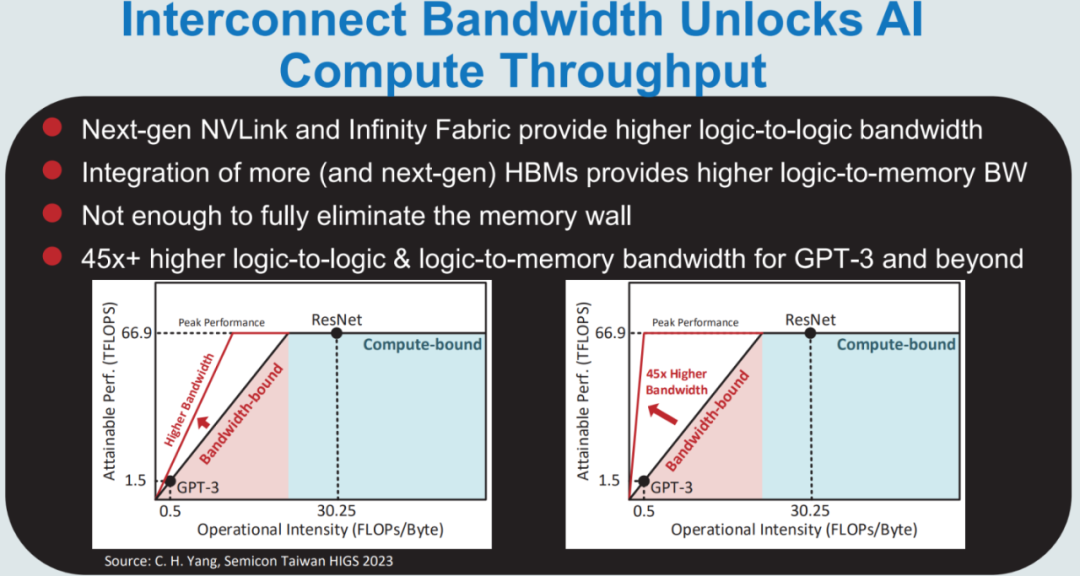

如图所示,将 N3 和 N2 等先进技术节点与更快、更密集晶体管的 DTCO 以及通过 2.5D/3DIC 集成实现的系统技术协同优化 (STCO) 相结合,对于释放 GPT-3 等复杂人工智能工作负载的全部可实现性能非常重要。通过新一代 NVLinks、Infinity Fabrics 和高 HBM 数量等创新技术,逻辑到逻辑和逻辑到内存的带宽提高了 45 倍,从而弥补了峰值性能和可实现性能之间的运行强度差距。

结论

由高性能计算和人工智能应用催化的半导体大趋势正在推动整个芯片封装系统堆栈的多维创新。先进的节点、存储器、2.5D 和 3DIC 封装、新的互连技术、材料和架构正在汇聚在一起,以克服计算、存储器和功耗方面的障碍。智能系统集成平台(如台积电的 3DFabric)是将系统扩展到未来,同时最大限度地提高性能、带宽、能效和外形紧凑性的关键推动因素。随着数据中心竞相支持人工智能的蓬勃发展,以及设备产生前所未有的数据量,半导体行业持续不懈的创新能力将在未来几年面临严峻考验。

扫码关注

扫码关注