运算放大器(简称:运放)在模拟电路设计中扮演着举足轻重的角色,其性能直接影响到整个电路系统的稳定性和准确性。但在使用过程中可能遇见相位延迟问题,如何针对这个问题解决?

1、运放为什么会产生相位延迟?

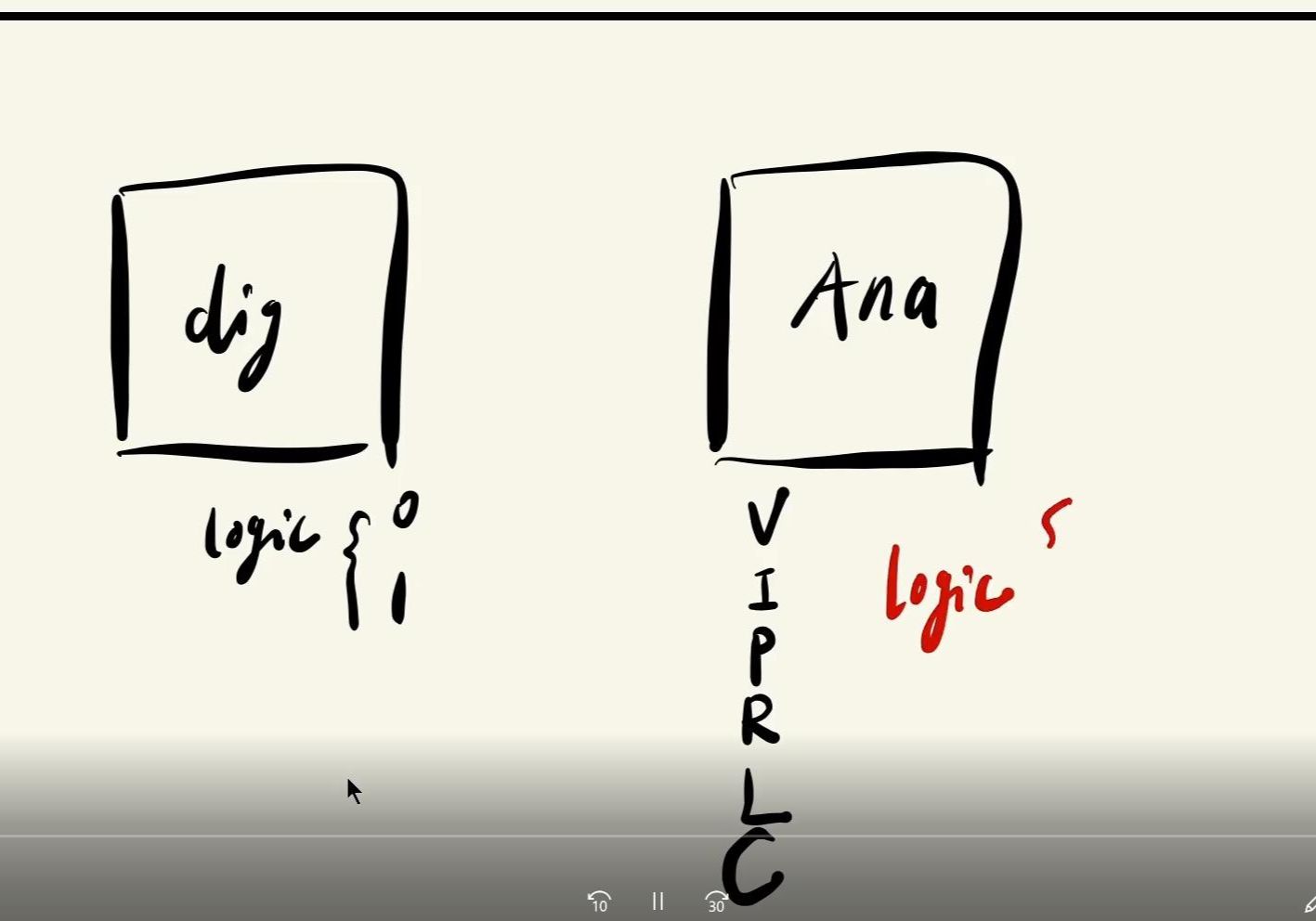

①内部电路结构

运放内部包含多级放大电路和反馈网络,这些电路元件在信号传输过程中会引入一定的时间延迟,导致相位延迟的产生。

②电容效应

运放的输入、输出端以及内部补偿电容都会对信号产生一定的延迟作用,特别是在高频信号下,这种延迟效果更加明显。

③反馈网络

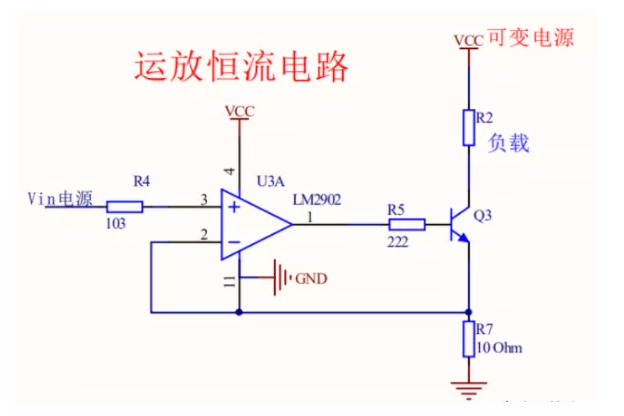

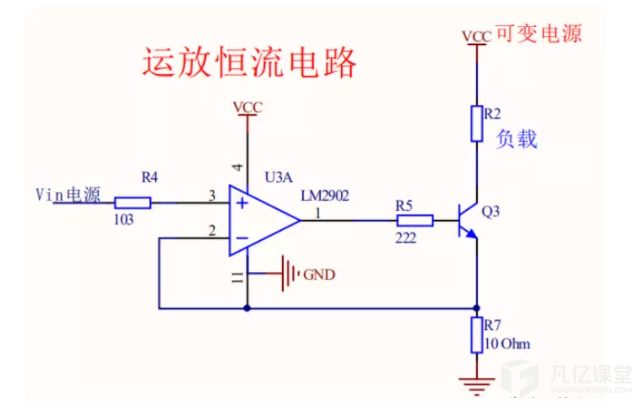

运放的反馈网络在调整增益和频率响应的同时,也会引入相位延迟。不合理的反馈网络设计会加剧相位延迟的问题。

2、相位延迟有什么危害?

①系统稳定性下降

相位延迟可能导致系统的相位裕度减小,从而降低系统的稳定性,使系统更容易出现振荡和不稳定现象。

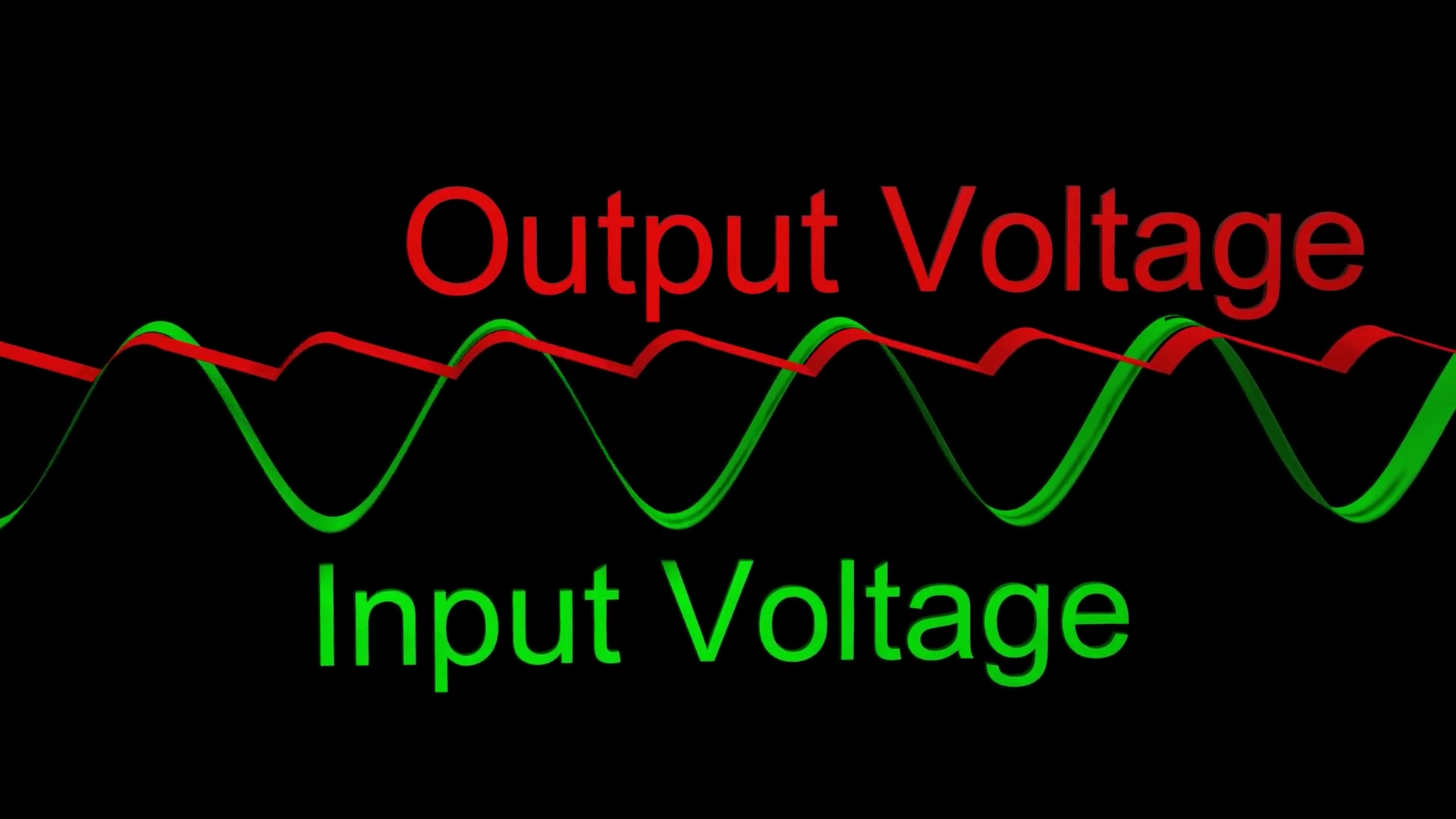

②信号失真

相位延迟会导致输出信号与输入信号之间的相位差增大,进而引起信号失真,影响系统的性能和精度。

③带宽受限

相位延迟会限制运放的带宽,使得运放在处理高频信号时性能下降。

3、如何解决运放的相位延迟问题?

①优化内部电路结构

通过改进运放内部电路的设计,减少信号传输路径上的延迟元件,从而降低相位延迟。

②调整电容效应

合理选择和调整运放的输入、输出电容以及内部补偿电容的数值,以减小电容效应对相位延迟的影响。

③使用高性能运放

选择具有更高增益带宽积(GBW)和更低相位延迟的运放,以提高系统的整体性能。

④采用差分放大技术

差分放大技术可以有效抵消共模干扰,提高系统的相位裕度,从而降低相位延迟的影响。

⑤优化反馈网络

设计合理的反馈网络,以平衡增益、频率响应和相位延迟之间的关系,实现最佳的系统性能。

本文凡亿企业培训原创文章,转载请注明来源!

扫码关注

扫码关注

![电子设计:数字滤波器分类及技术指标[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/65/de739e62290b3c228508ca5d1a65c9.png)