芯片的版图设计是个相当复杂的环节,需要用到很多工具及设计步骤,但很多人都不太熟悉芯片级版图设计,所以今天本文将讲讲这些,希望对小伙伴们有所帮助。

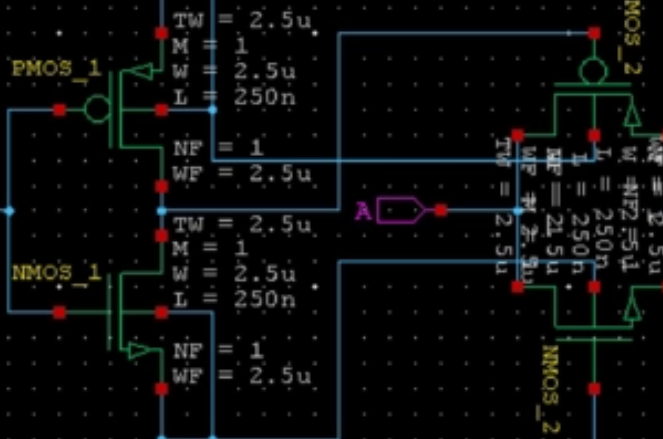

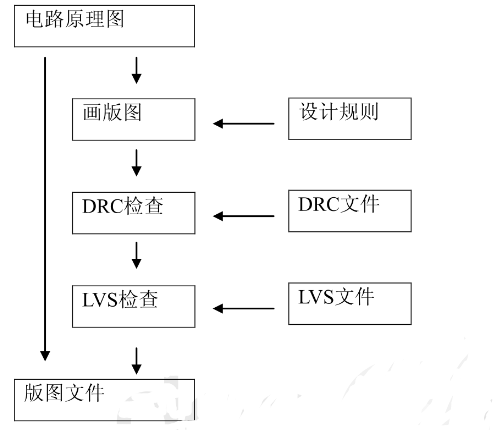

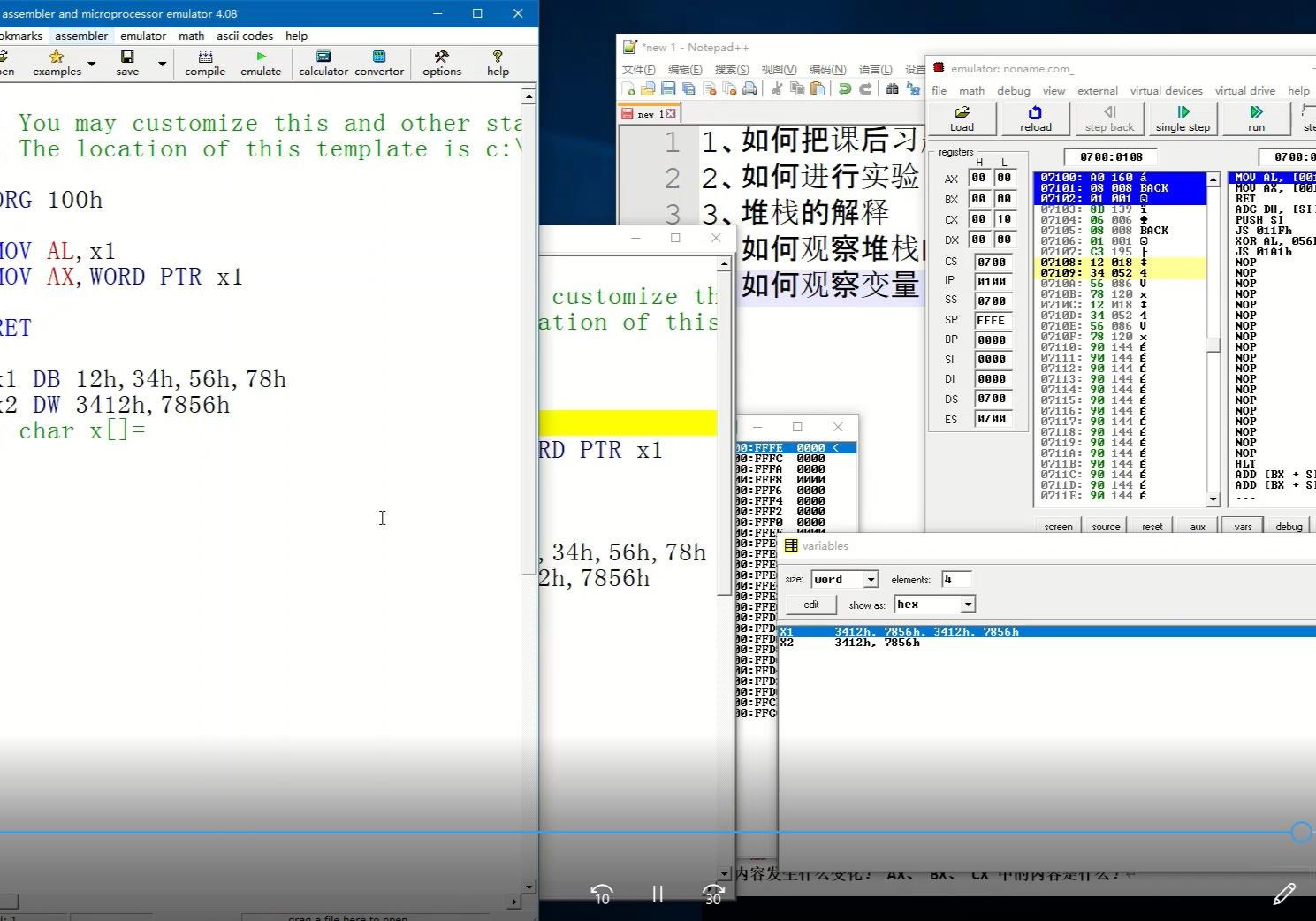

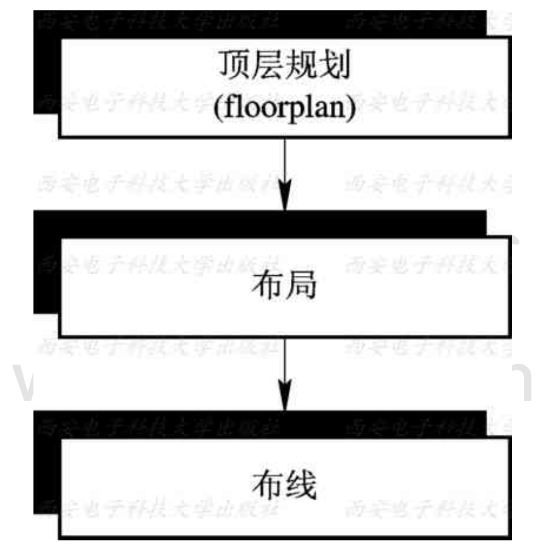

一般来说,芯片级的版图设计包括两部分内容:全定制电路的版图设计和自动布局布线的版图设计。其中,全定制方法适用于模拟电路和那些对性能面积要求较高的数字部分(例如CPU中的关键数据通路),而绝大多数数字设计采用自动布局布线的方法来生成版图。这两部分版图完成后,要在芯片级别整合在一起。如图所示,给出了自动布局布线(APR)的流程。

1、顶层设计

在实际的大型芯片设计中,往往很早就确定了芯片中各个块的位置。也就是说,芯片的顶层规划常常在进行电路/逻辑设计的时候就开始了。

在进行芯片顶层规划的时候,要考虑如下因素:

如何使芯片的面积尽可能地小;

各个宏( macros)/块( block)如何与PAD连接;﹒电源方案;

引脚(PIN)方案;

分析顶层的布线信息,通过合理地放置块,合理地定义区域及分组,使得连线的复杂性不会过高。

2、布局布线

完成芯片顶层规划之后,接下来进行布局布线。通常,这一阶段可分为四个步骤:

(1)布局;

(2)扫描链的优化。PR工具重新对扫描链中的单元排序,以便降低布线的复杂性;

(3)时钟树的综合及布线。由于时钟是设计中最为重要的信号线,因此在布线时要首先布时钟线。在通常的PR工具中,通常将时钟树的生成、时钟的布线作为一个单独的步骤,称为时钟树综合;

(4)布线。

扫码关注

扫码关注