随着高速数字信号处理器(DSP)和外设的出现,工程师开始面临着日益严重的电磁干扰(EMI)问题,其中以噪声和热量问题最为严重,PCB板设计要求愈发严格,工程师必须采用自身技术来减少这些干扰所带来的的伤害,其中板级降噪技术应用越来越广,所以今天讲讲它!

首先板级降噪技术包括板结构、线路安排和滤波,具体做法如下:

1、采用地和电源平板;

2、平板面积要大,以便为电源去耦提供低阻抗;

3、使表面导体最少;

4、采用窄线条(4-8mil)以增加高频阻尼和降低电容耦合;

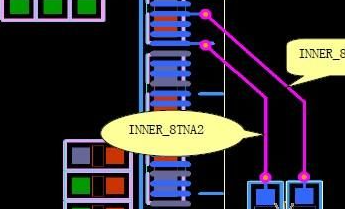

5、分开数字、模拟、接收器、发送器地/电源线;

6、根据频率和类型分割PCB上的电路;

7、不要切痕PCB,切痕附近的线迹有可能导致不希望的环路;

8、采用多层板密封电源和地板层之间的线迹;

9、避免大的开环板层结构;

10、PCB连接器接机壳地,这为防止电路边界处的辐射提供屏蔽;

11、采用多点接地使高频低阻抗低;

12、保持地引脚短于波长的1/20,以防止辐射和保证低阻抗线路安排降噪技术包括用45,而不是90,线迹转向90,转向会增加电容并导致传输线特性阻抗变化;

13、保持相邻激励线迹之间的间距大于线迹的宽度以使串扰最小;

14、时钟信号环路面积应尽量小;

15、高速线路和时钟信号线要短和直接连接;

16、敏感的线迹不要与传输高电流快速开关转换信号的线迹并行;

17、不要有浮空数字输入,以防止不必要的开关转换和噪声产生;

18、相应的电源、地、信号和回路线迹要平行以消除噪声;

19、保持时钟线、总线和片使能与输入/输出线和连接器分隔;

20、路线时钟信号正交I/O信号;

21、为使串扰最小,线迹用指教交叉和散置地线;

22、保护关键线迹(用4-8mil线迹以使电感最小,路线紧靠地板层,板层之间夹层结构,保护夹层的每一边都有地)。

扫码关注

扫码关注

![电子设计:数字滤波器分类及技术指标[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/65/de739e62290b3c228508ca5d1a65c9.png)