- 全部

- 默认排序

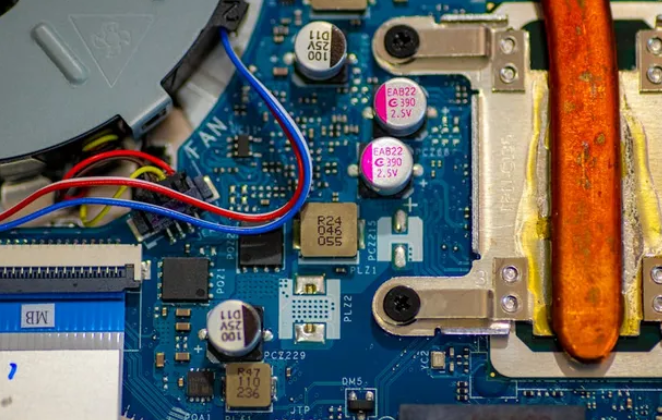

由于文章篇幅限制,将此文分为上下两篇,欲看上篇可点击《不同产品系统如何进行EMC设计?(上)》,接下来将更新下篇,希望对小伙伴们有所帮助。3、电源与接地、高速信号线路及内部线缆的EMC设计PCB的EMC设计中也提到过供电与接地、高速信号线路

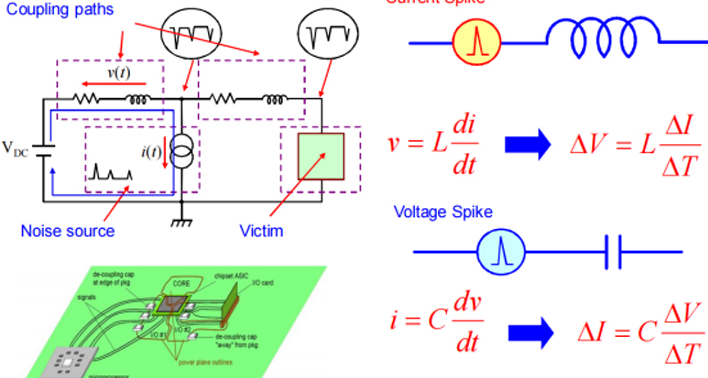

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

电磁兼容性(EMC)、热量、干扰等是电子设计中最为常见的设计问题,其中电磁兼容性问题最为麻烦,无法消除,电子工程师只能通过PCB布局布线来降低EMC问题,但你知道,在PCB设计中,有哪些电磁兼容性问题吗?1、电磁辐射电路中的高速信号线、射频

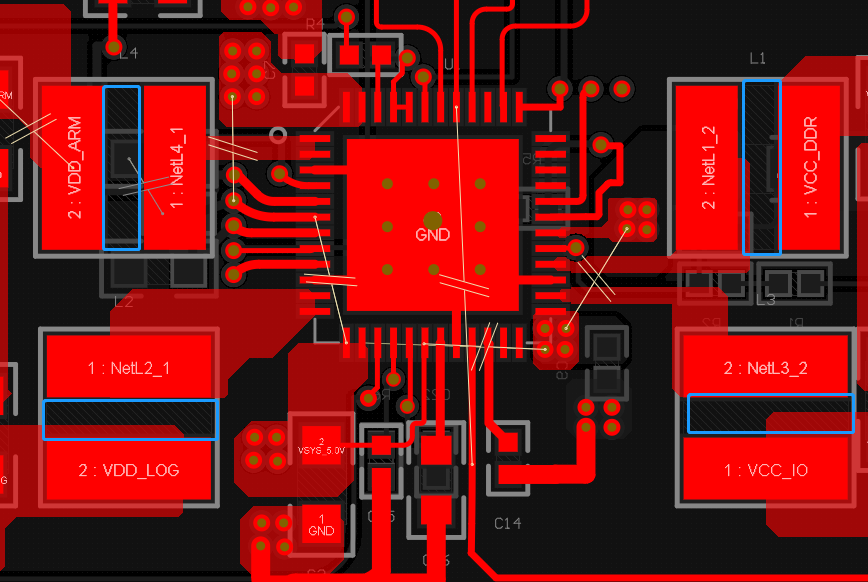

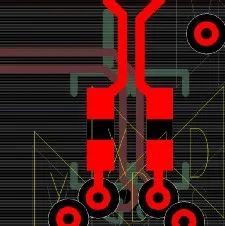

电感所在层的内部需要挖空处理2.反馈需要走一根10mil的线3.铺铜尽量包住焊盘,避免出现开路现象4.注意此处是否满足载流,后期自己加宽一下铜皮宽度5.走线尽量走直线,不要有直角,高速信号线才会用到圆弧走线6.电感下面尽量不要放置器件7.电

在教科书或原厂的PCB Design Guide里经常会看到一些关于高频高速信号的PCB设计原则,其中之一是尽量避免在PCB板边缘走高速信号线,但如果我依然要走这个线,我应该注意哪些方面?下面一起来看看吧!1、信号线的长度高频信号的传输速度

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

【摘要】在某单板开发工作中,高速信号线非常多,为了保证单板的EMI性能,在PCB布线中,尽可能保证信号线走内部信号层,防止因为过多表层高速信号线产生的EMC问题无法定位。但是该方案带来的直接问题是高速信号线跃层过多,过孔较多,极大的增加了信号线的插入损耗,影响了信号完整性。在本单板设计中,为了兼顾性

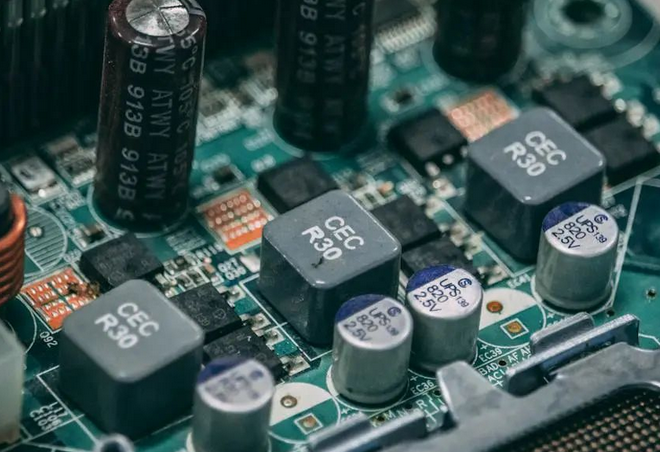

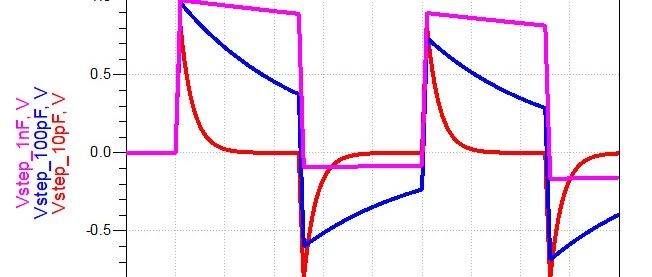

我们经常见到信号中串有耦合电容,如下结构。AC耦合电容的作用有:隔离直流分量;允许电容两端使用不同level的电压值;防止热插拔时的瞬态电流;协议要求,检测对端用;等等...这些不是我们的重点,下面我们来直观的看一下,信号通过电容后的影响;对于一个没有AC耦合电容的100MHz信号波形如下: 此

在高速PCB设计中,信号层的空白区域可以覆铜,但这仅限于单个信号层,如果遇见多个信号层的覆铜,该如何分配?今天本文将针对这个问题进行探讨,希望对小伙伴们有所帮助。1、主要信号层覆铜接地大部分信号层的空白区域优先接地。确保敷铜与高速信号线保持

今天遇到了这个问题,领导让我改成135°线,说这样不行电路板好看很重要吗,没谁天天盯着电路板瞅吧他给我的回复不是好不好看是他觉得有问题刚我搜的因为我认为直接走线会比45更好因为我要辞职了,然后我回复他我说我记得之前培训(或者还是那个技术文章)任意走线会比45好一些,弯越多信号反射越大,所以我现在布线

扫码关注

扫码关注